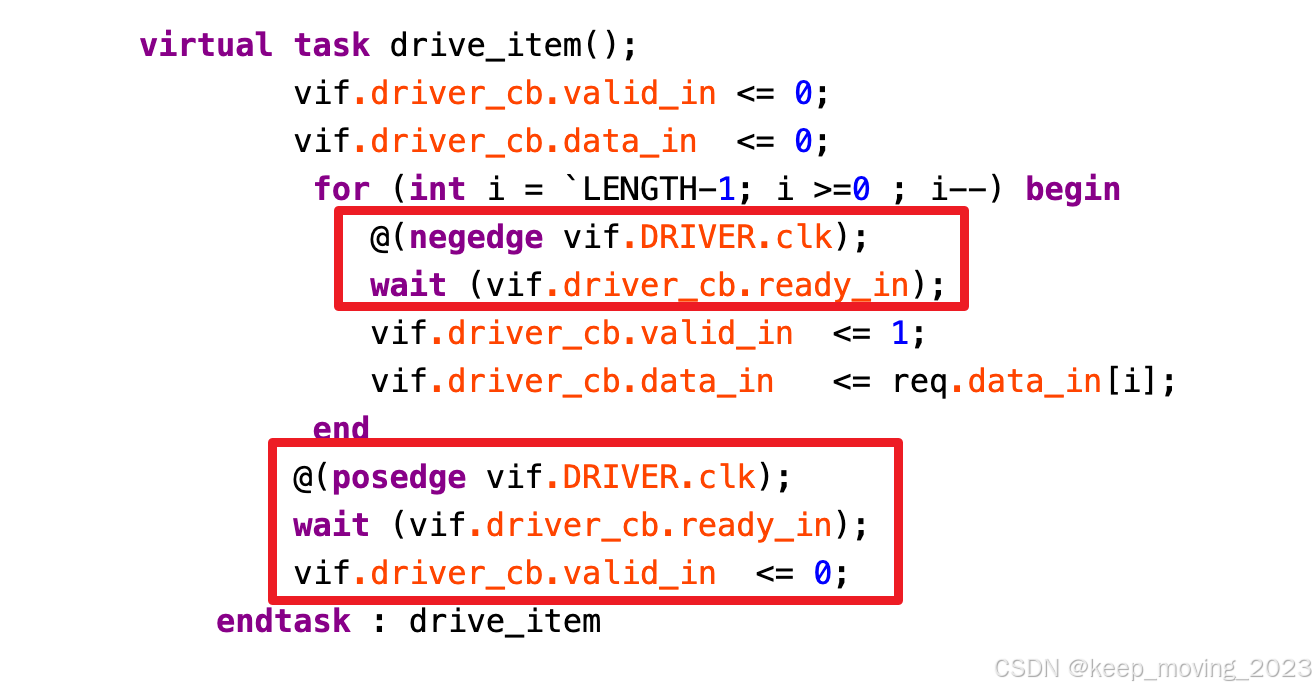

vld和rdy握手类型的驱动

背景:驱动收到rdy才能发起驱动,否则保持。

实践示例:

这样可以实现背对背发包,需要注意的地方就是,如果是最后一个包,DUT rdy一直拉高,TB这里发完最后一个包,要接口的vld信号置为无效。否则vld&rdy都会一直为高,输入大量非预期的包。所以需要在发完一个item后,再去初始化一下接口。

task drv();

dut.data <= Tb.data;

do begin

@clk ;

end while(rdy !== 1);

endtask

task run_phase();

supper.phase;

forever begin

init_if();

....;//get item

drv();

end

这里用了wait,可能会潜在风险;之前遇到过wait会get到毛刺导致环境认为已经达到wait条件,就是不知道这个下降沿能不能规避这个问题;

vld=0时,对其他信号随机驱动为0/1/rand/x等

run phase调用

get_stim任务

task get_stim()

SEQ_TR tr;

forever begins

seq_item_port.try_next_item(tr);

if(tr == null) driver_idle();

else begin

driver_pkt();

seq_item_port.item_done(tr);

end

endtask

task driver_idle();

vif.data <= 0;

vif.data <= '1;

vif.data <= 'x;

vif.data <= $urandom_range(1,9999);

@(posedge vif.clk)

endtask

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?