项目背景:在以FPGA做项目时尤其是图像、视频类项目时,对存储器的使用可谓是必不可少,其中作为高速缓存的动态存储器例如SDRAM、HyperRam、DDR3、DDR4等。这些易失性存储器使用的频率是最高的,但同时有些非易失性存储器也常常会使用到,一般对于存储参数类的小容量存储器会使用eeprom(iic接口)、flash(spi)接口等。但是如果要用大容量的而且对读写速率还有一定要求的应用场景呢??根据以往的项目经验在这个场合下会使用EMMC、SD卡等存储器。

本文就着重介绍下FPGA基于SDIO-4线模式实现 UHS-1 的协议来读写SD卡,向下兼容SD2.0协议。实现读写速率约600Mb/s.本文主要介绍FPGA在不使用文件系统的方式对SD卡进行基于物理地址的读写。网上基于SD2.0的协议介绍也比较多,在此就不太详细的介绍协议细节,主要介绍FPGA读写SD卡需要的具体内容 。

1、SD卡的类型

常见的SD卡按类型分为

标准容量卡(<=2GB): 存储地址的单位是以字节为单位

高容量卡 (>2GB <=32GB) 存储地址的单位是块(512Byte)为单位

2、SD的初始化

系统上电,发送 74 个时钟,等待 sd 卡内部初始化

发送 cmd0,复位 sd 卡

发送 cmd8,如果 sd 卡有响应,则 sd 卡属于 sdhc 类型,并且工作电压正常,初始化工程。如 果 sd 卡无响应,则 sd 卡可能属于 sdsc 类型,或者工作电压不正常,或者当前卡不属于 sd 卡,初始化失败。

发送 cmd55 和 acmd41

发送 cmd2,获取 sd 卡的 CID 序列。

发送 cmd3,获取 sd 卡的 RCA 地址。

发送 cmd7,选中 sd 卡。

发送 cmd55+acmd6,设置总线宽度。

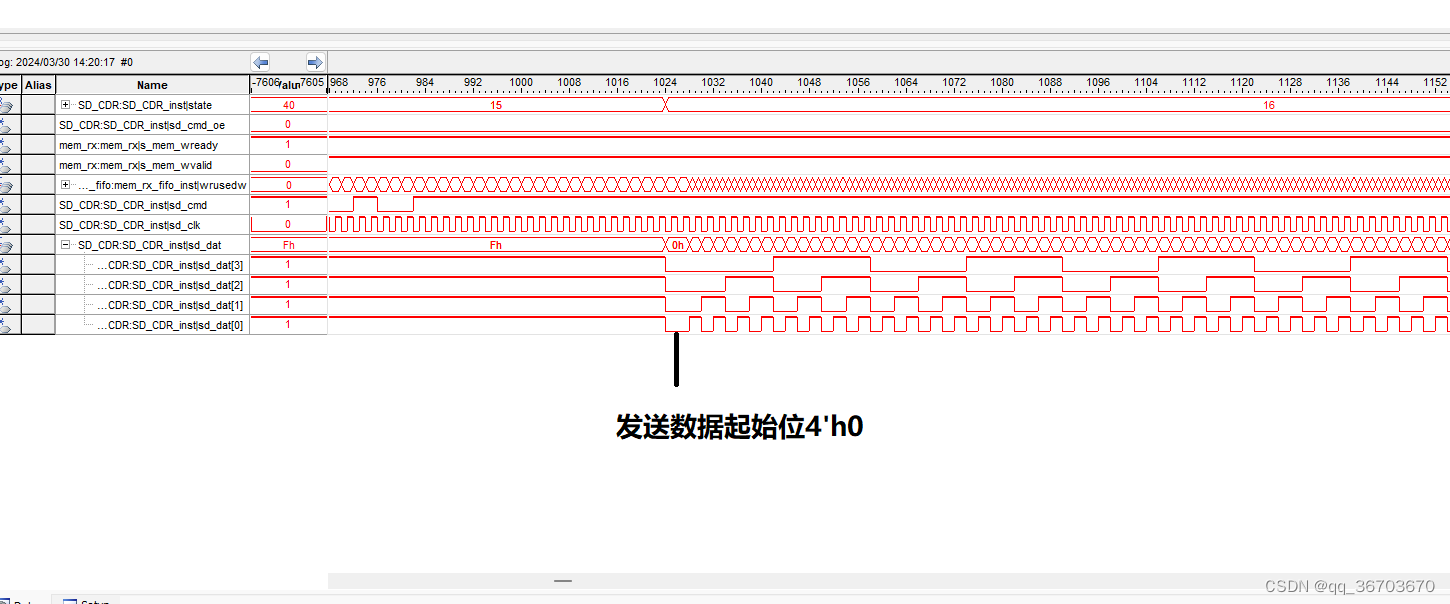

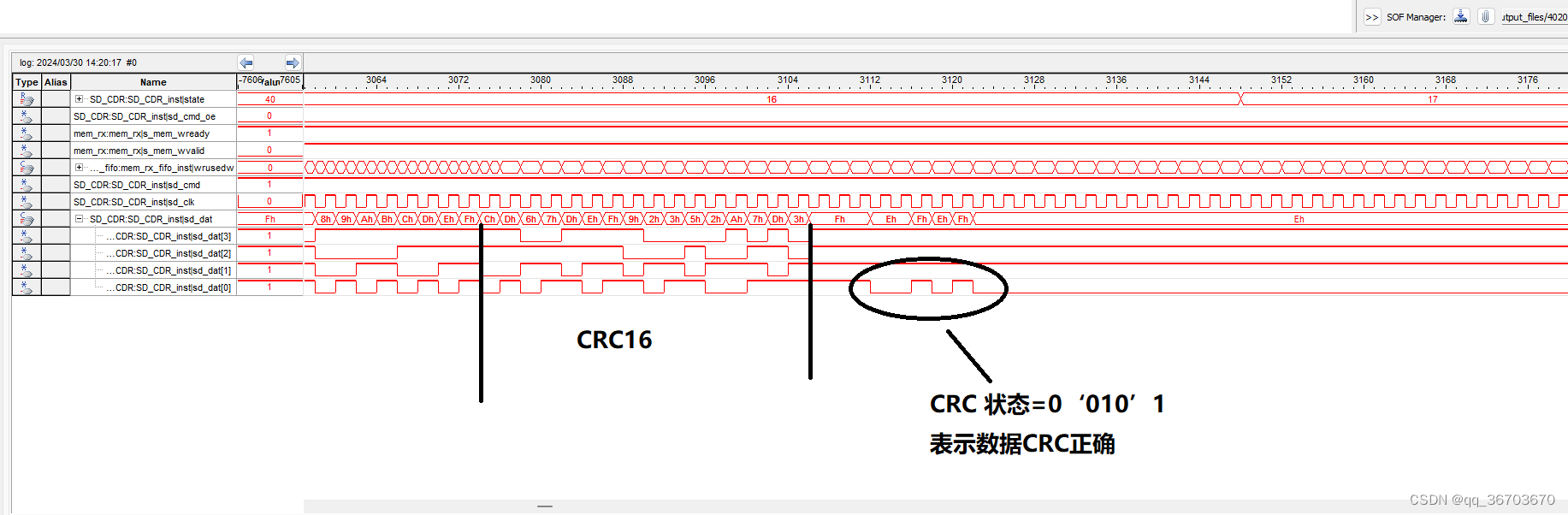

3、SD的写数据

发送 cmd16 复位设置块的大小

发送 cmd55+acmd23 预擦除

发送 cmd25 连续写的命令

发送数据(N*block_num)

发送 cmd12 制停止数据传输,数据写结束

发送 cmd13 查询卡是否恢复ready状态

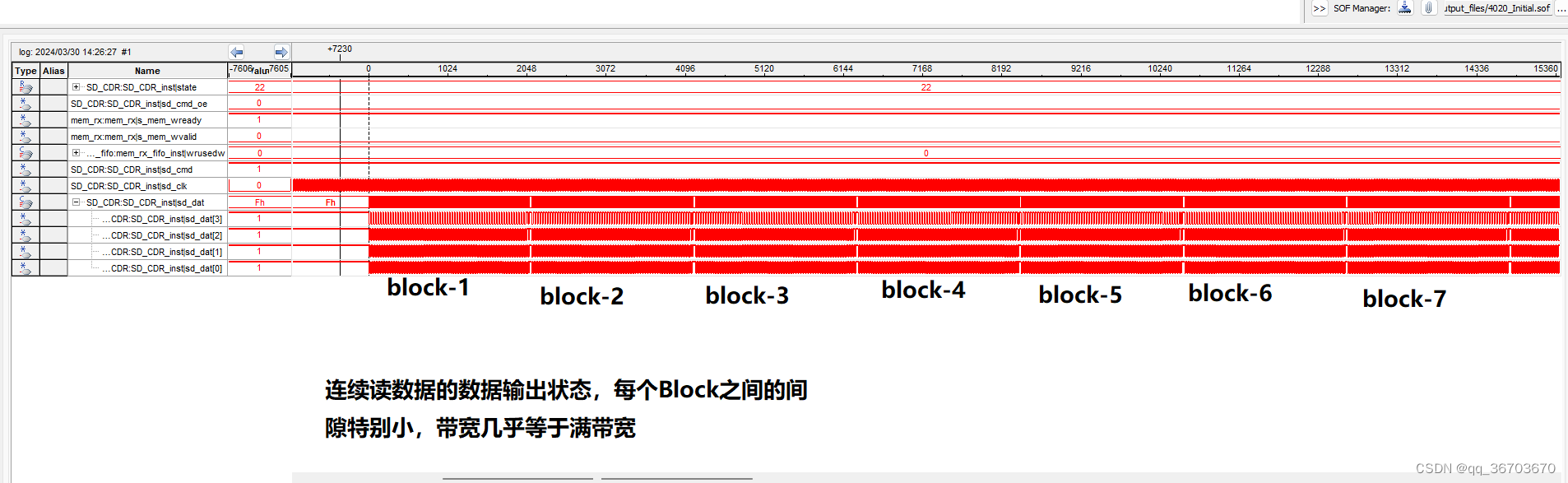

4、SD的读数据

发送 cmd16 复位设置块的大小

发送 cmd18 连续读的命令

发送 cmd12 强制停止数据传输,数据写结束

5、时序波形

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?