网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

尽管 SD NAND和 TF卡之间有着这么大的区别,但具体到实际应用,其对外接口和驱动程序都是一样了,这说明可移植性非常好。

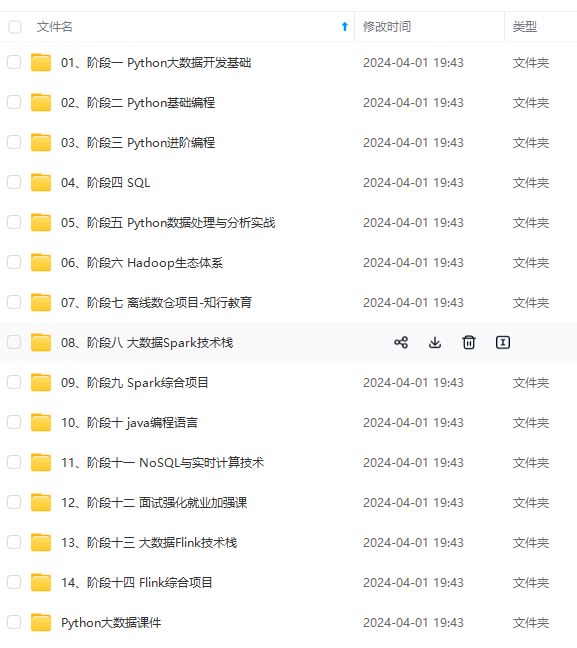

① 物理结构

SD NAND从物理结构看包括 5 个部分,分别为存储单元、存储单元接口、电源检测、卡及接口控制器和对外接口,具体见下图。

- 存储单元是存储数据部件,存储单元通过存储单元接口与卡控制单元进行数据传输

- 存储单元接口是接口控制器与存储单元的数据交互通道

- 电源检测单元保证 SD NAND工作在合适的电压下,如出现掉电或上电状态时,它会使控制单元和存储单元接口复位

- 卡及接口控制单元控制 SDNAND的运行状态,它包括 8 个寄存器

- 对外接口单元控制 SD NAND引脚的输入输出,一般包含SDIO接口和SPI接口

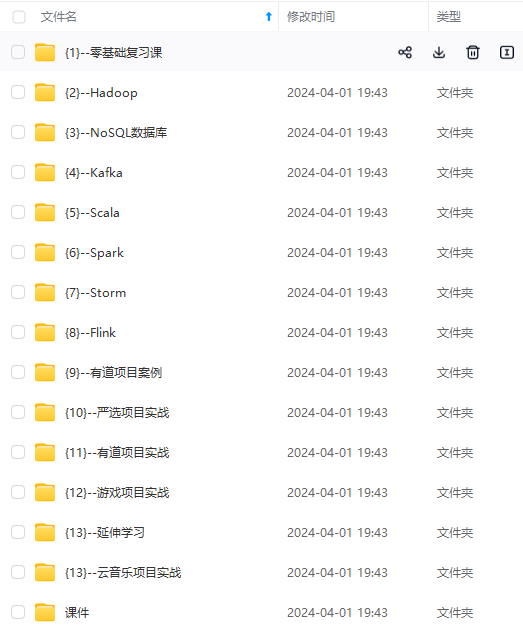

② 对外接口

SD NAND共有 9 个引脚,其中包括 3 根电源线、1 根时钟线、1 根命令线和 4根数据线。如下:

- CLK:同步时钟线,由主机产生,即由主控制器(FPGA)输出; 使用 SPI 模式 时,该引脚与 SPI 总线的 SCK 时钟信号相连

- CMD:命令控制线, SDIO 主机通过该线发送命令控制 SD NAND,如果命令要求 SD NAND 提供应答(响应), SD NAND也是通过该线传输应答信息; 使用 SPI 模式时,该引脚与 SPI总线的 MOSI 信号相连, SPI 主机通过它向 SD NAND发送命令及数据,但因为 SPI 总线 的 MOSI 仅用于主机向从机输出信号,所以 SD NAND返回应答信息时不使用该信号线;

- DAT0-3:在 SDIO 模式下,它们均为数据线,传输读写数据, SD NAND可将 D0 拉低表 示忙状态; 在 SPI 模式下, DAT0 与 SPI 总线的 MISO 信号相连, SD NAND通过该信号线向主机发送数据或响应, DAT3 与总线的 CS 信号相连, SPI 主机通过该信号线选择要通讯的 SD NAND。

- VDD、VSS1、VSS2:电源和地信号。

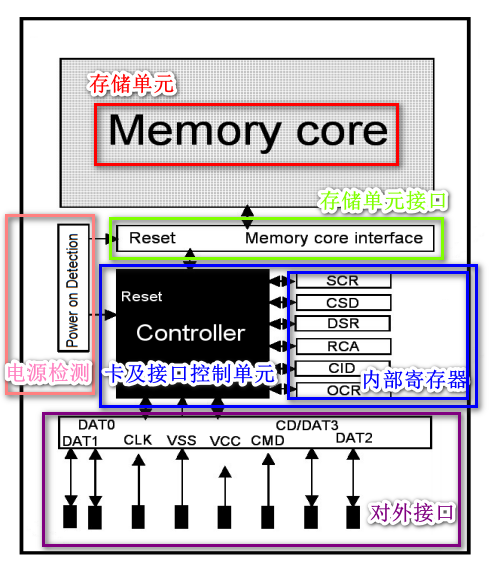

③ 工作模式

SD NAND有两种工作模式:SDIO 模式与SPI模式

在 SDIO 模式下,SD NAND共使用到 CLK、CMD、DAT[3:0] 6根信号线;SDIO 总线与多个 SD NAND连接时,可以共用 CLK 时钟信号线,对于 CMD、DAT[3:0]信号线,每个 SD NAND都要独立连接。SDIO 总线与 SD 卡连接方式,具体见下图。此模式使用IO引脚多,但传输速度高。

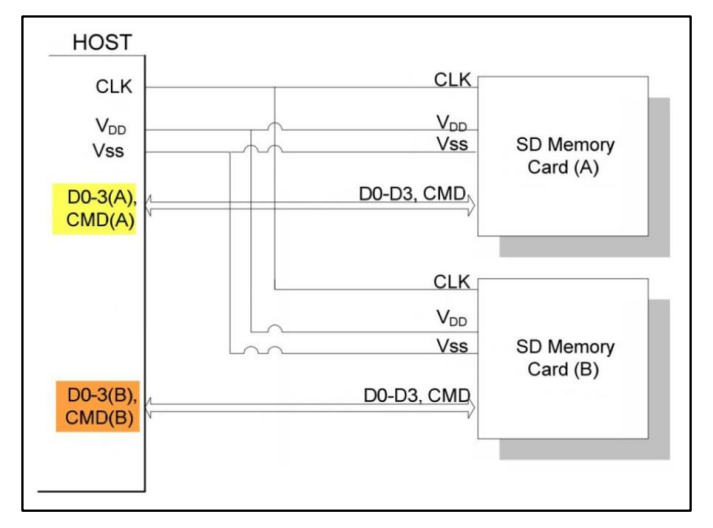

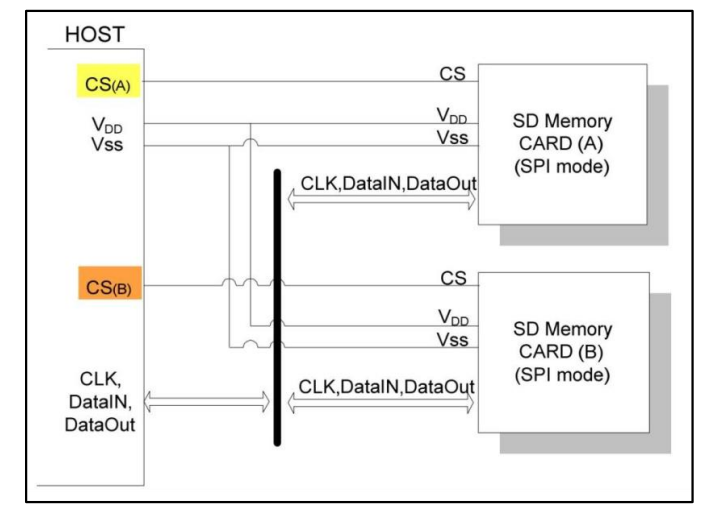

在 SPI 模式下,SD NAND共使用到 CS(DAT[3])、CLK、MISO(DAT[0])、MOSI(CMD) 4根信号线;SPI 总线与多个 SD NAND连接时,除 CS 片选信号线不可共用外,其他信号均可公用。SPI 总线与 SD NAND连方式,具体见下图。此模式使用IO引脚少,但传输速度慢。

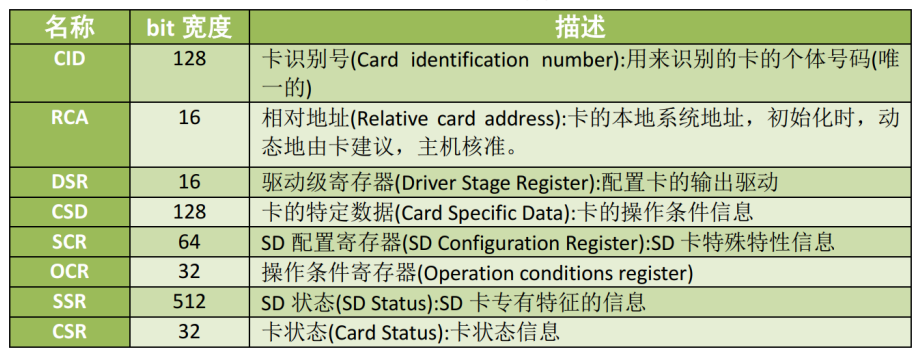

④ 内部寄存器

SD NAND总共有 8 个寄存器,用于设定或表示 SD NAND信息,寄存器描述具体见下图。 这些寄存器只能通过对应的命令访问,对 SD NAND的控制操作是通过命令来执行的, SD NAND定义了 64 个命令(部分命令不支持 SPI 模式) ,每个命令都有特殊意义,可以实现某一特定功能, SD NAND接收到命令后,根据命令要求对 SD NAND内部寄存器进行修改,程序控制中只需要发送组合命令就可以实现 SD NAND的控制以及读写操作。

内部寄存器就不展开讲了,我们用FPGA实现读写测试也不需要了解那么多寄存器。

5、SD NAND的控制时序

① 命令与读写时序

SD NAND的通信是基于命令和数据传输的。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1383

1383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?