第13章 开关电容式功率变换器拓扑结构概述与性能比较

13.1 引言

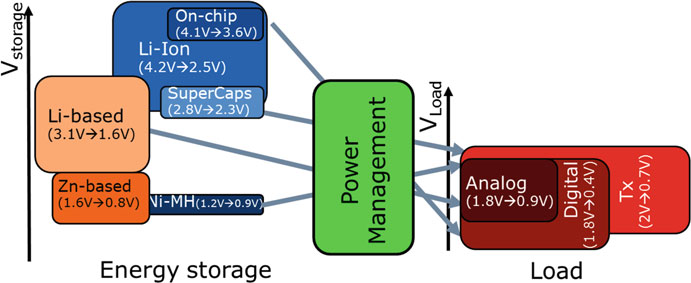

在现代社会中,以数据为中心的电子设备的使用已变得无处不在。由于消费者希望能够在任何地方使用这些设备,因此出现了大量电池供电设备,包括笔记本电脑、智能手机、智能手表以及其他所谓的可穿戴电子设备。根据使用需求,这些设备中的能量存储可以采用多种不同的电池化学体系,其中使用一次电池(不可充电)或二次电池(可充电)。在许多情况下,由于锂离子电池具有更高的能量密度,因而被广泛采用。根据用于能量存储的电池化学体系不同,电子设备的输入电压范围相对较宽。同时,电子设备内部供电以及连接外部接口需要产生多种不同的负载电压,这些电压需从输入电压派生出来[1]。在电子设备中,输入电压范围与所需负载电压之间的差距可通过图13.1[2]所示的电源管理模块来弥补。从图中可以看出,可能需要升压和降压转换来弥合电压差距。

电源管理模块中的电压转换,如图13.1所示,可通过三种不同方式实现,即采用连续时间电压调节器、电感式或开关电容功率变换器(SCPC)[3]。

在连续时间电压调节器中,耗散型通路器件仅能实现从输入电压Vin降至较低输出电压Vout的降压转换,其最大效率为Vout/Vin。尽管这类调节器具有良好的电磁干扰(EMI)特性,但在Vout远低于Vin的情况下,其低效率可能成为问题,尤其是在高功率水平时。使用

用于临时能量存储的无功元件可实现升压和降压直流/直流转换,并具有更高的效率。如果主要的无功能量存储元件是电感器,则可通过两个功率开关和一个电感器实现电感式直流/直流转换器。根据开关和电感器的连接方式,可以构成降压、升压或反相升降压直流/直流转换器[4]。输入电压与输出电压之间的比率由功率开关的工作占空比控制。如果主要的无功能量存储元件是电容器,则可以通过一组功率开关和一个或多个所谓的浮置电容实现开关电容功率转换器。正如本文将详细讨论的,这些开关和电容器的连接拓扑结构决定了输入电压与输出电压之间的比率。通过控制转换器的输出阻抗,可在输出电流和/或输入电压变化时维持固定的输出电压。

除了通过提高电池的能量密度和电压转换效率来延长电池供电电子设备的运行时间外,降低负载的功耗也非常重要。对于数字负载而言,在保持性能的同时提高功率效率,推动了细粒度电源管理方案的发展,例如根据连接模块的活动状态调节数字供电电压[5]。这种对本地供电电压生成的需求,促进了与负载集成的直流/直流转换器的发展[1, 3]。

存在多种方法可将电感器与电感式直流/直流转换器[1, 3]集成。首先,电感器可以与转换器的功率开关、转换器控制模块和负载集成在同一芯片上,既可以作为空芯电感器[6, 7],也可以作为带有磁芯的后处理薄膜电感器,例如基于CoZrTa合金[8]的电感器。或者,电感器可以集成在封装中的其他位置,例如使用键合线[9]或封装走线空芯电感器[10],或将电感器实现于一个单独的无源集成芯片上,并与有源CMOS芯片共同封装[11]。在所有情况下,集成电感转换器用于相对较高的输出功率,即超过100毫瓦[3],因为其效率性能在

与集成电容对应器件相比,当在更小面积上实现较低输出功率时,集成电感式直流/直流转换器的性能会下降[12]。这使得开关电容功率转换器在低于100毫瓦的功率范围内成为单片集成的有利候选方案;即使使用外部贴片电容来实现更高输出功率,其功率密度相较于带外部电感的电感式DC/DC转换器仍具有竞争力[13]。

对于开关电容功率转换器(SCPCs),存在多种单片电容集成方案,例如利用MOS场效应晶体管(MOSTs)的栅极电容(MOSCAPs)、使用边缘电容中的金属间电容(通常放置在MOSCAPs上方),或在可用时采用金属‐绝缘体‐金属(MIM)电容[1, 3]。当使用沟槽电容等非标准电容实现方式时,可获得更高的功率密度[14]。除了纯电感式或开关电容式直流/直流转换器外,还出现了中间方案。一方面,在集成电感转换器中加入浮置电容,以在开关节点处产生多个电压电平[15, 16],从而降低电感器中的纹波电流和开关中的阻断电压,进而提高效率。另一方面,在集成电容转换器中加入电感器,以减少与电容充放电相关的损耗[17]。

本文讨论了开关电容功率转换器(SCPC)中实现所需电压转换比的基本方法,以及由此产生的不同拓扑结构在性能上的比较。第13.2节介绍了开关电容功率转换的基本理论背景。第13.3节和第13.4节描述了双时钟相位和多时钟相位拓扑示例及其综合方法。第13.3节和第13.4节中的各种拓扑结构的性能比较在第13.5节中进行。最后,第13.6节给出了结论。

13.2 开关电容式功率变换器的理论考虑

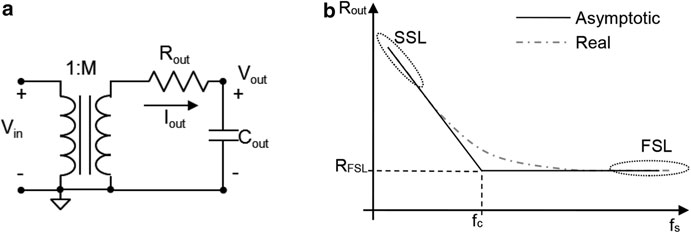

开关电容功率转换器(SCPC)的基本模型如图13.2a[3]所示。一个理想直流变压器将输入电压Vin乘以电压转换比M。正如将在第13.3和13.4节中更详细描述的那样,该电压转换比M取决于所采用的电路拓扑结构,即电容器在转换器不同时钟相位期间的连接方式。转换器的平均等效输出阻抗由Rout建模。如图13.2b所示,Rout在开关频率fs[18]的低值和高值情况下均表现出渐近行为。在fs较低时,其渐近线为慢速开关极限(SSL),而在fs较高时,其渐近线由快速开关极限(FSL)定义。在慢速开关极限(SSL)下,流入电容器的电流为脉冲式,并在每个时钟相位结束时降为零,此时Rout依赖于fs以及所使用的浮置电容;在快速开关极限(FSL)下,电容器两端的电压在导通阶段保持不变,Rout则取决于浮置电容器充放电路径中的电阻,主要由导通电阻决定。

开关电容功率转换器的平均模型,(b) 等效输出阻抗 Rout 与开关频率 fs 的函数关系)

开关电容功率转换器的平均模型,(b) 等效输出阻抗 Rout 与开关频率 fs 的函数关系)

功率开关。渐近线在转折频率f c处相交。现在,Rout的整体曲线可以近似为:

$$

R_{out} = \frac{q}{R^2_{SSL}}

$$

(13.1)

从图13.2a可以看出,开关电容功率转换器的最大可能效率等于Vout/MVin。然而,由于平均模型未考虑转换器的开关特性,实际上由于开关损耗的存在,所达到的效率将更低。这些损耗是由充电和放电转换器中每个浮置电容极板相关的寄生电容(也称为底板损耗)以及驱动功率开关通断所产生的驱动损耗引起的。除了开关损耗外,还会产生导通损耗,其值为(MVin − Vout)Iout,如图13.2a所示。

为了在Vin或Vout或两者变化范围较大时保持相对较高的效率,需要使用多个M值。在多变比开关电容功率转换器中,这些多个M值可以通过单个电路[3]生成。文献[13]给出了一个最近的实例,使用八个M值,在以锂离子电池作为输入源的全范围内维持超过90%的效率。在任何开关模式功率转换器设计中的另一个重要方面是输出电压纹波。与电感式直流/直流转换器类似,交错并联也可应用于开关电容功率转换器中以降低输出电压纹波[3, 19]。

这可以通过将一个在时间点Ts = 1/fs间隔向输出端输送电荷包Q的大转换器,拆分为N个相同的并联转换器或模块来实现,每个模块依次在时间点Ts/N间隔向输出端输送电荷包Q/N。对于集成转换器而言,将转换器拆分为并联模块并非问题。若需调整转换器以适应更高或更低的输出功率,只需增加或减少并联的模块数量即可。最后,对输出电压Vout的控制涉及选择正确的M值(若使用多变比转换器),通常通过查找表以开环方式实现,并在闭环控制中调制Rout的值[3]。对Rout的调制主要通过

表13.1 所有可能的转换比M与浮置电容数量的关系

| # 浮置电容器 | 可能的转换比M |

|---|---|

| 1 | 1/2, 1, 2 |

| 2 | 1/3, 1/2, 2/3, 1, 3/2, 2, 3 |

| 3 | 1/4, 1/3, 2/5, 1/2, 3/5, 2/3, 3/4, 4/5, 1, 5/4, 4/3, 3/2, 5/3, 2, 5/2, 3, 4 |

| 4 | 1/7, 1/6, 1/5, 1/4, 2/7, 1/3, 3/8, 2/5, 3/7, 1/2, 4/7, 3/5, 5/8, 2/3, 5/7, 3/4, 4/5, 5/6, 6/7, 7/8, 1, 8/7, 7/6, 6/5, 5/4, 4/3, 7/5, 3/2, 8/5, 5/3, 7/4, 2, 7/3, 5/2, 8/3, 3, 7/2, 4, 5, 6, 7, 8 |

通过改变稳态损耗中的浮动静电容(在SSL中),或调节功率开关的导通电阻或占空比(在FSL中)来实现,而不仅仅是在SSL中改变f s。

对于给定数量的浮置电容,所有可实现的M值均可基于斐波那契数列[3, 20]计算得出。这在表13.1[3]中进行了说明。

尽管表13.1展示了哪些M值可以实现,但迄今为止尚未系统化地解决每个值的综合方法。在许多情况下,表13.1中给出的变比可以通过多种方式实现,从而导致不同的性能权衡。本文描述了使用双时钟相位(第13.3节)或超过两个时钟相位(第13.4节)实现期望M值的不同方法,并在第13.5节中比较了它们的性能。

13.3 双时钟相位拓扑

在双时钟相位SCPC中,浮置电容器在一个开关周期Ts内通过两个连续的时钟相位进行充放电。在稳态下,这两个时钟相位中的充电和放电是平衡的。

第13.3.1节概述了历史上使用的双时钟相位拓扑结构,而第13.3.2节描述了一种双时钟相位SCPC拓扑的综合方法。

13.3.1 已知拓扑结构概述

如第13.1节所述,开关电容功率转换器可实现升压和降压转换。事实上,设计用于电压转换比M的转换器,通过交换输入和输出连接,也可用于电压转换比1/M。如表13.1所示,对于给定数量的浮置电容可实现的每个M值,均存在相应的1/M值。因此,仅需考虑电压

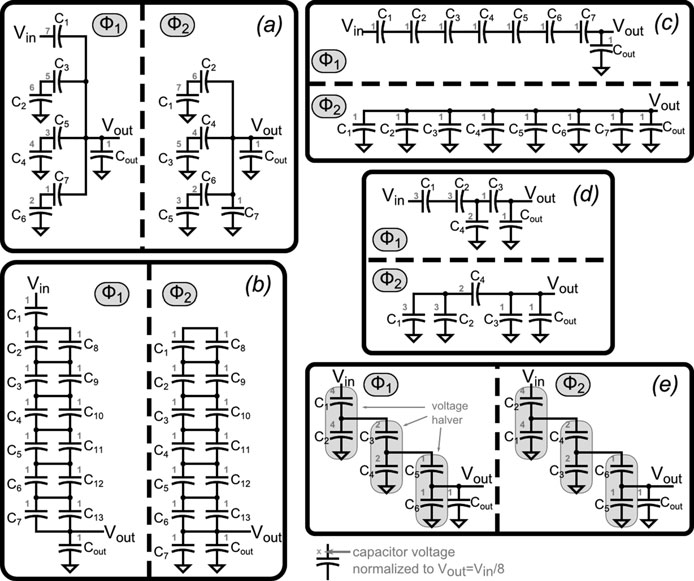

迪克森,(b) 梯形,(c) 串并联,(d) 分数‐1,(e) 递归 [24])

迪克森,(b) 梯形,(c) 串并联,(d) 分数‐1,(e) 递归 [24])

本节考虑降压转换,但所示的五种基本拓扑结构同样适用于升压转换[21, 22]。

图13.3中显示了用于M = 1/8的五种最著名的开关电容功率转换拓扑结构。对于每种拓扑结构,展示了两个时钟相位φ1和φ2下的电路构型,而未展示实现这两个状态所需的开关拓扑结构。浮置电容用Ci表示,其上的直流电压以相对于Vout的归一化值表示,而输出缓冲电容为Cout,其电压为Vout = Vin/8。

迪克森拓扑结构如图13.3a所示。该拓扑结构的灵感来源于格莱纳彻或科克罗夫特‐沃尔顿拓扑结构,后者有效实现了交流/直流电压转换,因此此处不予考虑。迪克森拓扑结构主要应用于升压转换器中,因为每个浮置电容充电路径中的一个开关可以用二极管代替,从而简化了转换器的控制。为了实现电压转换比M或1/M,需要M − 1个浮置电容器,因此图13.3a中有七个浮置电容器。梯形拓扑结构由两条相互串联的浮置电容器链组成,这两条链彼此相对上下滑动,这使其与其他四种拓扑结构不同

拓扑结构,因为在每个支路中,浮置电容在两个时钟相位中始终保持相同的连接顺序。为了实现M或1/M的电压转换比,需要M − 3个浮置电容,对应于图13.3b中的十三个浮置电容。这种对可用电容的低效利用使得梯形拓扑结构不太实用,但由于所有中间电压均可在梯形抽头处获得,因此它可用作辅助转换器,以在主开关电容功率转换器中实现所需的驱动电压[23]。

图13.3c所示的M − 1个浮置电容的串并联拓扑结构可实现M或1/M的电压比。与迪克森拓扑不同,在稳态下,每个浮置电容两端的直流电压相同。

图13.3d展示了根据表13.1使用最少数量电容器实现M=1/8的分数型拓扑的一个示例,即使用四个浮置电容。由于与其他四种拓扑结构相比,这种拓扑对电容的利用效率最高,因此在文献中可以找到大量分数型开关电容功率转换器的例子。然而,尽管表13.1列出了可能实现的电压比,但在实际中,通常需要通过试错法来推导出实现特定M值的分数型拓扑结构。

与图13.3d中的分数型拓扑相比,使用更多数量的电容器可通过模块化方法实现等间距的电压转换比[24],如图13.3e所示。通过对由两个浮置电容组成的相同2:1单元电路(M = 1/2)进行多个副本的智能重构,2N − 1可利用N个单元电路实现电压比,即使用2N个浮置电容。尽管对于给定数量的浮置电容而言,可能实现的电压比少于表13.1中的情况,但通过将相同单元电路以串联或并联方式递归排列的方法,使该拓扑结构易于重新配置。与分数型拓扑相比,这可能具有优势,特别是在需要多变比转换器以在更宽的输入或输出电压范围内保持效率的情况下。

13.3.2 拓扑综合

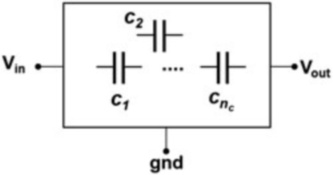

为了摆脱图13.3d中拓扑综合的试错过程,开发了一种用于综合开关电容功率转换器拓扑的通用迭代算法[25]。本节给出了该方法的简要概述。图13.4展示了一个双时钟相开关电容功率转换器的概念框图,该转换器由nc个浮置电容和三个外部端子组成。

表13.2 nc = 2、3 和 4 的有效配置对(省略冗余对)

| 描述 | 配置标识符 | 配置对 | q̂1, q̂2 | qsum |

|---|---|---|---|---|

| nc = 2 | 2 | [c1˚c2]&[c1jjc2] | 1,2 | 3 |

| nc = 3 | 3.1 | [(c1˚c2)˚c3]&[(c1jjc2)jjc3] | 1,2+1 | 4 |

| nc = 3 | 3.2 | [(c1˚c2)jjc3]&[(c1jjc2)˚c3] | 1+2,2 | 5 |

| nc = 3 | 3.3 | [(c1˚c2)jjc3]&[c1jj(c2˚c3)] | 1+1,1+1 | 4 |

| nc = 4 | 4.1 | [c1˚c2˚c3˚c4]&[c1jjc2jjc3jjc4] | 1,3+1 | 5 |

| nc = 4 | 4.2 | [(c1˚c2˚c3)jjc4]&[(c1jjc2jjc3)˚c4] | 1+3,3 | 7 |

| nc = 4 | 4.3 | [(c1˚c2˚c3)jjc4]&[c1jjc2jj(c3˚c4)] | 1+1,2+1 | 5 |

| nc = 4 | 4.4 | [((c1˚c2)jjc3)˚c4]&[((c1jjc2)˚c3)jjc4] | 3,2+3 | 8 |

| nc = 4 | 4.5 | [(c1˚c2)jj(c3˚c4)]&[((c1jjc2)˚c3)jjc4] | 2,2+1 | 5 |

| nc = 4 | 4.6 | [(c1˚c2˚c4)jjc3]&[((c1jjc2)˚c3)jjc4] | 3,2+1 | 6 |

| nc = 4 | 4.7 | [(c1˚c2)jjc3jjc4]&[(c1jjc2)˚c3˚c4] | 3+2,2 | 7 |

| nc = 4 | 4.8 | [((c1˚c2)jjc3)˚c4]&[c1jj(c2˚c3)jjc4] | 2,2+2 | 6 |

| nc = 4 | 4.9 | [(c1.c2)jj(c3.c4)]&[c1jj(c2.c3)jjc4] | 2,2+1 | 5 |

| nc = 4 | 4.10 | [((c1.c2)jjc3)jjc4]&[c1jj(c2.c3.c4)] | 1+1,2+1 | 5 |

| nc = 4 | 4.11 | [((c1.c2)jjc3)jjc4]&[(c1.c4)jj(c2.c3)] | 2+2,2 | 6 |

ci˚cj 意味着相同的电荷流动通过 ci 和 cj,cijjcj 意味着电荷在 ci 和 cj 之间共享

表13.1中介绍了开关电容功率转换器可实现转换增益的斐波那契极限。根据该极限,使用nc个浮置电容可以实现公式(13.2)给出的所有转换比:

$$

M(nc) = \frac{V_{out}}{V_{in}} = \frac{P}{Q}

$$

(13.2)

其中P和Q为整数,Fn是第nc个斐波那契数。针对目标转换比M = P/Q的综合算法分为两个步骤:

I) 迭代生成结构对:在此步骤中,通过迭代生成满足式(13.2)所给出的斐波那契极限要求的浮置电容数量的所有有效配置对(不考虑与外部端子的连接)。对于每个配置对,需确定nc个浮置电容器电压和输出电压Vout,因此有效的配置对是指能够产生nc + 1个有效的基尔霍夫电压定律(KVL)方程,同时保持每个浮置电容器的电荷平衡。这些有效的配置对如表13.2所示,其中ci表示浮置电容器,q̂1和q̂2为两个时钟相位期间的有效电荷系数,且qsum = q̂1 + q̂2。一个配置对描述了通过浮置电容器的电荷流动,并对应于每个时钟相位的基尔霍夫电压定律方程组。

II) 端子分配:具有期望电压转换比M = Vout/Vin = P/Q的变换器,其电荷转换比为qout/qin = 1/M = Q/P。归一化后,qout = Q且qin = P。通过端子分配,这三个外接

第13章 开关电容式功率变换器拓扑结构概述与性能比较(续)

13.3.2 拓扑综合(续)

nal端子连接到配置对,其中qsum ≥ max(P,Q),使得在两个相位φ1和φ2上满足电荷转换比。

应用这两个综合步骤的一个更详细示例如[25]所示。为了进一步说明该算法的应用,考虑M = 1/8,这意味着P = 1,以及Q = 8。按照该算法的步骤:

1) nc = 4 来自可能转换比的斐波那契极限,见表13.1。

2) 表13.2给出了nc = 4的所有可能配置对。该表的详细解释可在[25]中找到。

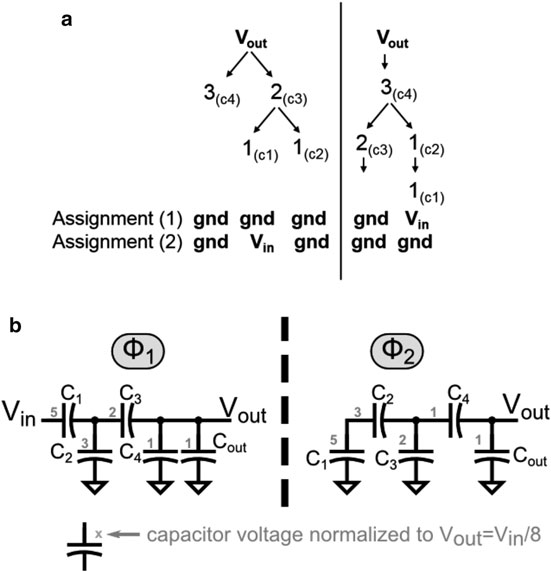

3) 在11种可能的配置对中,只有配置对(4.4)满足qsum ≥ max(P,Q),因为它具有值qsum = 8。其电荷流动图如图13.5a所示。当端子分配为P = 1且Q = 8时,可通过两种不同的方式实现,从而得到两个具有相同M的不同拓扑结构。图13.3d显示了对应于分配方式(1)的电容器极性分配结果,图13.5b显示了分配方式(2)的结果。

表13.2中配置对(4.4)的电荷流动图,(b) 综合成的替代型分数‐2 SCPC拓扑结构以实现M = 1/8)

表13.2中配置对(4.4)的电荷流动图,(b) 综合成的替代型分数‐2 SCPC拓扑结构以实现M = 1/8)

需要注意的是,具有M = 1/8的两种拓扑结构的浮置电容具有相同的电荷系数(如[18]中所定义),因此其稳态损耗和最终稳态损耗也相同。

阻抗。然而,它们在电容器和开关阻断电压方面有所不同,因此在特定应用中,一种拓扑结构可能比另一种更合适。这一点将在第13.5节进一步阐述。

13.4 多时钟相位拓扑结构

通过在每个开关周期内采用额外的时钟相位,可以扩展浮置电容最小所需数量的斐波那契约束Ts。在这些多时钟相位拓扑结构中,电容器的电荷平衡可以在超过两个时钟相位内发生。多时钟相位开关电容功率转换器的两个近期示例见第13.4.1节,而第13.4.2节展示了替代合成的多相时钟拓扑结构的示例。

13.4.1 已知拓扑结构概述

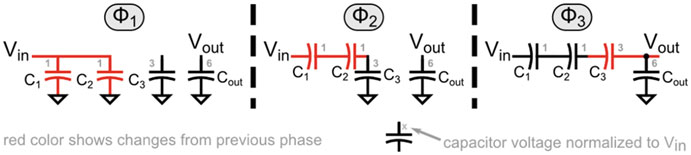

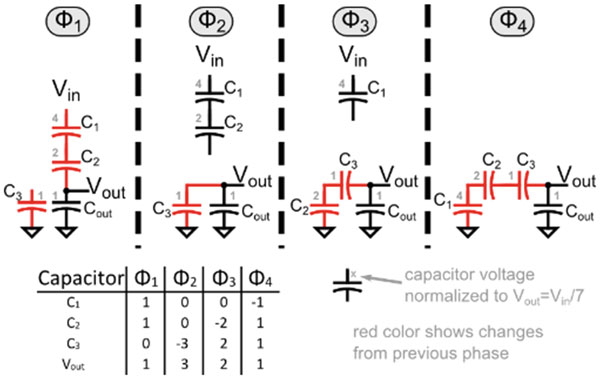

一种使用三相时钟实现电压升压转换比M = 6并采用三个浮置电容器的拓扑结构示例如图13.6[26]所示。通过利用额外的时钟相位,该拓扑结构使用更少一个的浮置电容器来实现M = 6。变换器的工作原理如下:

• φ1:C1和C2被充电至Vin,而C3未连接:归一化电荷系数qc1 = 2,qc2 = 2,qc3 = 0。

• φ2:C1和C2与Vin串联,且C3被充电至3Vin:电荷系数qc1 = −1, qc2 = −1, qc3 = 1。

• φ3:C1、C2和C3与Vin串联,以对Cout充电至6Vin:电荷系数qc1 = −1, qc2 = −1, qc3 = −1。

三相时钟中的电荷系数揭示了多时钟相位拓扑与双时钟相位拓扑之间的一个重要差异:在多时钟相位拓扑结构中,浮置电容在每个时钟相位期间所充(放)的电量不必相同,而双时钟相位拓扑则需要。浮置电容器的电荷平衡是在两个以上的时钟相位中完成的。

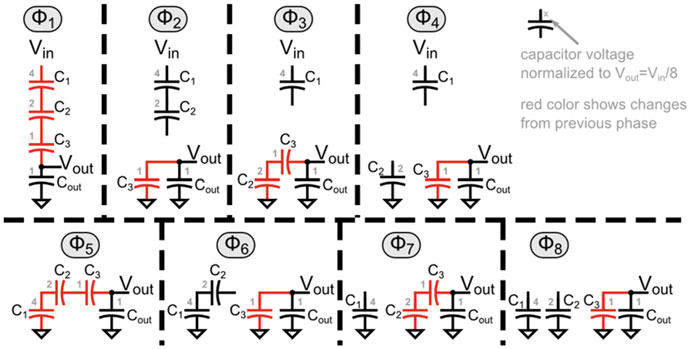

图13.7展示了一个示例,其中M = 1/2³ = 1/8采用三个浮置电容和八个时钟相位。在每个时钟相位期间向Vout提供一个单位电荷,因此在一个完整的开关周期内总共提供八个单位电荷。因此,每个浮置电容器在使用时的电荷系数始终为1/8,这是可能的最小值。该最小电荷系数将导致最低的SSL阻抗,这将在第13.5节中讨论(在相同的浮置电容总量和相同的开关频率下)。

在[27]该拓扑结构中,采用了一级级联的N个2:1单元电路(M = 1/2),以逐次倍频的方式运行,这等效于具有单一开关频率和2^N个时钟相位。这种方法具有模块化的优势,类似于图13.3e中的双时钟相位变体。

关于此拓扑结构,可以得出两点观察结论:(1)从电荷流动的角度来看,相位φ2、φ4、φ6和φ8的构型彼此完全相同,正如相位φ3和φ7的构型彼此完全相同;(2)每个构型仅包含一个基尔霍夫电压回路。这意味着该拓扑结构中实际上只有四种独特的构型。这与需要四个线性无关的回路以唯一确定电容器两端电压和输出电压Vout[25]的要求一致。

13.4.2 拓扑综合

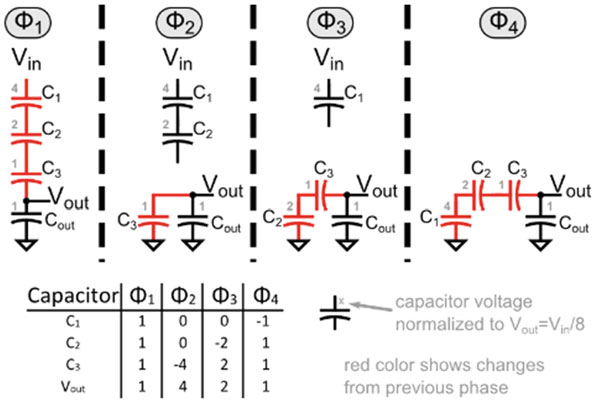

通过将图13.7中具有相同电荷流动的配置在单个相位中组合,可构建一种使用四个时钟相位而非八个时钟相位的多时钟相位分数拓扑,如图13.8所示。该拓扑结构的(充)放电行为如插图中的表格所示,归一化至qin = qout/8。

通过调整图13.8中的表格,可以生成其他多时钟相位拓扑结构。例如,考虑目标转换比为M = 1/7的情况。该变换器在一个开关周期内向Vin传输归一化总电荷7qout。为实现这一点,可对图13.8表格中的最后两行进行调整,得到图13.9表格中所示的浮置电容充放电行为。同时,浮置电容器的充放电也进行了调整以维持电荷平衡。所得拓扑结构如图13.9所示,形成一个具有M = 1/7的四时钟相位拓扑。一般而言,使用nc个浮置电容器,可实现具有相应转换比:

$$

M = \frac{P}{Q} = \frac{1}{2^{nc}}

$$

(13.4)

可以使用最多nc + 1个时钟相位实现(不包括具有相同电荷流动的配置重复情况,如二进制多时钟相位拓扑中的情况)。

13.5 拓扑性能比较

13.5.1 不同双时钟相位拓扑的比较

如前几节所述,有许多不同的拓扑结构可以提供相同的转换比M。然而,它们可能具有不同的优缺点,使其在不同应用中适用性各异。从开关电容功率转换器的功能角度来看,除M外,最重要的参数是输出阻抗Rout(见图13.2)。在SSL区域,输出阻抗RSSL可按如下方式计算:

$$

R_{SSL} = \frac{m}{f_s C_T}

$$

(13.5)

其中fs为开关频率,CT为浮置电容总量,而m是一个通过电路分析确定的与拓扑结构相关的参数[18]。

在FSL区域,输出阻抗RFSL仅取决于开关的导通电阻(忽略互连寄生电阻)和拓扑结构,可表示如下:

$$

R_{FSL} = p \cdot \frac{A_{swT}}{k_{sw}}

$$

(13.6)

其中p是通过电路分析获得的与拓扑结构相关的参数[18],AswT是开关的总面积,单位为[mm²],而ksw是一个与工艺相关的参数,表示单位硅面积开关的导通电阻(假设所有器件的电压额定值相同),单位为[Ω·mm²]。因此,比值的倒数AswT/ksw描述了设计所使用的电导量。

表13.3显示了多个不同拓扑结构的p和m参数值,这些拓扑结构提供相同的转换比(M = 1/8),但具有不同数量的浮置电容nc。如图所示,所有不同的双时钟相位拓扑结构(A–E)具有相同的m和p值,这意味着只要在相同开关频率下工作、使用相同总量的浮置电容以及开关所占用的相同总面积,所有考虑的拓扑结构都将呈现相同的输出阻抗。

表13.3中的拓扑F和G代表了在第13.4节中介绍的两种不同的多时钟相位拓扑结构,同样提供了M = 1/8。然而,由于它们的多时钟相位特性,无法直接从与双时钟相位拓扑结构的比较中得出结论。这将在第13.5.2节中进行评述,并结合最后两列的内容进行说明。

更详细地说,表13.3中所示的参数可以描述如下:

– nc:所需浮置电容器的数量。

– nsw:功率开关数量。

– m:RSSL、开关频率与浮置电容总量的乘积(在所有浮置电容器最优相对尺寸下),见公式(13.5)。

– p:RFSL与电导量之比,在所有功率开关最优相对尺寸下,见公式(13.6)。

– l:该参数可用于表示拓扑结构所遭受的底板功率损耗。若将充放电寄生底板电容所消耗的所有能量视为损耗(保守方法),则l参数计算如下:

$$

l = \sum_{i=1}^{n_c} C_{Ri} V_{Ri}^2

$$

(13.7)

其中CRi是每个浮置电容相对于浮置电容总量CT的归一化值,而VRi是每个浮置电容两端的电压相对于输入电压Vin的归一化值。根据式(13.7)中l参数的定义,可直接计算底板损耗总量:

$$

P_{bot} = V_{in}^2 f_s \alpha C_T l

$$

(13.8)

其中α是一个与工艺相关的比率,表示浮置电容的顶板和底板寄生参数相对于其电容的平均值。

– 所有功率开关的g·Voff²(电导g和阻断电压Voff)值的求和。阻断电压被平方是因为从概念上讲,功率开关的导通电阻随其阻断电压的平方而增加。该参数直观地反映了开关的尺寸大小,从而也反映了驱动其栅极所需消耗的能量。

– 所有浮置电容的Vci·qci的求和。此参数在全集成解决方案中尤为重要,因为在全集成解决方案中,浮置电容器的相对尺寸与其流过的电荷量以及其两端的工作电压成正比。

– VCi:每个浮置电容器Ci上的电压(相对于输出电压Vout = Vin/8进行归一化),如第13.3和13.4节所示。

– qCi:流过每个浮置电容器Ci的电荷量(相对于每开关周期的输入电荷量qin = qout/8 = Iout·Ts/8进行归一化)。

仅通过比较双时钟相位拓扑A–E的p和m参数,可以得出结论:所有不同的拓扑结构将提供相同的性能。然而,观察表格内容的其余部分可知,针对特定的应用与工艺组合,通过合适的拓扑选择可以获得显著优势。下面将讨论不同可能场景。

13.5.1.1 场景1:使用外部贴片电容实现的浮置电容

对于此场景,最值得关注的选项是分数型拓扑(D和E),因为它们需要最少数量的电容和引脚。由于贴片电容的底板寄生参数通常可忽略,因此在高压应用中,分数型‐1拓扑(D)更为合适,因为浮置电容上的工作电压更小。另一方面,如果这一点变得无关紧要(例如由于应用电压相对较低),则更倾向于选择分数‐2拓扑结构(E),因为其功率开关的电导与阻断电压的组合更低,这可能会导致更低的开关损耗。

13.5.1.2 场景2:全集成开关电容功率转换器

在完全集成的场景下,不同参数的相对重要性发生了显著变化。在集成领域中,浮置电容的数量本身并不是问题,但它们的总体积才是关键。如果应用的工作电压足够低,使得电容器上的电压不会影响其向更低电容密度实现的方向发展,则由于其极低的底板损耗以及开关所需的面积较小,迪克森拓扑结构(A)显然是最佳选择。另一方面,当特定应用在相对较高的电压下运行时,尽管底板损耗和开关损耗明显更大,但由于所有浮置电容上的电压被最小化,串并联拓扑结构(B)可能变得具有吸引力。分数‐2拓扑结构(E)在所需开关的阻断电压和电导之间表现出良好的折衷,同时具有非常低的底板功率损耗以及浮置电容上的施加电压。尽管在主要转换器参数中没有一项特别突出,递归拓扑结构(C)提供了一种非常有趣的模块化方法,通过智能连接实现M = 1/2的单元电路来构建多变比开关电容功率转换器。这意味可以设计一个单一单元电路,并通过复制和智能使用,轻松创建大范围的转换比(尽管并非所有可能的转换比都能实现)。遗憾的是,在需要极高或极低转换比的情况下,所需的单元电路数量以及相应的浮置电容数量将使得基于外部元件的设计(场景1)变得不切实际。

需要注意的是,表13.3中所示的所有参数值仅用于指示一种趋势,且仅适用于器件(包括浮置电容和功率开关)的电压额定值能够连续调节的情况。然而,大多数工艺技术所提供的器件具有特定的电压额定值,且以离散的步进方式变化。这显然排除了在每种不同的应用与工艺组合下存在绝对最优选择的可能性。

13.5.2 双时钟相位与多时钟相位拓扑结构的比较

在本节中,将对更传统的双时钟相位拓扑结构与多时钟相位拓扑结构进行比较,比较内容包括在考虑与第13.5.1节中所用参数相似的情况下可实现的增益和性能。

尽管与输出阻抗(p和m)以及可能的转换比相关的参数在所有双时钟相位拓扑结构中是通用的(除了图13.3b中的梯形拓扑),但对于采用多时钟相位运行的拓扑结构而言情况并非如此。因此,双时钟相位拓扑将与[27]中提出的方案进行比较(如二进制多时钟相位所示)拓扑F,图13.7),因为这是作者所知的多转换比多时钟相位拓扑结构的最佳示例。这种特定方法提供了一种系统化的方式,能够以少量浮置电容实现多个二进制比例的转换比,并在多时钟相位下工作。如第13.4.1节所述,采用了一种智能连接的电压减半级,每一级的工作频率是前一级的两倍,从而形成一种特殊的多时钟相位设计(具有2^nc个时钟相位对应nc个浮置电容)。

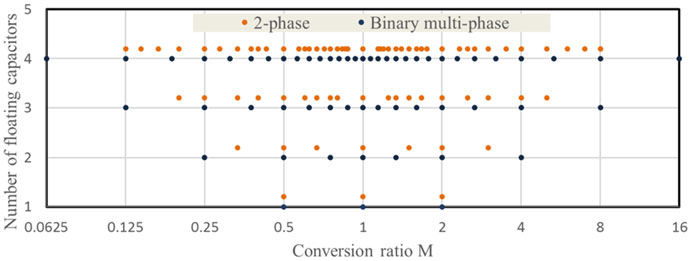

图13.10显示了分数双时钟相位(见表13.1)和二进制多时钟相位拓扑结构在不同浮置电容数量下可实现的转换比M(升压/降压)数量。如第13.4节所述,对于给定数量的浮置电容,多时钟相位拓扑结构能够实现比分数双时钟相位更高的最大转换比。然而,正是特定增益范围内可用转换比的密度,使得多比值设计能够在一定的输入或输出电压范围内保持高功率效率。

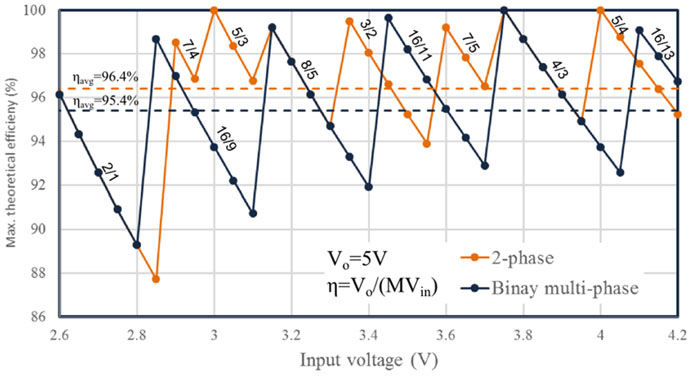

从图13.10可以看出,在特定增益范围内,分数双时钟相位设计相比二进制多相方法能够提供更多的转换比,最终实现更高的平均功率效率。例如,图13.11比较了基于双时钟相位或多时钟相位拓扑、使用四个浮置电容的多比值设计所能达到的理论最大功率效率(Vout/MVin)。在此示例中,如[13]所示,输出电压为5V,输入电压范围对应于锂离子电池(2.6–4.2V)。在此示例中,双时钟相位分数型拓扑在整个输入电压范围内的平均效率为96.4%,而二进制多时钟相位拓扑为95.4%。然而,由于二进制多时钟相位拓扑的转换比分布更均匀,提高了线性度,使得转换比控制更加容易。

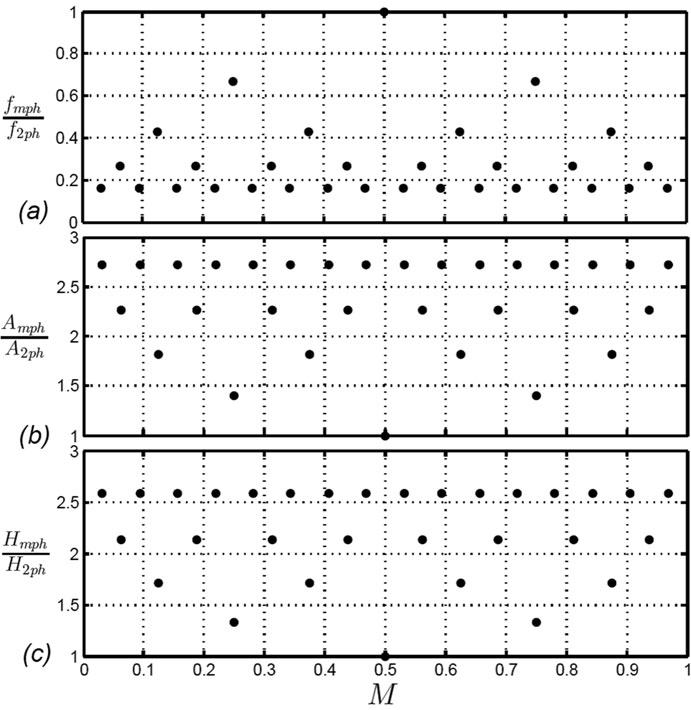

除了特定方法(使用两个或多个时钟相位)所能产生的转换比之外,开关电容功率转换器的性能还很大程度上取决于其输出阻抗和开关损耗。图13.12a展示了作为降压转换比M函数的多时钟相位设计(f_mph)与双时钟相位(f_2ph)设计之间的开关频率之比。两种设计在相同的浮置电容总量CT下提供相同的RSSL。显然可以看出,尽管多时钟相位拓扑在其每个开关周期Ts内由于具有更多的时钟相位而产生更多的开关事件,但它们需要更低的fs来提供相同的阻抗值。根据公式(13.5),对于给定的RSSL值,m随fs的变化而变化。因此,开关频率之比与各拓扑结构家族的m值之比一致。

二进制多时钟相位和双时钟相位拓扑结构也可以基于它们的RFSL值进行比较。图13.12b显示了多时钟相位情况(Amph)与双时钟相位设计(A2ph)在实现功率开关上所占用的总面积之比,作为实现转换比M的函数。从该图可以明显看出,双时钟相位拓扑结构在开关上所需的面积更小,因此在使用外部浮置电容实现开关电容功率转换器时更具吸引力,尤其是在需要高输出功率且更小的开关面积带来更低的成本的情况下[13]。类似于图m对应于图fs比率的情况,在图13.12a中,图13.12b中的开关面积比与根据公式(p值的比率一致,如公式(13.6)所示。

考虑到多时钟相位拓扑需要更大的功率开关(在相同的RFSL条件下),但需要较低的fs(在相同的RSSL和CT条件下),尽管每周期开关事件次数更多,因此比较它们预期的开关损耗量是很有意义的。可以通过计算以下乘积来估计任一设计方法可能产生的开关损耗量:开关频率和每周期切换的面积。对于双时钟相位拓扑,每周期切换的面积与开关中消耗的总面积相同(AswT)。然而,在多时钟相位设计中,某些开关在每个开关周期内可能被导通/关断多次Ts,这意味着切换的面积比AswT大一个因子switching_events/nsw(如果所有开关尺寸相同,如在二进制多时钟相位拓扑中)。为了解决这一问题,定义了以下参数作为开关损耗量的指示性参数:

$$

H = f_s A_{swT} \frac{\text{switching_events}}{n_{sw}}

$$

(13.9)

图13.12c显示了多时钟相位和双时钟相位拓扑(Hmph/H2ph)在不同转换比M下的该参数比值。可以看出,尽管多时钟相位设计的开关频率较低,但在提供相同转换比和输出阻抗的情况下,通常会带来更高的开关损耗。与之前的结果一样,当M = 1/2时,两种方法一致,此时仅使用一个浮置电容,并且只能实现两个时钟相位。

遗憾的是,由于可实现的双时钟相位拓扑结构种类繁多,且均能提供相同的转换比,因此无法将底板损耗以及不同器件的阻断电压包含在图13.12b, c的结果中而不失一般性。如果某个特定设计中的所有器件并非都具有相同的电压额定值,则在考虑不同的设计策略时也应将其考虑在内。

为了完整性,图13.7和13.8中提供的M = 1/8的多时钟相位设计也已包含在表13.3中(分别为拓扑F和G)。对于M = 1/8的特定情况,可将双时钟相位拓扑A–E与多时钟相位设计F和G进行比较,包括器件的阻断电压以及底板损耗。底板损耗的相对量由ml乘积得出,该乘积考虑了开关频率的差异。为了计算考虑功率开关阻断电压的相对开关损耗量(表的最后一列),需要仔细分析多时钟相位拓扑中哪些开关被多次使用,以及它们相对较低的fs(由m值表示)。从表13.3中可观察到以下内容:

- 多时钟相位拓扑在采用分立浮置电容的设计中显然是一种有趣的解决方案,因为在这些设计中减少元件和引脚数量非常重要。

- 多时钟相位拓扑在较低的fs下运行,尽管其底板损耗不一定更小。然而,在使用分立式浮置电容时,这一点可能无关紧要。

- 多时钟相位设计需要更大的开关面积,这对于高功率设计而言至关重要[13, 27]。

- 尽管在较低的fs下运行,多时钟相位设计并不会降低开关损耗,因为它们具有更多的每周期开关事件次数。

13.6 结论

各种开关电容功率转换器拓扑可用于实现所需的电压转换比M。不同拓扑结构之间的一个主要区别在于开关周期内所使用的时钟相位数量。在双时钟相位SCPC中,可以采用不同的拓扑结构,利用不同数量的浮置电容来实现所需的M值。分数型拓扑使用最少数量的浮置电容根据斐波那契极限实现给定的M值,但此类分数型拓扑的综合通常通过试错法完成。相反,本文给出了双时钟相位拓扑结构系统化推导的一个示例。在比较各种双时钟相位拓扑结构的性能时,在相同的开关频率、总浮置电容和总开关面积条件下,其输出阻抗相同。然而,本文表明,根据具体应用的不同,在底板损耗量、浮置电容上的电压或功率开关的阻断电压等方面的性能差异,使得不同的拓扑结构在不同应用中各有优势。

使用两个以上的时钟相位可以扩展双时钟相位转换器所能实现的M值范围。这使得在实现目标M值时可以使用更少数量的浮置电容,对于采用外部浮置电容的应用而言可能更具优势。对双时钟相位与二进制多时钟相位拓扑结构的比较表明,尽管双时钟相位拓扑结构的可实现M值范围较小,但在某一所需范围内可用的M值密度更高。这能够提高在整个期望输入电压范围内的平均效率,相较于二进制多时钟相位拓扑结构更具优势。此外,双时钟相位拓扑结构在实现功率开关时占用更小的面积,这对于高功率应用可能是有利的。然而,通过二进制多时钟相位采用模块化方法生成不同的转换比,可在产生更多转换比时降低复杂性。

1455

1455

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?