在CPU与主存的协同工作当中,根据摩尔定律,集成电路的性能每18个月翻一翻,对于CPU来说,它的速度是指数级增长,对于主存来说,它的容量是指数级增长,但是它的速度则是近似线性的增长,这样就会导致CPU余主存之间的速度差距会越来越大,所以,如何提高主存的工作速度成为计算机领域中优化方面的一大主题。

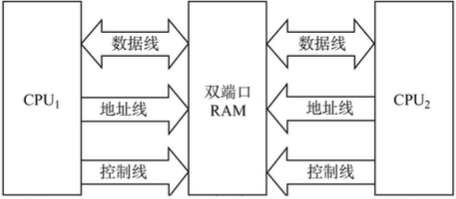

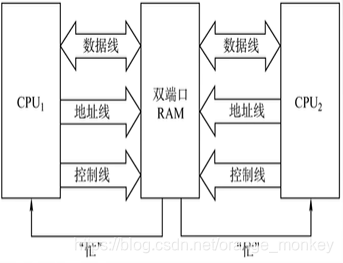

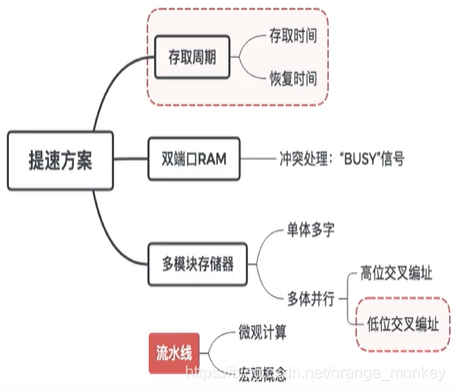

这里双口RAM和多模块存储器,原理是使用特殊的存储器的管理结构。

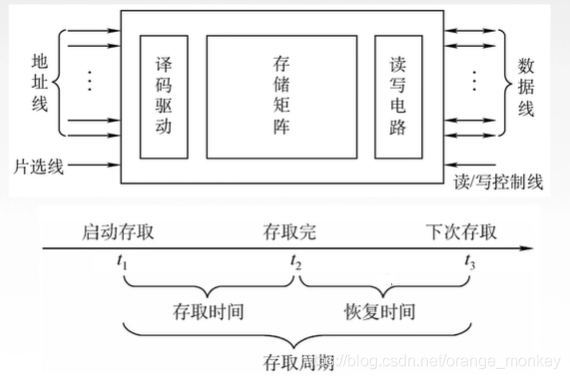

存取周期:

存取周期是用来衡量整个存储器的工作速度,是一个时间概念。

题外扩展:

{

与周期相对的一个概念是频率,频率是周期的倒数,单位时间内的次数,是个数量概念。

例:设1个周期的时间为T秒,则,则1秒运行的周期次数是1/T,即频率为f=1/T。

}

那么,对于存储器工作速度的优化就是通过一定的方法把恢复时间利用起来。

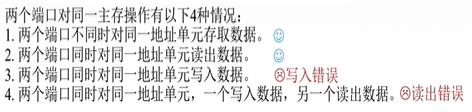

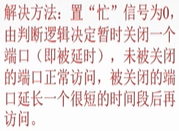

双端口RAM:

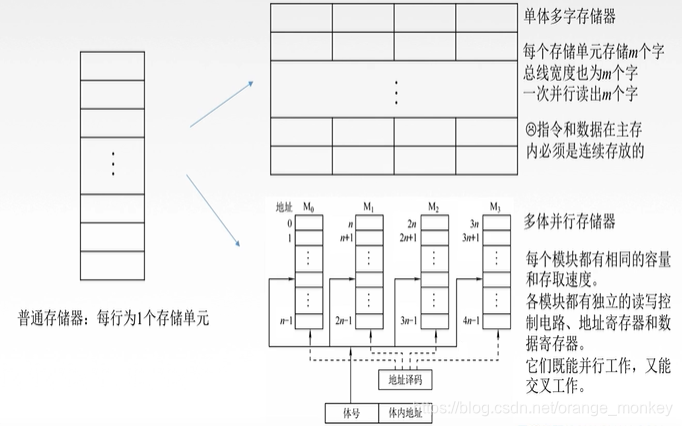

多模块存储器:

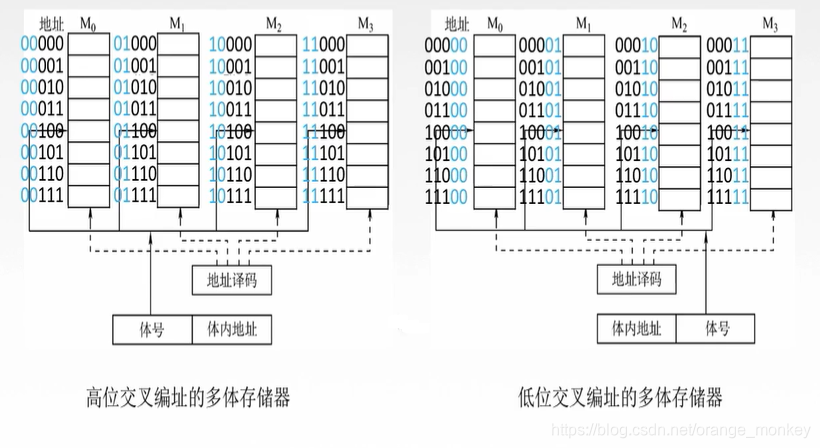

多体并行存储器:

分析:

假设:,

![]()

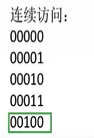

要访问的空间是:

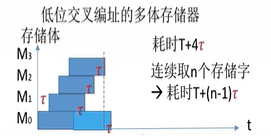

画出时空图:

例题:

理解题意:

题解:

所以,可以总结出:

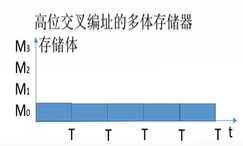

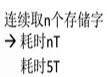

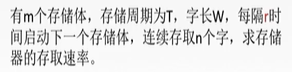

![]()

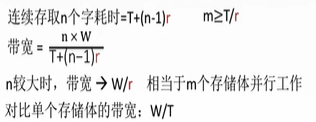

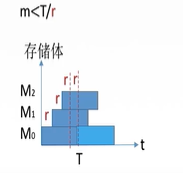

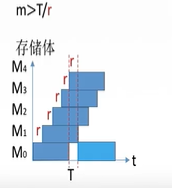

T / r , 相当于在一个周期内能启动的存储体个数,如果存储体个数小于这个值,那么在启动所有的存储体之后发现第一个还在恢复,就不能用这个公式了。

通俗解释:流水线嘛,工厂一条流水线上原本需要5个人才能刚好完成的工序,黑心老板抽走一个人,剩下4个人肯定忙不过来了。

m>T/r时,T周期内依然是4个r,没有增加,但是M0有一段时间是空闲的,这样对于存储体的利用率是不够高的,相当于多买了个存储体(如果不需要那么大容量的话)。

所以,一般情况下设计时直接设计m = T/r就够了,这个时候利用率比较高,提速也达到了最大的效果。

总结:

随着摩尔定律的发展,CPU速度与主存速度间的差距日益增大,优化主存速度成为关键。双端口RAM和多模块存储器通过特殊管理结构来提高效率。存取周期是衡量存储器速度的指标,频率则是其倒数。优化存储器速度的方法是利用恢复时间,例如双端口RAM允许同时读写,多模块存储器则通过并行访问多个存储体加速。设计时通常选择m=T/r以确保高利用率和最大提速效果。优化目标在于平衡CPU与主存的速度匹配,提高系统整体性能。

随着摩尔定律的发展,CPU速度与主存速度间的差距日益增大,优化主存速度成为关键。双端口RAM和多模块存储器通过特殊管理结构来提高效率。存取周期是衡量存储器速度的指标,频率则是其倒数。优化存储器速度的方法是利用恢复时间,例如双端口RAM允许同时读写,多模块存储器则通过并行访问多个存储体加速。设计时通常选择m=T/r以确保高利用率和最大提速效果。优化目标在于平衡CPU与主存的速度匹配,提高系统整体性能。

3573

3573

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?