目录

1.Use of Macros to Overcome Errors Faced in Package

5. 最小的factory override for stimulus objects

6.避免使用uvm_printer,使用conver2string()

8. Loop performance optimization

13.uvm_printer 打印array all element

14.uvm_compare mismatch的时候不打印信息

1.Use of Macros to Overcome Errors Faced in Package

package pkg1;

`include "adder_design.sv"

`include "tb.sv"

endpackage

package pkg2;

`include "adder_design.sv"

`include "adder_tb.sv"

endpackage

module top();

`ifndef ADDER_DESIGN

`define ADDER_DESIGN

import pkg2::*;

`endif

...

endmodule2.fork-join_none 中使用loop

使用automatic

module top;

initial begin

for (int i = 0; i < 4; i++) begin

fork

automatic int l = i;

display(l);

join_none

end

end

task display(int i);

$display("i = %d", i);

endtask

endmodule3.random 机制

3.1 如果名字重复,使用local

rand_success = trans.randomize() with {trans.addr == local::addr; };

3.2 动态数组需要定义size

class Ethernet;

rand bit [3:0]payload[];

constraint c { payload.size() == 4;}

endclass3.3 检查randomize 结果

4.uvm_config_db的使用要注意

a.尽量避免传递数值,有需要的话可以封装成class

b. wildcard谨慎使用

c. it is recommended to minimize the number of uvm_config_db entries.

...

5. 最小的factory override for stimulus objects

Low performance, 因为多次调用了factory中的create

//Low performance code

task body;

seq_item item;

repeat (200) begin

item = seq_item::type_id::crease("item"0;

start_item(item);

if (item.randomize()) begin ... end

finish_item(item);

endtaskHigh performane, 只第一次create,然后clone 它

//High performance

task body;

seq_item orig_item = seq_item::type_id::create("item");

seq_item item;

repeat(200) begin

$cast(item, orig_item.clone());

start_item(item);

assert(item.randomize());

finish_item(item);

end

endtask6.避免使用uvm_printer,使用conver2string()

在class 自定义conver2string

virtual function string convert2string();

string s = super.convert2string();

s = { s, $psprintf( "\nname : %s", get_name() ) };

s = { s, $psprintf( "\nflavor : %s", flavor.name() ) };

s = { s, $psprintf( "\ncolor : %s", color.name() ) };

return s;

endfunction: convert2string7.UVM objections 使用

Objections should only be used by the controlling threads, and it is also very necessary to place the objections in the run-time method of the top level test class, or in the body method of a virtual sequence. Using them in any other place is likely to be unnecessary and also cause a degradation in performance.

在virtual sequence中的body;或者在top level的testcase的run-time method

//High Performance code

class sequence extends uvm_sequence#(seq_item);

task body;

seq_item item = seq_item::type_id::create("item");

repeat(5) begin

start_item(item);

assert(item.randomize());

finish_item(item);

end

sequencer seqr;

task body;

`uvm_objection objection = new("objection");

sequence seq= sequence::type_id::create("seq");

objection.raise_objection(seqr);

seq.start(seqr);

objection.drop_objection(seqr);

endtask8. Loop performance optimization

1.loop的性能取决于loop中的工作

下面高效代码,减少了每次循环化size的计算

//Less efficient code

int arr[];

int total = 0;

for(int i = 0;i< arr.size();i++) begin

total += arr[i];

end

//High Performance Code

int arr[];

int arr_size;

int tot = 0;

arr_size = arr.size();

for(int i = 0; i < arr_size; i++) begin

tot += arr[i];

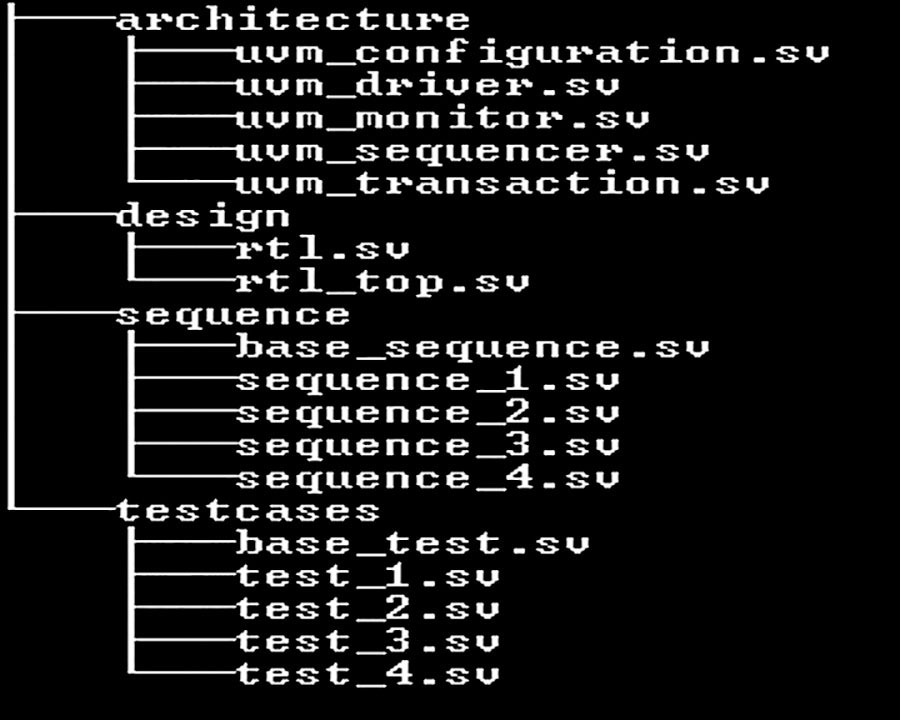

end9.文件目录

10.sequence

1.避免使用pre_body() and post_body, 另一篇文章有解释

2.启动一个sequence, 推荐使用sequence.start(sequencer);

3.启动一个sequence_item 推荐使用, start_item(), randomize(), finish_item()

11.getenv

import "DPI-C" function string getenv(input string env_name);

function string get_env(string name);

return getenv(name);

endfunction

12.match_string

function bit match_string(string s1, string s2);

int l1,l2;

bit vld;

vld = 0;

l1 = s1.len();

l2 = s2.len();

if (l2 > l1) return 0;

for(int i = 0;i < l1 - l2 + 1; i ++)

if( s1.substr(i,i+l2 -1) == s2) vld = 1;

return vld;

endfunction

13.uvm_printer 打印array all element

在任意地方(tb/test)加入

uvm_default_printer = uvm_default_table_printer;

uvm_default_printer.knobs.begin_elements=-1;

14.uvm_compare mismatch的时候不打印信息

class my_comparer extends uvm_comparer;

function new ();

super.new();

this.show_max = 0;

endfunction

endclass

my_comparer comparer = new();

left.item.compare(right.item, this.comparer);

本文围绕UVM展开,介绍了使用宏克服包中错误、fork - join_none中使用loop、random机制、uvm_config_db使用注意事项等内容。还提及了刺激对象的factory override、避免使用uvm_printer、循环性能优化等实用技巧,对UVM使用者有较大帮助。

本文围绕UVM展开,介绍了使用宏克服包中错误、fork - join_none中使用loop、random机制、uvm_config_db使用注意事项等内容。还提及了刺激对象的factory override、避免使用uvm_printer、循环性能优化等实用技巧,对UVM使用者有较大帮助。

696

696

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?