1、简述

在汽车ECU开发中,标定是必不可少的一环,Infineon Tc3xx提供的overlay功能可以将flash地址重映射到ram区域,进而通过XCP等协议就可以直接修改flash地址对应的变量,非常方便。

2、Overlay

相关的内容可以在UserManel的5.3.9节中找到,在CPU章节,感兴趣可以看看原文。

2.1 数据访问重定向

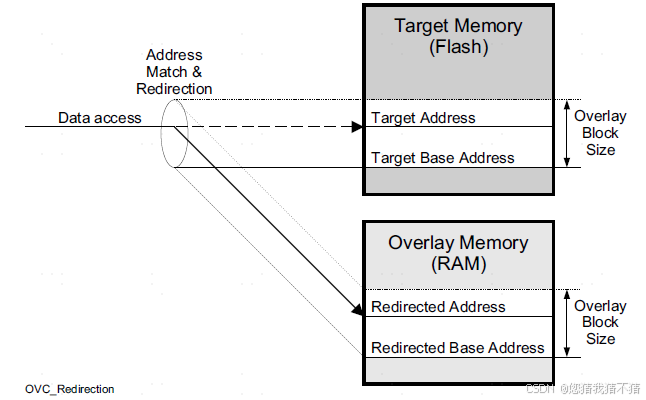

如上图所示,当开启Overlay功能后,在访问目标内存的时候会转而访问重定向内存地址,在配置Overlay Block的时候有几个比较重要的东西:

① Target Base Address:要重定向的目标地址范围的起始地址

② Block Size:标定区域块大小

③ Redirection Base Address:重定向基地址

个人认为还是比较好理解的,就是你要从哪准备标,标多大块,定义好了之后方便干活。同时在Tricore里每个核给了32个可定义大小和范围的overlay block,可通过寄存器使能和关闭。

2.2 相关寄存器

与2.1节提到的几个地址和块大小相关的配置寄存器有四个,分别是OSEL、OTARx、OMASKx和RABRx,还有一个全局重映射控制寄存器在SCU里面,下面我们详细介绍下各个寄存器和配置项。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3330

3330

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?