目录

一、实验目的及原理

1、实验目的

掌握组合逻辑电路的分析与设计。掌握真值表、逻辑函数表达式、卡诺图化简基本概念和方法。

2、实验原理

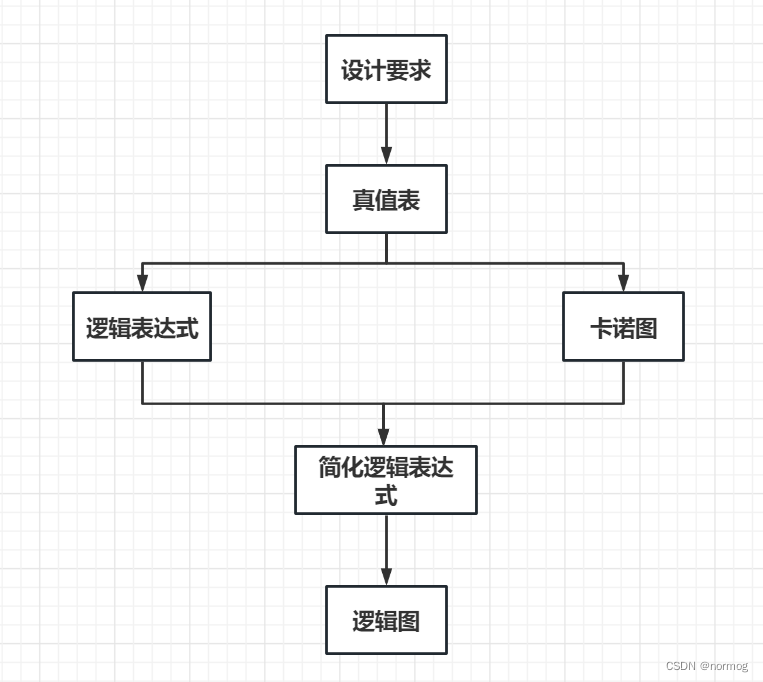

使用中、 小规模集成电路来设计组合电路是最常见的逻辑电路。 设计组合电路的一般步骤如下图所示:

根据设计任务的要求建立输入、 输出变量, 并列出真值表。 然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。 并按实际选用逻辑门的类型修改逻辑表达式。 根据简化后的逻辑表达式, 画出逻辑图, 用标准器件构成逻辑电路。 最后, 用实验来验证设计的正确性.

二、实验内容

1、组合逻辑电路——四路表决器

用“ 与非” 门设计一个表决电路:当四个输入端A、B、C、D中有三个或四个为“ 1” 时,输出端才为“ 1”。

(一)列真值表

| D | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| A | 0 | 0 | 0 | 0 |

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?