一、代码实现

设计定义:让LED灯按照亮0.25s,灭0.5s,亮0.75s,灭1s的状态循环。

`timescale 1ns / 1ps

module led_step2(

input clk ,

input rstn ,

output led

);

reg[26:0] cnt ;

reg r_led ;

assign led = r_led ;

parameter MCNT = 125_000_000;

always @(posedge clk or negedge rstn) begin

if(!rstn)

cnt <= 0;

else if(cnt == MCNT - 1)

cnt <= 0;

else

cnt <= cnt + 1'd1;

end

always @(posedge clk or negedge rstn) begin

if(!rstn)

r_led <= 1;

else if(cnt == MCNT/10 - 1)

r_led <= 0;

else if(cnt == MCNT *3/10 - 1)

r_led <= 1;

else if(cnt == MCNT *3/5 - 1)

r_led <= 0;

else if(cnt == MCNT - 1)

r_led <= 1;

else

r_led <= r_led;

end

endmodule

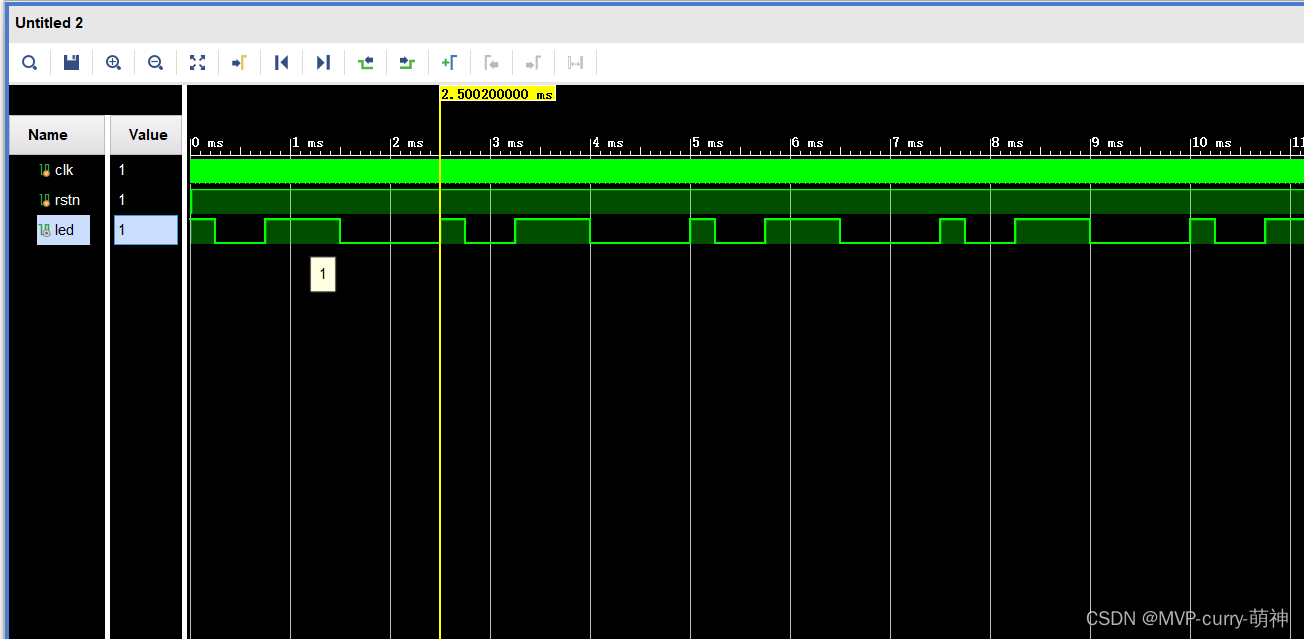

二、仿真

`timescale 1ns / 1ns

module led_step1_tb();

reg clk ;

reg rstn ;

wire led ;

led_step2 #(

.MCNT(125_000)

)inst0(

.clk (clk ) ,

.rstn (rstn) ,

.led (led )

);

initial clk = 1;

always #10 clk = ~clk;

initial begin

rstn = 0;

#201;

rstn = 1;

#1000_000_000;

$stop;

end

endmodule

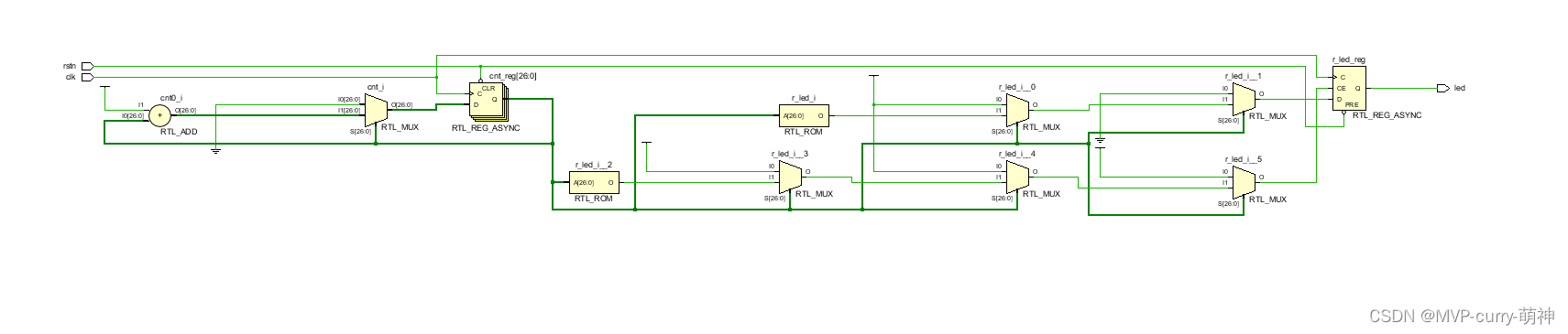

本文详细介绍了如何使用Verilog语言设计一个模块,使LED灯按照亮0.25s、灭0.5s、亮0.75s和灭1s的周期循环。并通过示例给出了代码实现和电路仿真过程。

本文详细介绍了如何使用Verilog语言设计一个模块,使LED灯按照亮0.25s、灭0.5s、亮0.75s和灭1s的周期循环。并通过示例给出了代码实现和电路仿真过程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?