fsbl是elf文件,是运行的第一个用户应用程序,基本工作是将逻辑从flash复制到RAM中。用户对所有所有的可编程元素的定义可以借助Bootgen工具组装成一个可引导的映像。fsbl就是来打开这个单一的映像的。

1、上电 Power Applied

一旦电源连接到设备,内部的电源管理电路会确保系统各个电源轨(例如供电给CPU、内存、I/O接口等的电压轨)保持稳定。电源轨的稳定性对于保证设备正常工作至关重要,尤其是在启动过程中,设备必须确保各种电压满足硬件组件的要求。

2、引导与管理 PMU ROM Code Executes

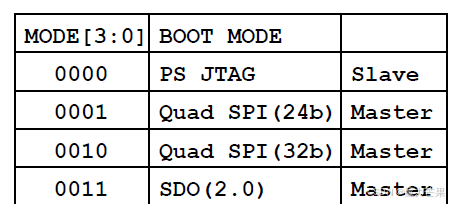

在启动过程中,PMU(Platform Management Unit,平台管理单元)检查引导模式引脚的状态。引导模式引脚(如 Boot Mode Pins)是硬件级的输入引脚,用于决定系统启动时应该从哪个介质(如闪存、SD卡、外部存储等)加载操作系统或固件镜像。这一过程对于启动顺序非常关键,决定了系统如何加载操作系统或引导加载程序。对应读取引脚的是FPGA上的拨码开关;不同的FPGA的拨码设置不同

例如:

在加载 FSBL 之前,PMU 会执行一些电源管理、硬件初始化、管理存储器选择等任务,确保设备能够按照预期方式启动。在完成这些初始化任务后,PMU会释放复位信号到 “配置和安全单元”。从而进入下一个阶段的系统启动过程,这种机制确保了设备在启动时的电源稳定性、安全性,并为后续的引导和操作系统加载做好准备。

3、捕获与加载 CSU ROM Code Executes

与PMU类似,CSU(Configuration and Security Unit,配置和安全单元)是负责硬件配置、启动过程管理和安全性的模块。它通常会控制启动的顺序,保护敏感信息,并确保在启动过程中没有受到恶意篡改。

①捕获 :根据拨码开关设置的启动模式,CSU会在对应的模式下捕获引导映像的标头(Header),CSU根据引导头中的信息,找到FSBL的位置并将其复制到OCM RAM (On-Chip Memory,处理器的快速内存)中,以便FSBL快速执行。如果需要,CSU还会加载PMU固件到PMU的RAM中。

②加载:CSU根据引导头指示,将控制转移到指定的处理器(Processor),处理器在OCM中开始执行FSBL代码。

4、执行FSBL Either Processor or Mux

如果系统包含多个处理器,复用器决定哪一个处理器负责执行引导加载程序。处理器读取FSBL代码并开始执行。

FSBL 是系统启动时的第一阶段引导加载程序,在OCM RAM中执行,通常完成一些基本的硬件初始化后(如设置时钟、初始化内存控制器、加载初步的引导映像等),将一个应用程序加载到一个处理器。

当为多个处理器加载多个应用程序时会由SBL 负责进一步的引导工作,在DDR中执行,通常包括将操作系统的内核加载到主内存中( DDR 或其他大容量内存中)、驱动程序或其他系统固件,并将控制权交给操作系统或其它启动程序。

当操作系统加载后,应用程序加载开始运行,整个系统进入正常工作状态。

总结:

- FSBL加载:FSBL通常是引导映像的第一个块,负责对硬件进行初始化(如时钟、内存、外设等),并为后续的操作做好准备。

- SBL加载:在FSBL完成基础初始化后,第二阶段引导加载程序(SBL)会接管,通常它会加载操作系统内核、设备树等。

- 操作系统加载:引导映像中可能包含操作系统内核,SBL将其加载到大内存(DDR)中并启动系统。

- 应用程序加载:在引导映像中加载其他应用程序或固件模块,供处理器或硬件使用。

6597

6597

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?