继上一篇FPGA 之 DAC3482 学习(一) https://blog.youkuaiyun.com/m0_58129662/article/details/145722667

对DAC3482继续研读。

6.3.3 Input FIFO

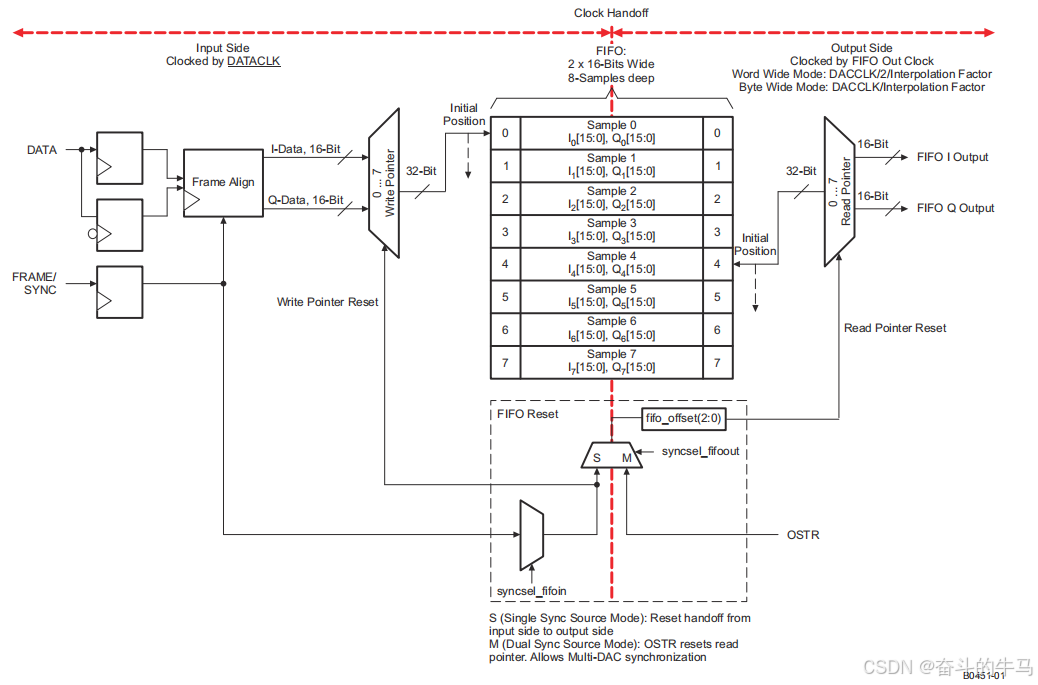

DAC3482包括一个2通道,16位宽和8样本深度输入FIFO。

FIFO 的输出时钟由DACCLK产生,当为字模式下时,速率为DACCLK/2*Interpolation。为字节模式下时,速率为DACCLK/Interpolation。

可以使用config9的 fifo_offset【2:0】对FIFO偏移量进行操作。我认为的此偏移量就是写和读指针的距离,写指针在0地址位,读指针在4地址位,在读和写的时钟是同一时钟情况下,他们之间的间隙不变,在不同时钟下间隙不同,可能发生写和读指针在同一个地址位。

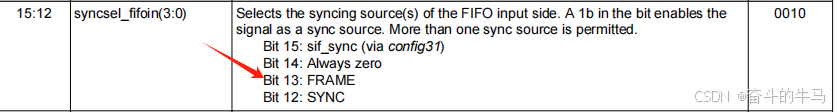

写指针是通过config32的【15:12】syncel_fifoin(3:0) 控制同步源,写指针同步元时钟为DATACLK。

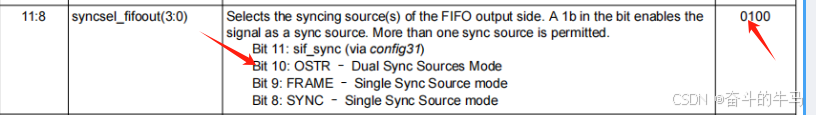

读指针是通过config32的【11:8】syncel_fifoout(3:0) 控制同步源,读指针同步元时钟为DACCLK,这是由于DATACLK到FIFO输出时钟会导致复位信号的相位模糊性,并将基于FIFO输出时钟的捕获边缘产生延迟变化。OSTR信号来独立于写指针来重置FIFO读取指针的替代方案。OSTR信号由DACCLK采样。

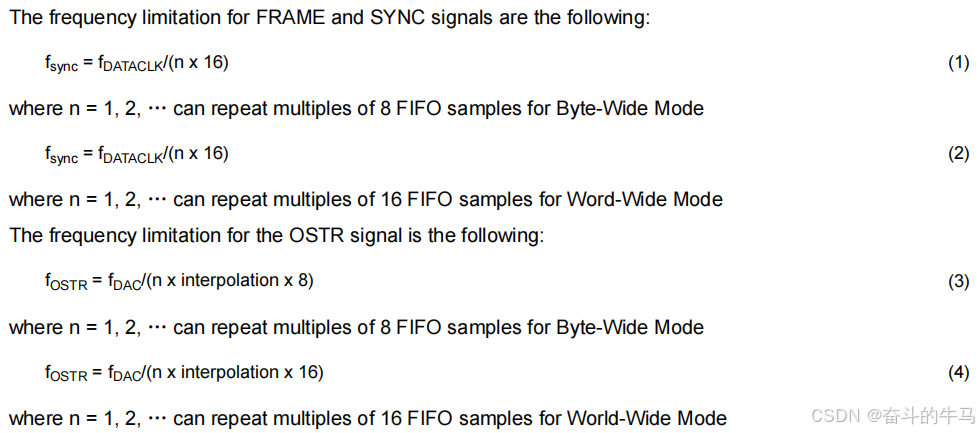

接下来介绍帧和同步信号的频率限制如下:

大概的意思FRAME和SYNC 是用于数据传输,在数据流中标记帧或周期的开始。

1. Byte-Wide Mode(字节宽模式)

在字模式下,FIFO缓存的样本宽度是8位,即1字节。通常来说,1字节=8位。所以,公式中用到的

n*16,实际上是与FIFO样本传输的“宽度”有关。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1193

1193

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?