前言

有了对64B66B协议的认识以及我们之前设计8B10B自定义PHY的经验,本文开始对64B66B自定义PHY的设计

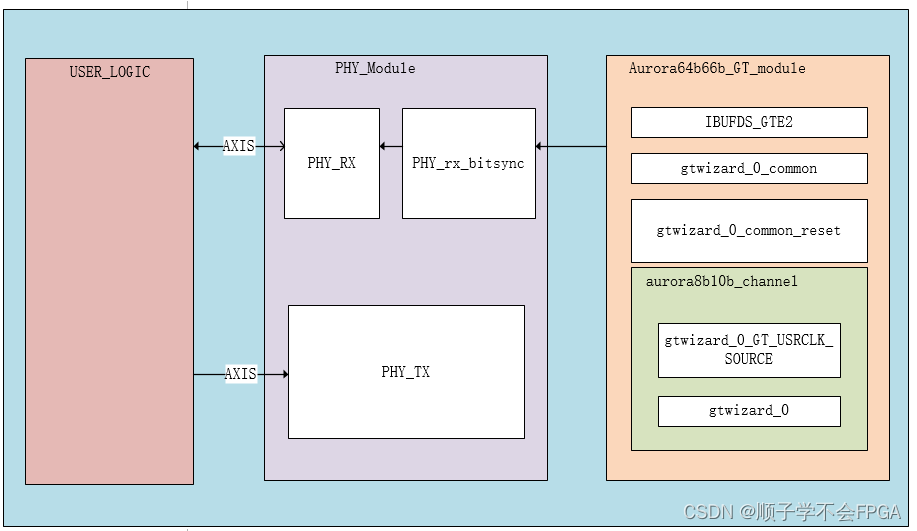

一、设计框图

二、GT_module

该模块整体设计与8B10B几乎一致,只有一些端口的区别;再就是将QPLL复位产生模块gtwizard_0_common_reset从GT_channel模块放到了GT_module模块,但其实本质没有任何区别。

主要还是IP核配置变为64B66B之后输入输出的接口有一些变化,包括帧头信号,对齐信号以及发送队列计数器信号等。

同理,用户需要多个channel的时候只需要在GT_module模块当中例化多个GT_channel模块即可。

module GT_channel(

input i_sysclk ,

input i_gtrefclk ,

input i_rx_rst ,

input i_tx_rst ,

output o_tx_done ,

output o_rx_done ,

input i_tx_polarity ,

input [3 :0] i_tx_diffctrl ,

input [4 :0] i_txpostcursor ,

input [4 :0] i_txpercursor ,

input i_rx_polarity ,

input [2 :0] i_loopback ,

input [8 :0] i_drpaddr ,

input i_drpclk ,

input [15:0] i_drpdi ,

output [15:0] o_drpdo ,

input i_drpen ,

output o_drprdy ,

input i_drpwe ,

input i_qplllock ,

input i_qpllrefclklost ,

output o_qpllreset ,

input i_qplloutclk ,

input i_qplloutrefclk ,

input i_data_valid ,

output o_rx_clk ,

output [63:0] o_rx_data ,

output o_rx_valid ,

output [1 :0] o_rx_header ,

output o_rx_header_valid ,

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1838

1838

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?