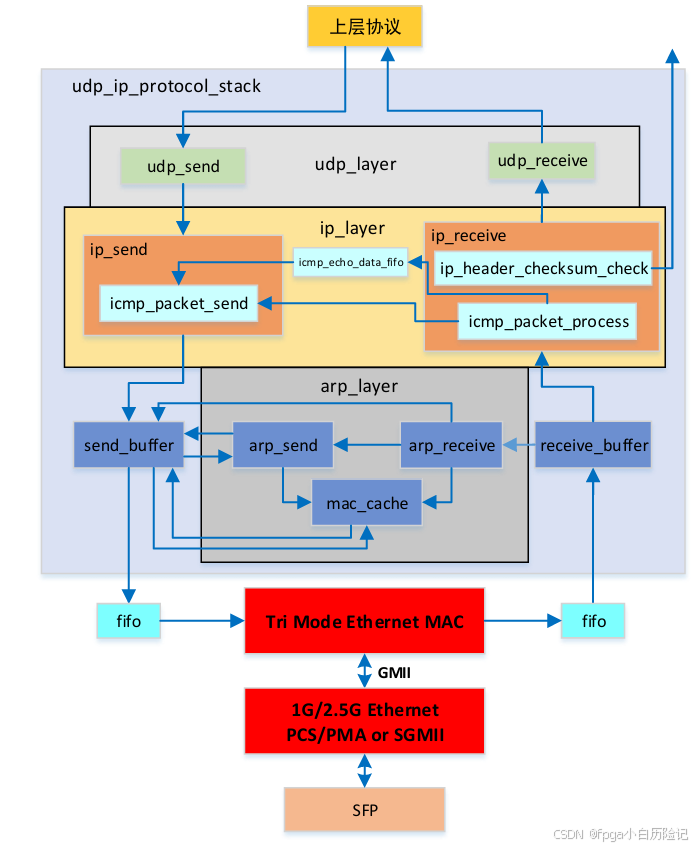

所学习的千兆以太网模型如下图所示:

本篇旨在解释该UDP_千兆光通信框架:1G/2.5G Ethernet PCS/PMA or SGMII ip核的上一级为什么是Tri Mode Ethernet MAC IP核;

在学习该篇文章之前需要先学习:https://blog.youkuaiyun.com/lzr232/article/details/145058267?fromshare=blogdetail&sharetype=blogdetail&sharerId=145058267&sharerefer=PC&sharesource=lzr232&sharefrom=from_link

了解OSI七层模型之间的信息交互关系;

一、以太网接口电路的主要构成

更加详细的信息,可转战:https://blog.youkuaiyun.com/dongdongnihao_/article/details/137061601?fromshare=blogdetail&sharetype=blogdetail&sharerId=137061601&sharerefer=PC&sharesource=lzr232&sharefrom=from_link

要学习两个IP核连接的底层原理,首先需要了解以太网接口电路的主要构成。如下图所示:

从硬件的角度看,以太网接口电路主要由MAC(Media Access Control)控制器和物理层接口PHY(Physical Layer,PHY)两大部分构成。

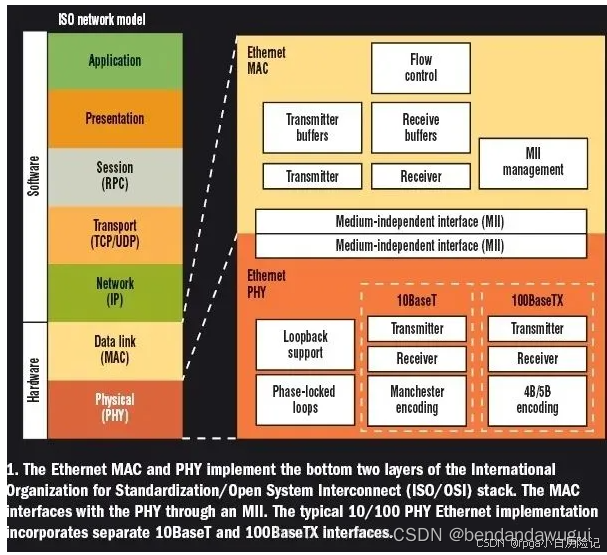

MAC及PHY工作在OSI七层模型的数据链路层和物理层。具体如下:

因此串行数据在经过PHY后需要传输至MAC层;

了解大致构成之后,就需要学习MAC是什么,与PHY的连接方式:

二、什么是MAC

OSI协议栈中的数据链路层可进一步细分为较低的介质访问控制(MAC)子层和较高的逻辑链路控制(LLC)子层。当它接收到一个分组后,它从MAC子层向上传送。如果有多个网络和设备相连,LLC层可能将分组送给另一个网络

介质访问控制 (MAC, Media Access Control):

- 功能:MAC子层负责把物理层的“0”、“1”比特流组建成帧,并通过帧尾部的错误校验信息进行错误校验;提供对共享介质的访问方法,包括以太网的带冲突检测的载波侦听多路访问(CSMA/CD)、令牌环(TokenRing)、光纤分布式数据接口(FDDI)等。

逻辑链路控制 (LLC, Logical Link Control):

- 功能:LLC负责识别网络层协议,然后对它们进行封装。LLC报头告诉数据链路层一旦帧被接收到时,应当对数据包做何处理。它的工作原理是这样的:主机接收到帧并查看其LLC报头,以找到数据包的目的地,比如说,在网际层的IP协议。LLC子层也可以提供流量控制并控制比特流的排序。

应用:不管是在传统的有线局域网(LAN)中还是在目前流行的无线局域网(WLAN)中,MAC协议都被广泛地应用。==在传统局域网中,各种传输介质(铜缆、光线等)的物理层对应到相应的MAC层,==目前普遍使用的网络采用的是IEEE802.3的MAC层标准,采用CSMA/CD访问控制方式;而在无线局域网中,MAC所对应的标准为IEEE802.11,其工作方式采用DCF(分布控制)和PCF(中心控制)。

因此,数据经过PHY层传输到MAC层,而后再进行组帧

三、MAC层与PHY层数据传输接口

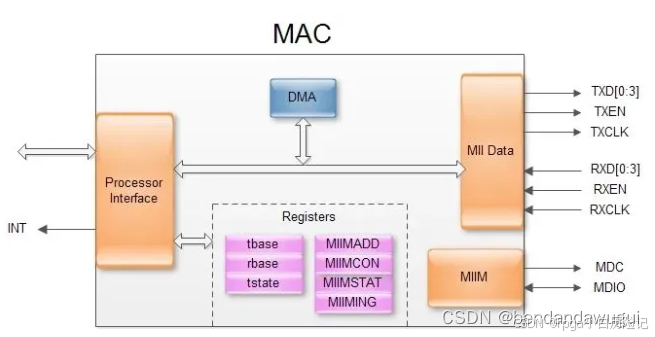

以太网MAC芯片的一端接计算机PCI总线,另外一端就接到PHY芯片上,它们之间是通过MII接口链接的,MII有各种衍生版本——GMII、SGMII、RMII、RGMII等。一个MAC的结构图如下图所示:

3.1 MII

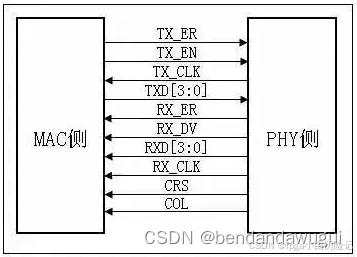

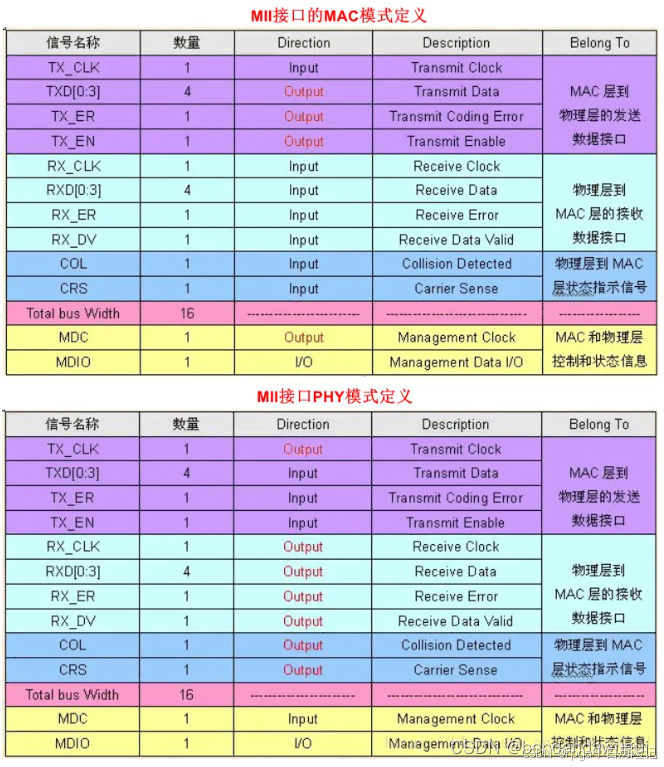

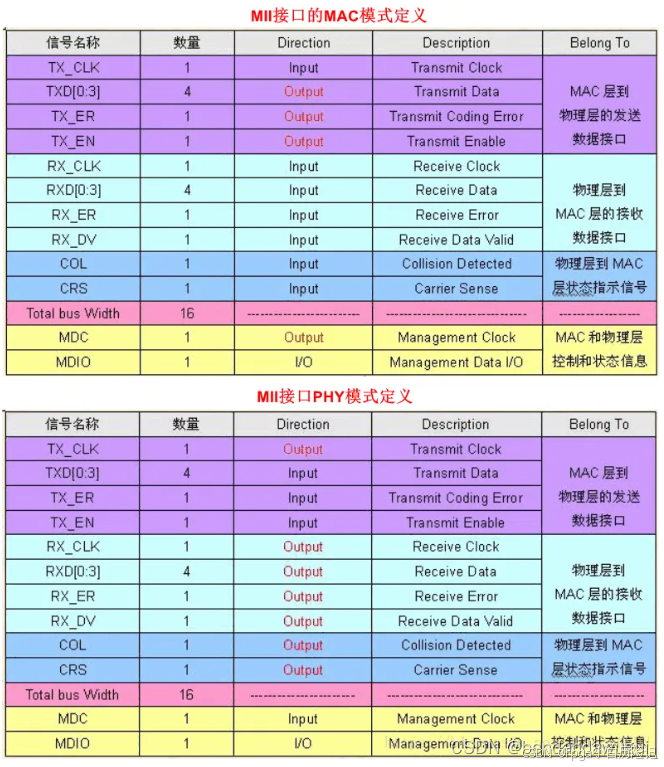

MII(Media Independent Interface)即媒体独立接口,MII 接口是 MAC 与 PHY 连接的标准接口。它是 IEEE-802.3 定义的以太网行业标准。MII 接口提供了 MAC 与 PHY 之间、PHY 与 STA(Station Management)之间的互联技术,该接口支持 10Mb/s 与 100Mb/s 的数据传输速率,数据传输的位宽为 4 位。MII 接口如下图所示:

MII接口主要包括四个部分。一是从MAC层到PHY层的发送数据接口,二是从PHY层到MAC层的接收数据接口,三是从PHY层到MAC层的状态指示信号,四是MAC层和PHY层之间传送控制和状态信息的MDIO接口。

具体时序可以根据芯片选型去看手册~

3.2 RMII

简化媒体独立接口是标准的以太网接口之一,比 MII 有更少的 I/O 传输。RMII 口是用两根线来传输数据的,MII 口是用 4 根线来传输数据的,GMII 是用 8 根线来传输数据的。

MII/RMII 只是一种接口,对于10Mbps 线速,MII 的时钟速率是 2.5MHz 就可以了,RMII 则需要 5MHz;对于 100Mbps 线速,MII 需要的时钟速率是 25MHz,RMII 则是 50MHz。

MII/RMII 用于传输以太网包,在 MII/RMII 接口是 4/2bit 的,在以太网的PHY里需要做串并转换,编解码等才能在双绞线和光纤上进行传输,其帧格式遵循IEEE 802.3(10M)/IEEE 802.3u(100M)/IEEE 802.1q(VLAN)。

3.3 GMII

GMII是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口。GMII 采用 8 位接口数据,工作时钟125MHz,因此传输速率可达 1000Mbps。

同时兼容 MII 所规定的10/100 Mbps工作方式。

3.4 RGMII

RGMII(Reduced Gigabit Media Independant Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

- 发送/接收数据线由8条改为4条

- TX_ER和TX_EN复用,通过TX_CTL传送

- RX_ER与RX_DV复用,通过RX_CTL传送

- 1 Gbit/s速率下,时钟频率为125MHz

- 100 Mbit/s速率下,时钟频率为25MHz

- 10 Mbit/s速率下,时钟频率为2.5MHz

3.5 SMII

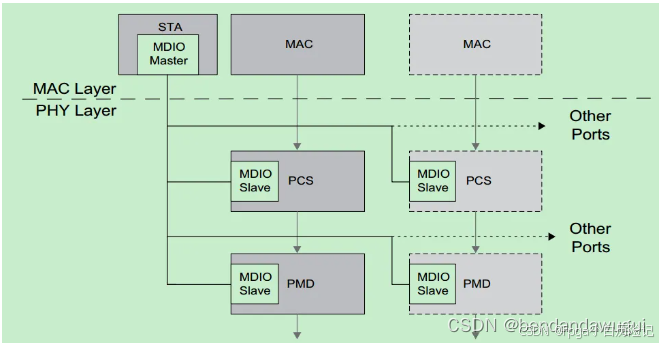

SMI:串行管理接口(Serial Management Interface),通常直接被称为MDIO接口(Management Data Input/Output Interface)。

MDIO最早在IEEE 802.3的第22卷定义,后来在第45卷又定义了增强版本的MDIO,其主要被应用于以太网的MAC和PHY层之间,用于MAC层器件通过读写寄存器来实现对PHY层器件的操作与管理。

MDIO主机(即产生MDC时钟的设备)通常被称为STA(Station Management Entity),而MDIO从机通常被称为MMD(MDIO Management Device)。通常STA都是MAC层器件的一部分,而MMD则是PHY层器件的一部分。

MDIO接口包括两条线,MDIO和MDC,其中MDIO是双向数据线,而MDC是由STA驱动的时钟线。MDC时钟的最高速率一般为2.5MHz,MDC也可以是非固定频率,甚至可以是非周期的。

MDIO接口只是会在MDC时钟的上升沿进行采样,而并不在意MDC时钟的频率(类似于I2C接口)。如下图所示。

转载:https://blog.youkuaiyun.com/dongdongnihao_/article/details/137061601

四、总结

在做千兆网的时候,FPGA通常采用两种外界接口。

1、一种就是普通接口MII/RMII/GMII/RGMII这些接口,RGMII是最常用的接口,这些接口都属于低速接口。例如上边介绍的ZYNQ的PS端以太网和三速以太网Tri Mode Ethernet MAC IP核这两种都是使用RGMII,与外部PHY芯片进行连接,然后再通过网口。即:FPGA=MAC<–>PHY<–>RG45。

2、还有一种就是采用高速收发器即GT接口作为外接接口,外部接的是TXP/TXN和RXP/RXN这种串型接口,上边普通的采用的是并行接口。GT用于千兆以太网物理编码子层/物理介质连接子层 (Physical Coding Sublayer/Physical Media Dependent PCS/PMA)。(本次学习的框架就是第二种方法)

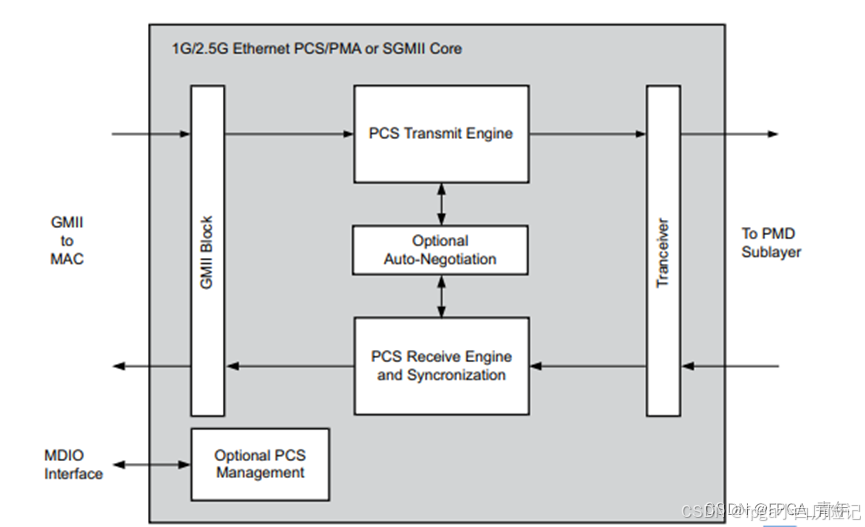

例如本次使用的1G/2.5G Ethernet PCS/PMA or SGMII IP核。这个IP是将PHY芯片的的PMA层和PCS层集合到了FPGA中。即FPGA=MAC+ PCS / PMA。

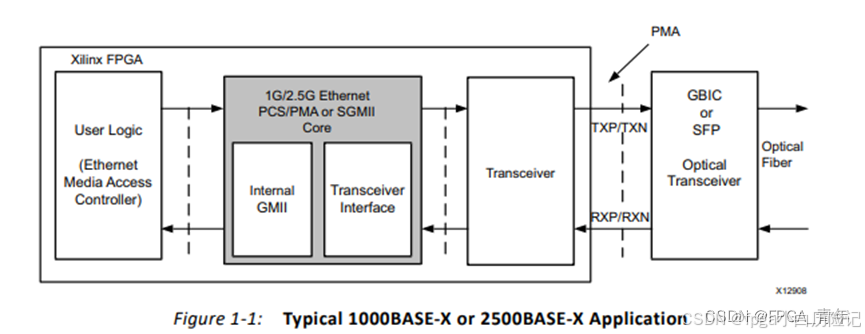

(1)当采用1000BASEX时候,IP核作为PCS层(编码)+PMA层(并转串),通过收发器向PMD发送,此时FPGA与外部千兆接口转换器 (GBIC) 或小型可插拔 (SFP) 光收发器进行连接。如下图所示:

(2)当采用SGMII时候,IP核作为PCS层,通过收发器向PHY芯片的PCS层发送,此时FPGA与现成以太网PHY设备(RJ-45电口)进行连接。如下图所示:

在所学习的设计中,需要将 Tri Mode Ethernet MAC 与 1G/2.5G Ethernet PCS/PMA or SGMII 之间通过GMII 接口互联。

7788

7788

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?