在同步数字集成电路中,时钟信号如同人体的心跳,为所有寄存器提供同步节拍。时钟树综合(Clock Tree Synthesis, CTS)作为后端物理设计的核心环节,负责构建高效的时钟网络,确保信号同步传输,直接决定芯片的性能、功耗和可靠性。本文将深入解析CTS的原理、流程与实战要点,助您掌握这一关键技术。

一、什么是CTS?为何需要时钟树综合(CTS)?

时钟树综合(Clock Tree Synthesis, CTS)是数字集成电路物理设计中的关键环节,指通过插入缓冲器(Buffer)或反相器(Inverter)构建时钟信号传输网络的过程。其核心目标是确保时钟信号从源端(如PLL或时钟端口)同步到达所有时序单元(寄存器、锁存器等),消除因物理路径差异导致的时序偏差。

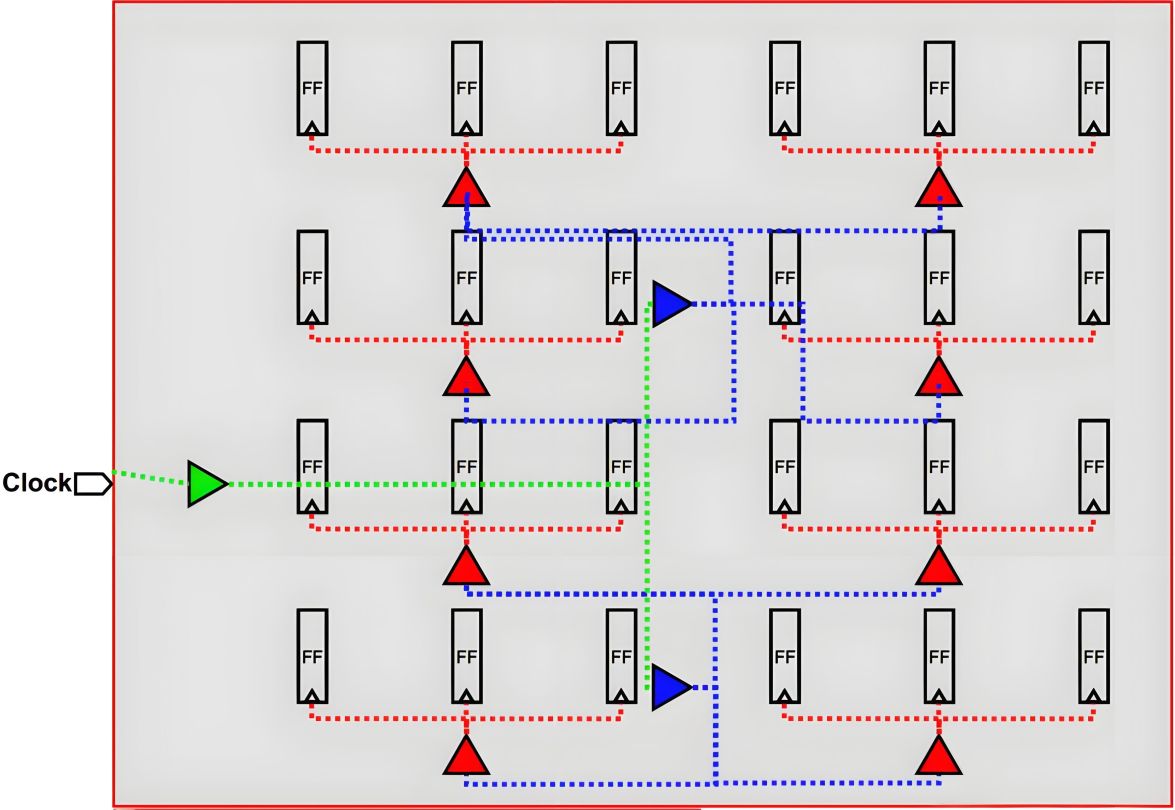

在未进行CTS之前,时钟信号从源端(如PLL输出)直接扇出到成千上万的寄存器时钟端。由于路径负载和驱动差异,时钟到达不同寄存器的时间存在偏差(Skew),可能导致时序违例和功能错误。CTS通过插入缓冲器(Buffer)或反相器(Inverter)构建树状网络,平衡时钟路径,实现“零偏差”目标。

二、CTS的三大核心目标:偏差、延迟与功耗的平衡艺术

1. 最小化时钟偏差(Skew)

时钟偏差指同一时钟到达不同寄存器的时间差,分为局部偏差(相关寄存器间)和全局偏差(任意寄存器间)。局部偏差直接影响时序路径的余量。例如,若发射寄存器时钟早于捕获寄存器,可能导致保持时间违例。CTS的目标是通过平衡布线长度和驱动强度,将偏差控制在工艺允许范围内。

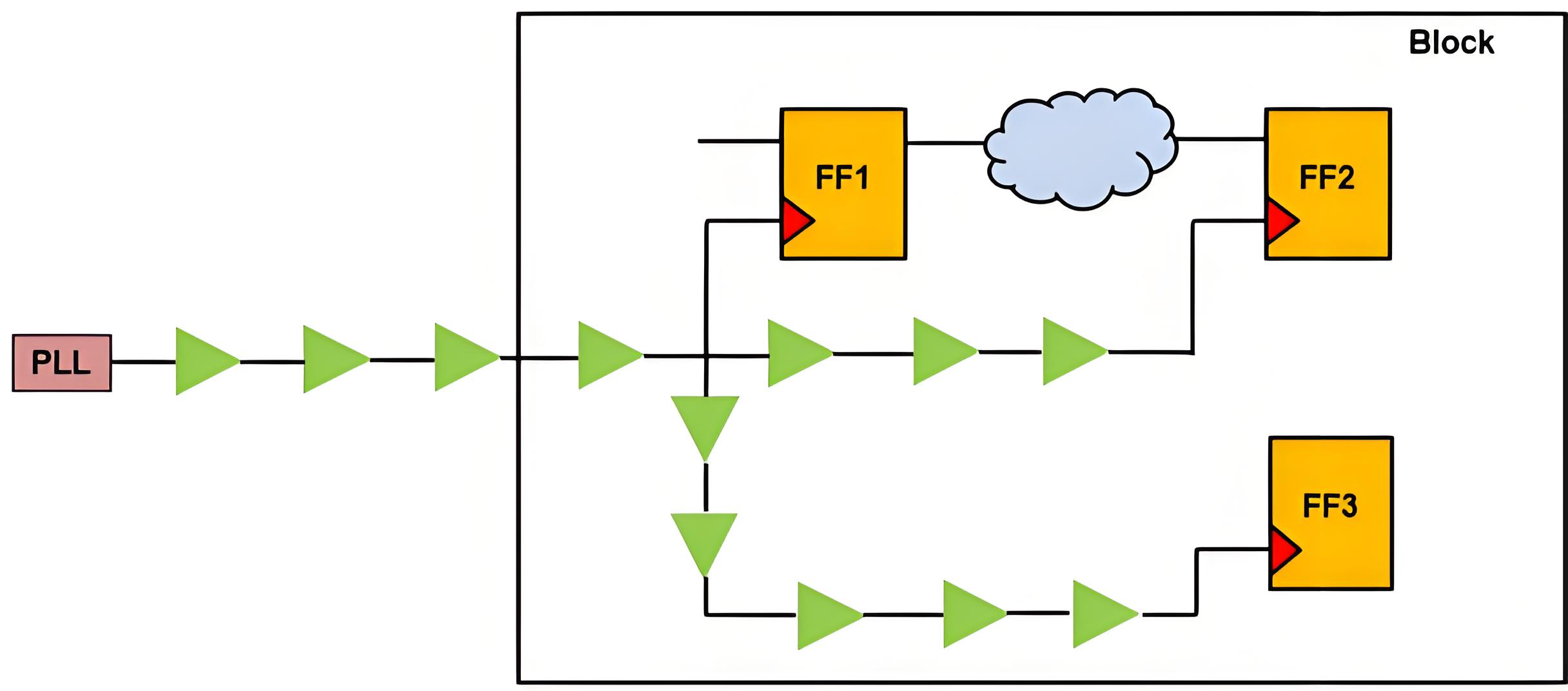

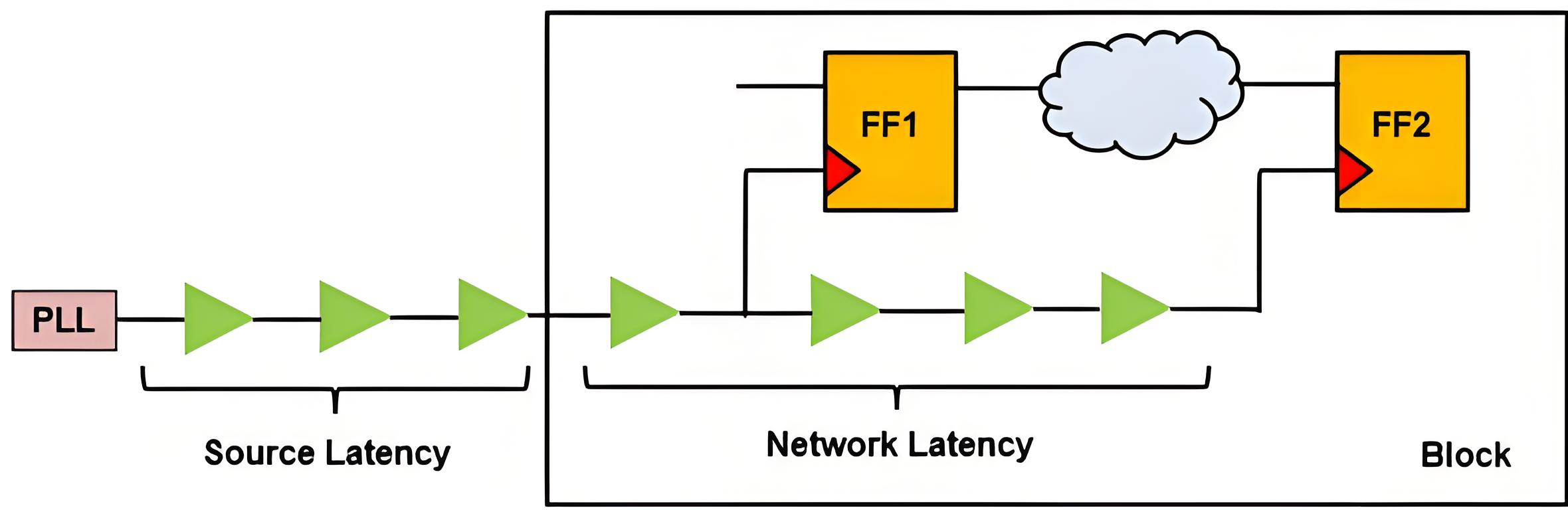

2. 优化时钟延迟(Latency)

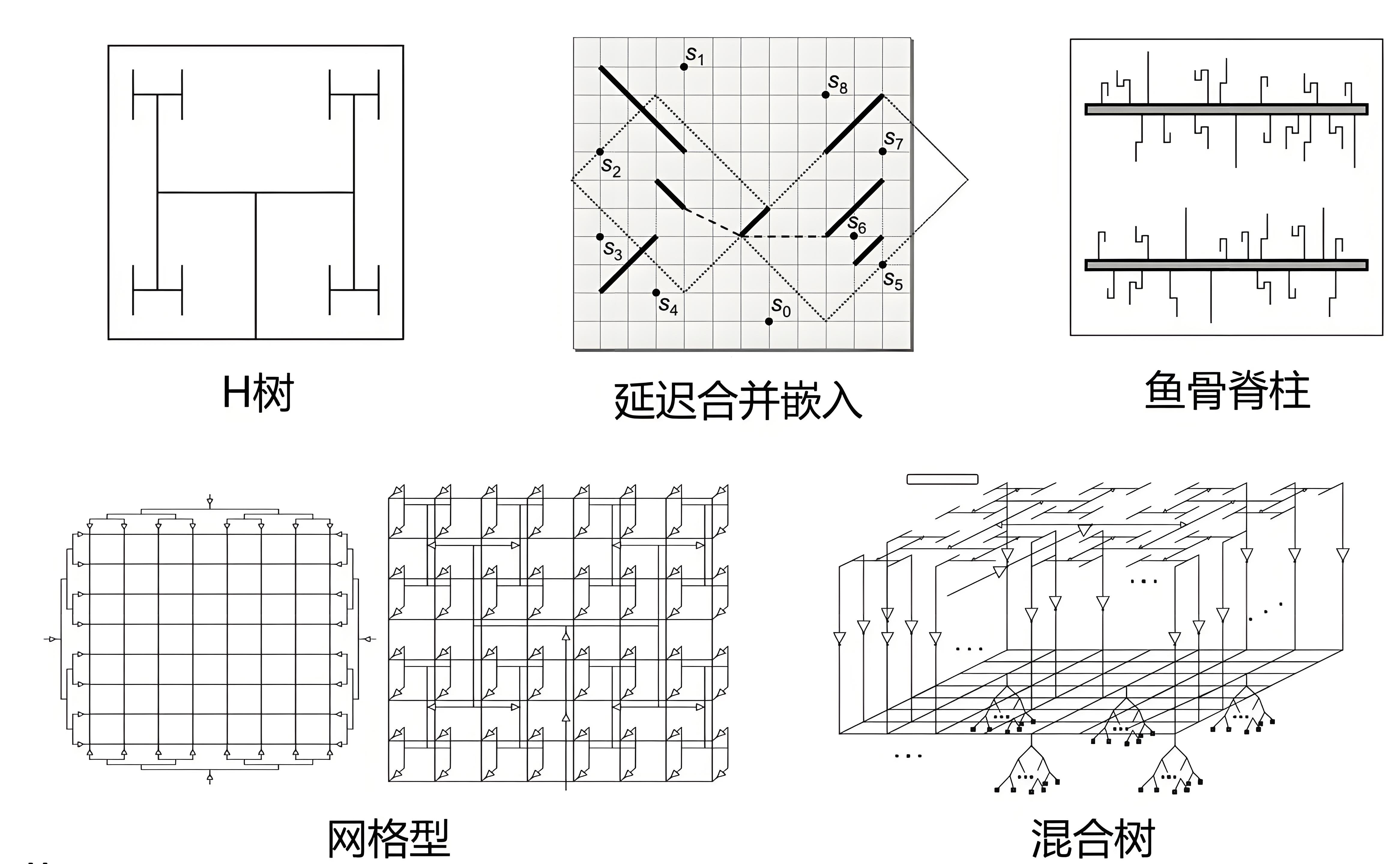

时钟延迟包括源延迟(芯片外部到时钟根节点)和网络延迟(根节点到叶节点)。过大的延迟会限制电路最高频率。例如,在高频设计中,需通过H树拓扑或时钟网格缩短关键路径延迟。

3. 控制时钟功耗

时钟网络动态功耗可占芯片总功耗的30%-40%。CTS中需采用时钟门控(ICG)、多比特寄存器等技术降低功耗。例如,通过精细门控关闭空闲模块时钟,或使用多比特寄存器减少时钟引脚电容。

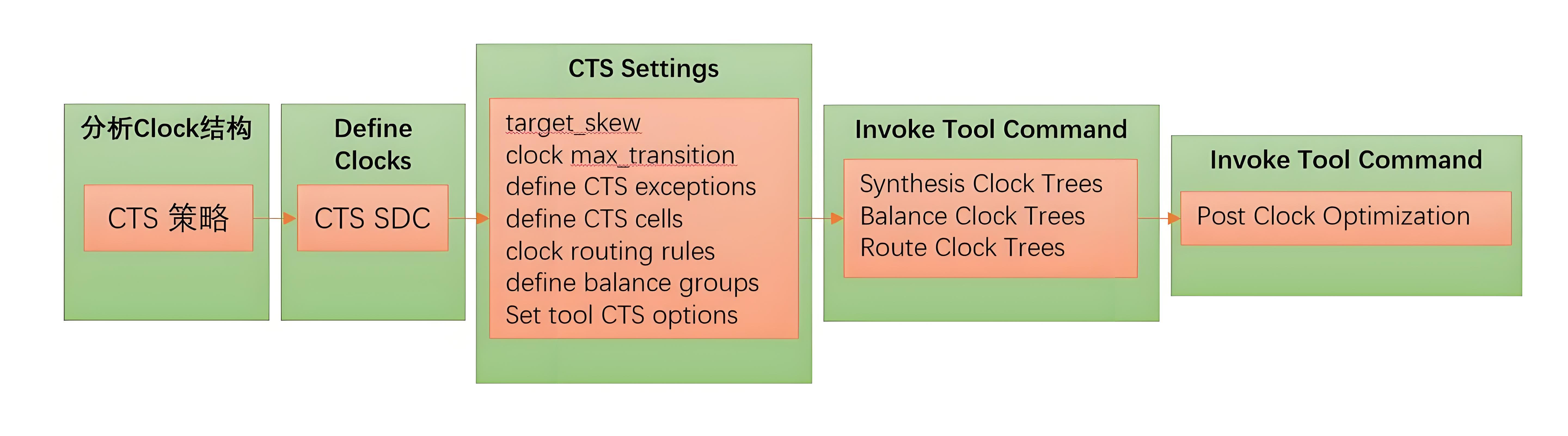

三、CTS全流程分解:从约束到优化的关键步骤

1. 预CTS设置:时钟定义与约束

时钟定义:使用create_clock定义主时钟,create_generated_clock定义分频时钟。需明确相位关系,避免分析错误。例如,二分频时钟若定义不当,可能导致上升沿对齐错误。

物理规划:预留中层金属(如M4-M5)用于时钟布线,设置非默认规则(NDR)如双倍线宽屏蔽串扰。

约束加载:读入SDC文件,设置时钟不确定性、插入延迟等参数。

2. 时钟树综合执行

拓扑构建:工具从叶节点回溯,插入缓冲器(如cts_buf)或反相器(如cts_inv),分解高扇出网络。例如,将直接驱动100个寄存器的路径改为多级缓冲结构。

偏差优化:通过算法(如延迟合并嵌入)平衡子树延迟,控制局部偏差。工具会报告全局偏差(Max Skew)和插入延迟(Insertion Delay)。

3. 后CTS优化与验证

DRC修复:解决最大过渡时间、电容违例。例如,替换驱动能力不足的缓冲器。

时序验证:使用report_clock_timing检查建立/保持时间余量,并分析时钟抖动(Jitter)影响。

四、架构选择:单点、网格与多源CTS的实战抉择

1. 单点CTS

适用场景:多时钟域中低频设计(如IoT芯片)。

优点:功耗低,布线资源占用少。

缺点:OCV(片上变异)惩罚大,偏差控制能力弱。

2. 时钟网格(Clock Mesh)

适用场景:高频单时钟域(如CPU/GPU)。

优点:偏差极小(可达ps级),抗工艺变异能力强。

缺点:功耗高,需大量金属资源。

3. 多源CTS(MS-CTS)

适用场景:复杂SoC,需平衡偏差与功耗。

实现方式:分区构建子时钟树,通过H树连接。共同路径长,OCV惩罚适中。

五、常见问题与调试指南:从日志分析到根因定位

问题1:时钟树未综合

现象:部分寄存器时钟端存在巨大过渡时间违例。

根因:时钟定义遗漏或dont_touch属性误设。

解决:检查SDC完整性,使用ICC2的report_clock_gor -type structure追溯未综合节点。

问题2:延迟过长

现象:时钟延迟超预期,限制频率提升。

根因:缓冲器尺寸过小或布线层选择不当。

解决:替换高驱动能力单元,优化布线规则。

问题3:串扰噪声

现象:时钟信号抖动增大。

解决:设置屏蔽层(Shielding)或物理独占性约束,减少悲观分析。

六、前沿趋势与最佳实践:迈向7nm以下的CTS挑战

1. AI驱动优化

机器学习模型预测路径延迟,自动调整缓冲器布局,提升CTS效率。

2. 低功耗技术

电压频率缩放:动态调整时钟域电压,优化能效。

3D集成:跨芯片时钟同步方案,减少板级偏差。

3. 设计建议

器件选择:优先使用反相器(非缓冲器)减少占空比失真。

早期规划:结合Floorplan对称摆放时钟逻辑,避免热点集中。

结语:CTS——精准时序的基石

时钟树综合不仅是工具流程,更是设计策略的体现。从架构选择到偏差控制,每一步都需权衡PPA目标。随着工艺进入3nm以下,CTS需与签收工具(如PrimeTime)深度融合,实现时序、功耗与可靠性的协同优化。掌握CTS,方能驾驭芯片设计的“心跳”,打造高性能、低功耗的集成电路。

2105

2105

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?