国际电路理论与应用杂志Int. J. Circ. Theor. Appl.(2016) 在威利在线图书馆 (wileyonlinelibrary.com) 上在线发布。DOI: 10.1002/cta.2293

特刊论文

密码算法中用于GCD计算的可逆电路设计

H. V. 贾亚什里*,†,斯坎达·科泰托塔 和 V. K. 阿格拉瓦尔

PES理工学院,班加罗尔,印度

摘要

密码算法的实现不断面临多种技术对安全系统的威胁。目前破解密码安全系统的趋势是采用功耗分析技术。为了破解安全密钥,黑客会测量数字电路在计算过程中消耗的能量。这种技术通常被称为差分功耗分析,被广泛用于攻击安全系统。为避免此类攻击,有必要探索能够消耗更少能量的不同设计。理想情况下,可逆电路不消耗能量。我们提出了一种基于改进的二进制最大公约数算法的可逆最大公约数(GCD)计算架构。我们提出了可逆GCD计算单元的通用设计方法。我们将所提出的GCD计算设计与现有设计进行了比较。与文献中现有的GCD架构相比,所提出的可逆GCD架构所需的迭代次数更少。在量子代价、门数量和辅助输入方面,所提出的设计优于现有的GCD设计。版权所有 © 2016 John Wiley & Sons, Ltd。

收到日期:5月15日y2016;2016年10月20日修订;2016年10月23日接受er 2016

关键词

:最大公约数;可逆;密码学;托佛利;弗雷德金

引言

密码系统(例如基于椭圆曲线的密码系统、RSA密码系统)因其在移动设备、智能卡等便携式设备中的广泛应用而受到欢迎。在这些密码系统中,通过观察密码算法执行过程中不同阶段的功耗轨迹,可以确定密码设备的特征以及密码算法中使用的安全密钥。这种技术通常被称为差分功耗分析技术,用于攻击密码系统。最大公约数(GCD)与标准ALU操作一样,在许多领域都有应用。在密码学[1],中,它被用于多种对称密钥算法。在模运算[1],中,它被用于计算机代数或计算机科学中的位运算、编程语言中的取模运算、误差控制编码中的校验和计算等。在秀尔算法[2],中,它有助于整数分解的计算。因此,最大公约数计算由于在众多领域的广泛应用,成为现代数学中最重要的工具之一。密码算法中最重要且基本的需求是因式分解,而因式分解又依赖于最大公约数的计算。目前已有一些研究提出利用可逆逻辑门进行密码算法电路设计,以缓解功耗分析攻击[3, 4]。这些论文中提出的工作明确指出了使用可逆逻辑设计密码算法的优势。在文献中,使用可逆逻辑设计密码算法已取得显著进展,但可逆GCD电路设计却鲜有报道。在本研究中,我们提出了可逆GCD计算单元的设计,这将有助于缓解差分功耗分析攻击。从朗道尔的

通讯作者:H. V. 贾亚什里,电子与通信工程系,PES理工学院,班加罗尔,卡纳塔克邦,印度

†电子邮件: j a y ashreehv@ p es.edu

版权所有 © 2016 John Wiley & Sons, Ltd.

本文档由 funstory.ai 的开源 PDF 翻译库 BabelDOC v0.5.10 (http://yadt.io) 翻译,本仓库正在积极的建设当中,欢迎 star 和关注。

H. V. 贾亚什里, S. 科特索塔 和 V. 阿格拉瓦尔

根据摩尔定律,据指出[5]假设一台计算机(不可逆)擦除单个比特的信息,则每次逻辑操作至少会向环境中耗散KBTln2的能量(KB为玻尔兹曼常数,T为计算机所处环境的温度)。

另一方面,摩尔定律指出芯片中的晶体管数量每18个月将翻一番;因此,如果在采用不可逆门的芯片设计中继续遵循摩尔定律,则发热量将会增加。为解决这一问题,IBM的本内特[6]提出了可逆计算的概念,以规避不可逆计算中的功耗问题。在可逆逻辑中,由于输入与输出之间存在唯一的单射映射关系,因此可以从输出恢复输入。文献[7]中的研究显示,构建密钥相关的可逆逻辑电路不仅适用于数据加扰函数,还可用于构造一种新型通用的面向硬件的分组密码以及相应的密钥扩展算法。此外,通过在逻辑门级应用掩码技术,可以有效保护所得到的硬件设计免受功耗分析攻击。最大公约数计算单元的可逆电路在使用可逆逻辑门实现密码算法方面具有应用价值。最大公约数计算模块的应用已在[8],中讨论的混合模式数字视频转码方法以及[9]中的配对密文密码算法用于有效密钥分发方面得到了充分展示。文献[10]中的工作旨在获得抗功耗攻击电路。为实现这一目标,该设计基于蒙哥马利幂阶梯、进位保存公共被乘数蒙哥马利模乘法以及最大公约数计算单元。文献中存在多种高效的GCD算法,例如肖恩哈格算法、次二次整数最大公约数计算[11],以及整数最大公约数并行算法[12]。我们的设计重点是二进制最大公约数算法[13],并进行了少量修改,讨论了最大公约数计算所需的基本构建模块。这些相同的基本构建模块可用于实现不同的最大公约数计算算法。

本文中,我们提出了使用可逆逻辑门设计用于计算两个无符号数最大公约数(GCD)的各个组件的设计方法。本文结构分为多个部分:第2节介绍可逆逻辑门和优化参数的基础知识;第3节讨论GCD设计的现有实现;第4节详细阐述所采用的算法以及提出的设计的结构顶层视图;第5节说明各组件的设计步骤和性能参数;第6节列出结果与比较;第7节对本文提出的工作进行总结。

2. 可逆逻辑门

可逆门是一种能够根据唯一的输入向量生成唯一输出向量的门。可逆逻辑要求输出的数量等于输入的数量。因此,可逆门表示为n × n门。可逆门的扇出不能大于一[14]。可逆门中不允许存在环路或反馈。本文第2.2节将对部分可逆门进行介绍。

2.1.优化参数

可逆逻辑电路设计与综合中的重要电路指标或优化参数[15]如下所列:

-

辅助输入

:电路中保持恒定(即始终为0或1)的输入称为辅助输入。这些输入有助于重新配置可逆门的输出函数。

-

门数量

:电路中使用的可逆门的数量即为该电路的门数量。

-

量子代价

:一个设计的量子代价是其设计中所使用的 1 × 1和 2 × 2可逆门的数量。

-

垃圾输出

:电路中不期望且对电路无用的输出称为垃圾输出。在输出端再生的输入不被视为垃圾输出 [16]。这些输出仅用于维持一一映射。

-

逻辑深度

:电路中最长路径(关键路径)中可逆门的最大数量即为逻辑深度。逻辑延迟是该最长路径中可逆门量子代价的总和。

2.2.用于最大公约数电路设计的可逆门

在提出的设计中使用的一些最常见可逆门如表I所示。这些包括费曼门[17],托佛利门[18], BJN门[19], TR门[20],弗雷德金门[21], UPG门[22],和改进型TR门。改进型TR门是本工作引入的。在TR门的第二输出线上放置一个非门以得到A ⊕B。因此,改进型TR门的量子代价将为1+ TR门的量子代价。

3. 现有工作

少数作者提出了用于实现最大公约数算法的可逆设计,但其适用性有限,因为这些设计不具备可扩展性。作为对比,我们参考了[23]中提出的结果。我们发现,该文作者为最大公约数计算所需的每个组件提供了通用的设计方法。[23]中的设计在每次计算后会清除辅助位,而[24]则不会。

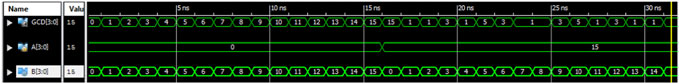

此外,在现有工作中,执行计算所需的迭代次数大于本文所提出设计中的迭代次数(参见表II和表III以比较迭代次数,图1以查看电路结构)。我们还发现,当其中一个输入为零时,作者提出的架构将无法成功计算最大公约数。作者在某些设计组件中使用了[25]中提出的现有设计。我们验证了作者提出的方法[23],并发现它需要更多的迭代次数,而不像n次迭代那样如作者所述即可获得结果(表II中所示示例对于4位输入需要超过四次的迭代)。

4. BEH用于最大公约数计算的行为模型与可逆电路设计

本节介绍了改进的二进制最大公约数算法在较高抽象层次上的行为和结构模型。在后续章节中,将对每个组件的设计进行详细讨论。

H. V. 贾亚什里, S. 科特索塔 和 V. 阿格拉瓦尔

4.1.改进的二进制最大公约数算法

算法1通过修改[13]中给出的步骤,将求(A,B)的最大公约数问题进行简化。本文提出的改进的二进制最大公约数算法用于计算两个非负数A和B的最大公约数,其中n ≥3;其中n表示用于表示输入数字的位数。

表III通过一个示例说明了该算法。在第四次迭代后,A= 2和B= 3。然后检查(A ≠ 0)⋅(A ≠ B)的逻辑电平。由于该逻辑电平为真,因此取 B的最终值为1。因为在所有迭代中,A和B从未同时为偶数,所以k[i]在所有迭代中保持为零。因此,不执行左移操作,最终得到的结果为1。从这个示例可以明显看出,本工作所采用的方法相比现有工作[23]所需的迭代次数更少。我们对算法进行了建模,并针对n位数据进行了验证;结果表明,该方法需要2n− 4次迭代才能得到输出。

4.2.二进制最大公约数计算的顶层结构设计

在本节中,我们对二进制最大公约数计算单元的结构模块进行功能描述。我们将最大公约数计算单元的功能框图分为三个图,如图2所示。使用第4.1节中提到的改进的二进制最大公约数算法进行最大公约数计算时,建模为两个迭代阶段和一个非迭代阶段。

迭代阶段

:以下描述中给出了每个模块的功能说明。简要解释了迭代阶段中每个结构模块的功能。此阶段中的模块将执行2n− 4次迭代。

(1) %2 和 /2 模块:A%2(B%2)模块检查A(B)是否为偶数。如果结果为真,则使用 ∕2模块将 A(B)除以 2,否则数据不作修改直接传递。计算完成后,输出将指示 A为偶数(B为偶数)以及根据奇偶性调整后的 A(B) 数据。由于不存在数据依赖关系,数据A和数据 B的计算是并行进行的。

(2) A< B模块:此处采用串行比较技术计算A< B。该模块的输入在计算后被再生。该模块的第三(最后)行在A线路上的数据小于B线路上的数据时输出高电平;否则输出低电平。

(3) CSWAP模块:该模块(表示为带负控制的弗雷德金门)根据前一模块得到的输出A< B来交换A和B线路上的数据。该电路保持较大的线路B上的值较大,线路A上的值较小。如果线路A<线路B成立,则数据将不做任何修改地传递到CSWAP模块的输出线。

(4) CSUB:条件减法(仅当两个输入均为奇数时进行减法运算)。此处,设fL为两个数中较大的数,f S为较小的数。前一个模块输出的fL作为第一条输入线,f S作为第二条输入线。完成减法计算后,fL线上将输出f S,f S线上将输出差值;否则,fL,f S上的数据将保持不变,分别传递至该CSUB模块输出端对应的fL和f S线上。

(5) /2:当 A 和 B 输入线上的输入均为奇数时,从 CSUB 模块得到的差值Di 除以 2;否则,该模块输入线上的数据不作修改地传递到输出线。

非迭代阶段

:此结构的前两个输入(从上往下)来自迭代阶段的前两条输出线(从上往下)。该阶段中的模块仅执行一次。该模块的输入将在上一阶段所有迭代完成后提供。

(1) A ≠ 0:检查线路 A上的数据是否为非零。该模块生成两个输出。其中一个输出线将保持A线上的数据不变;另一条输出线通过将线路驱动至逻辑高电平来表示A非零,否则为低电平。

(2) A ≠ B:最后一个辅助输入线将保持A不等于B的输出结果,即当A不等于B时为高电平,否则为低电平。该模块的其他输出将再生出线路 A和线路 B上的数据。

(3) 条件选择:如果A ≠ 0且A ≠ B,则CSEL‐out将在B线上输出1(00..0001);否则,将保留B线上的先前数据。

最终迭代阶段

:该阶段的模块从非迭代阶段和迭代阶段获取输入。来自非迭代阶段的输出线 CSEL‐out以及来自迭代阶段的输出线B‐even和A‐even被作为输入提供给此模块。

(1) X2模块:如果对应于同一迭代的B偶数和A偶数线路均为高电平,则CSEL‐out线路上的数据将向左有条件地移动2n‐4次。

5. 可逆最大公约数组件的设计与性能参数计算

在本节中,我们介绍了针对n位输入数据宽度的设计方法和性能参数。对于偶数和奇数数据宽度的性能参数估计已列于表格中。符号⌊⌋和 ⌈⌉分别表示向下取整和向上取整。

5.1.可逆电路设计:A%2(B%2)和 /2

二进制数 A(B) 如果最低有效位为零,则该数为偶数。这需要使用一个费曼门和一个辅助输入位来指示输出是偶数还是奇数。此计算之后是一个条件除以2模块,该模块通过循环右移操作实现。该设计基于公式1和2。为了说明目的,图3展示了对于奇数和偶数数据位的移位操作。

$$ fi= B‘0 \cdot Bi+1+ B i \cdot B0 \quad 0 ≤i ≤ n− 2 $$ (1)

$$ fi = B 0 \cdot Bn−1 \quad i= n− 1 $$ (2)

输出。再生阶段增加了门数量和量子代价。由于这些组件被迭代重用,因此有必要再生辅助位;这反过来减少了垃圾输出。此处针对输入数据位B的解释,对于输入数据位A同样适用。

5.1.1./2可逆电路的性能参数计算

本节包含对%2, /2电路性能参数的详细计算。

阶段 a

:此处使用CNOT门生成偶数或奇数校验输出位。这些位在阶段 b中用于交换数据位。本阶段使用的CNOT门数量为 n/2(当n为奇数时为(n−1)∕2)。CNOT门的连接方式为部分串行和部分并行。通过实验评估,当n为偶数时,延迟计算为 ⌈log2n⌉。

阶段b

:阶段 b的逻辑深度为 ⌈log2n⌉。在阶段 b的每一步中,并行运行的弗雷德金门利用阶段 a中CNOT门的目标位来控制交换操作。本阶段所需的最大弗雷德金门数量为 n − 1。

stagec

:CNOT门序列以与阶段a镜像的方式运行,以再生辅助位。在此阶段,仅第一个CNOT门不会重新执行,因为在设计的后续阶段我们需要 ∼ B0。CNOT门的数量比阶段a的CNOT门数量少一个。

所有性能参数的摘要列于表IV中。参数“消耗的辅助输入”表示未被再生的辅助位的数量。

5.2.可逆电路设计:A小于 B

文献中存在多种用于比较两个数的设计。现有文献中的比较器设计能够提供所有比较输出(A> B、A< B 和 A= B),并再生任一输入。本文所设计的电路根据最大公约数架构的需求,需要再生两个输入,并仅生成单一输出信号A< B。本工作为A< B所提出的电路设计仅生成A< B输出信号,并再生两个输入数据(A和 B线上的数据)。该模块的设计被划分为多个阶段。为了更清晰地说明,各阶段如图5所示。在阶段A和B线上数据的相等性检查于阶段a完成。随后在阶段b执行小于计算步骤。在阶段c,我们获得所需的输出A< B。之后是再生阶段,用于将辅助位重置为其初始值,即再生辅助位以及输入A和B。

$$ Ei= Ai ⊕ Bi \quad for \quad 0 ≤i ≤ n− 1 $$ (3)

$$ A< B=(An−1 ⋅Bn−1)⊕(En−1 ⋅An−2 ⋅Bn−2)⊕(En−1 ⋅En−2An−3 ⋅Bn−3)⊕· · · $$ (4)

5.2.1. A小于 B电路的性能参数

本节涵盖 A< B 电路的性能参数估计。用于评估 A< B 信号的可逆门包括改进型TR门、UPG门、托佛利门、费曼门和非门。各阶段的性能参数计算如下。

阶段a:此阶段包含并行运行的改进型TR门,用于检查 A< B 和 A= B,针对 A 和 B 线路上数据的每一位。该计算共涉及 n 个改进型TR门。所使用的辅助输入位数量为 n。由于本阶段中所有门均并行执行,因此逻辑深度为1,延迟等于5(改进型TR门的量子延迟)。

阶段b:该阶段通过串行运行的UPG门对连续的比特对评估小于条件。图5中的表达式阐明了计算步骤。该计算共使用了n− 2个UPG门。从图5可以看出,UPG门未放置在 0th和(n − 1)th条比特线上。该阶段的逻辑深度包含n − 2个UPG门。

stage c:这是 A< B计算过程的最后一步。此阶段仅需一个托佛利门,因此门数量和逻辑深度均等于1。

stage d和 e:阶段 d 是阶段 b 的镜像。其逻辑深度和门数量与阶段 b 所得值相同。阶段 e 除 (n − 1)th 行外,是阶段 a 的镜像。使用非门和CNOT门在该模块的 (n − 1)th 行上再生输入。逻辑深度等于 2,但延迟为该阶段的最大延迟,即相当于改进型TR门的量子延迟(5)。

性能参数估计的摘要见表V。

5.3.可逆电路设计:条件交换

该电路需要保持较大的值在B线路上,较小的值在A线路上。为了表示这一点,在图6中将输出线标记为fL和f S。C线是控制线,它来自前一个设计模块扩展的A< B线。如果C为0,即如果A> B或A= B,则线路A和B上的数据将进行交换。该电路基于公式5和公式6进行设计。

$$ fLi= C ⋅Ai+ C ⋅Bi \quad for \quad 0 ≤i ≤ n− 1 $$ (5)

$$ f Si= C ⋅Bi+ C ⋅Ai \quad for \quad 0 ≤i ≤ n− 1 $$ (6)

5.3.1.条件交换电路的性能参数

图6所示的设计被划分为三个阶段,即阶段a、阶段b和阶段 c。性能参数的摘要列于表VI。

阶段a:此阶段由费曼(CNOT)门组成,用于复制控制线C。需要复制控制线以实现并行的交换操作。此步骤需要n − 1个CNOT门和一个非门。所需的常量或辅助输入为n − 1。该步骤计算操作的逻辑深度为 1+ ⌈log2n⌉。

阶段b:此阶段需要并行运行的弗雷德金门,根据控制输入C来交换A和B线路上的数据。本阶段包含n个弗雷德金门。由于所有弗雷德金门并行计算,该阶段的逻辑深度为1。

阶段c:此阶段是阶段 a 的镜像。它利用 CNOT门 和 非门 来再生辅助输入位。这是为了减少垃圾位并重用辅助位所必需的。门数量和逻辑深度与阶段 a 的值相同。

5.4.可逆电路设计:控制线生成

该模块需要一个UPG门和一个非门来生成输出线,以指示A和B线上的数据是否均为奇数。如图 7所示。该门的输入是A%2= 0(设为C1)和B%2= 0(设为C2)模块的输出线,用于指示A(B)是偶数还是奇数。该阶段的输出由out1和out2表示。当A和B线上的数据均为奇数时,out1线变为高电平。当A和B线上的数据均为偶数时,out2线变为高电平。输出线out1和out2通过UPG门和非门的功能表达式得出,如公式7和8所示。第一条输出线是一个由g表示的垃圾位。

$$ out1= C1+ C2 $$ (7)

$$ out2= C1 ⋅ C2 $$ (8)

5.4.1.控制线生成电路的性能参数

控制线生成的计算仅需要两个门电路,即UPG和非门。性能参数的摘要列于表VII。

5.5.可逆电路设计:条件减法电路

该模块的数据输入来自CSWAP模块(fL和f S)以及控制生成模块的out1线,该控制线用于指示线路A和线路B上的数据均为奇数。如果控制线(out1)为高电平,则该模块将对前一个模块中线路B和线路A上的数据(即分别为fL和f S)执行减法操作。计算完成后,fL线将保留较小的数,而f S线将保留差值。条件减法采用串行进位技术实现。减法的串行计算基于公式9和10进行。为了更清晰地说明,设计被划分为若干阶段,如图8所示。阶段a包含CNOT门,用于生成控制位out1的副本。阶段b的计算由托佛利门、非门和费曼门组成,用于生成半减法结果,即计算仅考虑被减数和减数。差值(Di)的完整计算以及较小的数的再生将在阶段c中完成。减法结果将出现在fL线上,较小的数将在f S线上被再生。在阶段d中,将使用弗雷德金门执行条件交换操作。此交换操作是为了将差值结果获取到f S线(A线)上。最后一个阶段e是阶段a的镜像,用于再生辅助位。此处,我们采用二的补码方法来计算A和B之间的减法。该操作之后将执行条件交换操作。差值计算使用通用公式10进行,并根据该电路的输入修改为公式11所示形式。

$$ C−1= 1 $$ (9)

$$ Di=(Ai ⊕ Ci−1) ⋅ Control⊕ Bi \quad for \quad 0 ≤i ≤ n− 1 $$ (10)

$$ Di=(f Si ⊕ Ci−1) ⋅ out1 ⊕fLi \quad for \quad 0 ≤i ≤ n− 1 $$ (11)

5.5.1.条件减法电路的性能参数

此处针对条件减法电路的每个阶段解释了性能参数,相关内容总结于表VIII中。

阶段a:在此阶段,生成控制位out1的副本。该阶段包含n − 1个CNOT门。

阶段b:该阶段包含CNOT门、非门和托佛利门,用于计算半减法。它需要2n −1托佛利门,1 个 CNOT门,1个非门,和n非门。

阶段c:该阶段包含6n−10个托佛利门、2n −1个CNOT门和n个非门,用于生成Dii(差值)并再生较小的数(f Si)。

阶段 d:该阶段由弗雷德金门组成。当控制位(out1)为高电平时,需要n个弗雷德金门来交换 fS线 和 fL线 上存在的数据。

stagee:此阶段是阶段a的镜像,其中一系列CNOT门被重新运行。此阶段需要n − 1个CNOT门。

5.6.可逆电路设计:条件/2模块

fS线(参考图8)或图2中的A线来自前一模块的数据是/2模块的数据输入,控制输入为图7中的out1。此处仅当out1为高电平时才执行除法操作(回忆:out1表示两个输入均为奇数)。该模块的结构类似于图4所示设计,但不包括第一个CNOT门,并且辅助位1被out1位取代。

5.7.可逆电路设计:非零块

非零块(图2中的A NON A ≠ 0块)的设计包含UPG门和BJN门。该模块通过对此模块的输入位执行或运算来实现。此处给出了该设计所依据的简单方程。

$$ fA≠0 = A0+ A1+ A2+…+ An−1 $$ (12)

图9所示的设计步骤清晰地展示了电路如何逐阶段演化。阶段a由UPG门组成,这些门将对输入的连续两个数据位执行或运算,所需输出位于UPG门的第二输出端。此步骤中的门并行执行。在阶段b中,对阶段a中两个连续UPG门的结果执行或运算。为了完成对所有位的或运算,阶段b需对每对连续位进行多次迭代的或运算,直到完成n −2(n −1对于奇数n)位为止。在每个迭代步骤中,UPG门串行地进行计算。在阶段c中,使用BJN门产生最终输出f A≠0;该信号由BJN门的第三输出线计算得到。阶段d和阶段e分别是阶段b和阶段a的镜像,用于再生该模块的输入和辅助输入位。当该模块的数据输入为非零时,则f A≠ 0线变高,否则变低。该模块的数据输入和辅助输入位在输出端被再生,但最后一个辅助位(用于保持f A≠ 0)除外。

5.7.1.可逆非零电路的性能参数

本节涵盖图9所示每个阶段的性能参数计算。性能参数汇总见表IX。

stage d和 stage e:这些阶段的计算涉及 stage b和 stage a中计算的镜像。我们探索了使用BJN门的串联来计算f A≠0的另一种方案。我们发现,提出的设计所获得的性能参数优于前者。

5.8.可逆电路设计:A不等于B电路

图10所示的设计在阶段a包含CNOT门,在阶段b包含UPG门,在阶段c包含BJN门。阶段d是阶段b的镜像,阶段e是阶段a的镜像。相等性检查的计算在阶段a中通过为每个比特对并行运行的CNOT门来完成。在此,线路A上数据的每一位都会与线路B上对应位的数据进行相等性检查。阶段b将包含或运算的迭代;该步骤的输入由前一阶段的输出组成上一阶段的相等性检查结果a。阶段c将执行最终的或运算,以在最后的辅助线中得到f A≠B。本阶段所示的设计基于公式16和17。

$$ Ei= Ai ⊕ Bi \quad for \quad 0 ≤i ≤ n− 1 $$ (16)

$$ fA≠B= E0+ E1+…+ En−1 $$ (17)

5.8.1.可逆的A不等于B电路的性能参数

本节详细阐述了A不等于B电路的性能参数计算。a和e阶段分别作为第一和最后阶段添加到A非零电路中。因此,A非零电路与A不等于B电路的计算仅在第一和最后阶段有所不同,其余计算相同。stagea:在阶段a中,线上 A和 B上的每一位数据都输入至CNOT门。该阶段包含 n个 CNOT门。此阶段的量子代价为 n,辅助输入的总数与 A非零电路相同,即 n − 1。阶段 e是阶段 a的镜像。性能参数列于表X中。

5.9.可逆电路设计:条件选择

该电路类似于CSWAP电路,只是CSWAP电路的输入为线路B上的数据和0000…1(仅最低有效位为1,其余位为0)。令控制位为Y,其中Y=(A ≠ 0)⋅(A ≠ B)。如果Y为真,则执行交换操作;否则,数据将直接传递到输出线。对于性能参数,我们参照表VI。

5.10.最终迭代阶段

在此阶段,如果在特定迭代中(在迭代阶段生成)A偶数和B偶数输出为真,则B线上的数据左移2n−4次。可逆电路设计与/2模块相同,但位索引方向相反。为了生成控制线以指示A和B均为偶数,使用了UPG门。UPG门的第三输出线作为控制线提供给移位模块(参见图7)。该模块的性能参数参考表IV。

顶层模块的仿真结果如图11所示。

6. 与现有工作的比较

在本节中,我们给出了构建最大公约数架构所用各组件的性能参数估计,并与现有工作[23]进行了比较。表XI、XII、XIII和XIV列出了针对n位操作数的门数量、量子代价、辅助输入和逻辑深度的估计值。表XV、XVI和XVII给出了输入尺寸宽度从8到1K位范围内的比较结果。这些表格展示了所提出方法与现有工作的估计值,以便进行对比分析。表中所列数值均为数据在奇数和偶数位长度下的最坏情况值。在现有设计中,有几个参数需要注意:w(n)表示n的二进制展开中 1 ′ s的数量。现有工作在表格中列出的参数仅考虑了CNOT门和Toffoli门。

7. 结论

我们提出了一种基于改进的二进制最大公约数算法并使用可逆逻辑门实现的最大公约数计算电路。该设计在构建电路组件以实现最大公约数算法时,采用了非门、托佛利门、费曼门(CNOT)、BJN门、UPG门、改进型TR门和弗雷德金门作为基本的可逆逻辑单元。所有性能指标均已列表统计,结果表明在门数量、量子代价和辅助输入方面,性能参数均有提升。现有设计与提出的设计在条件减法电路中的辅助输入数量相同,但我们的设计在门数量和量子代价方面表现更优。由于整个电路使用了较少数量的可逆门,因此极大可能降低功耗,从而缓解功耗分析攻击。该算法及所有电路组件均通过Verilog硬件描述语言和Xilinx ISE仿真器进行了验证。

44

44

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?