直接说解决办法:取消外部硬件和内部CPLD的上拉,外部下拉视情况选择。

以下是debug过程:

问题描述: ALTERA 10M08SAU169 在3V3上电时,输出pin perst信号会有4.5ms的高脉冲,影响以太网芯片的正常时序,需要消除此脉冲。

环境:CPLD该pin外部有10K上拉,预留有下拉;

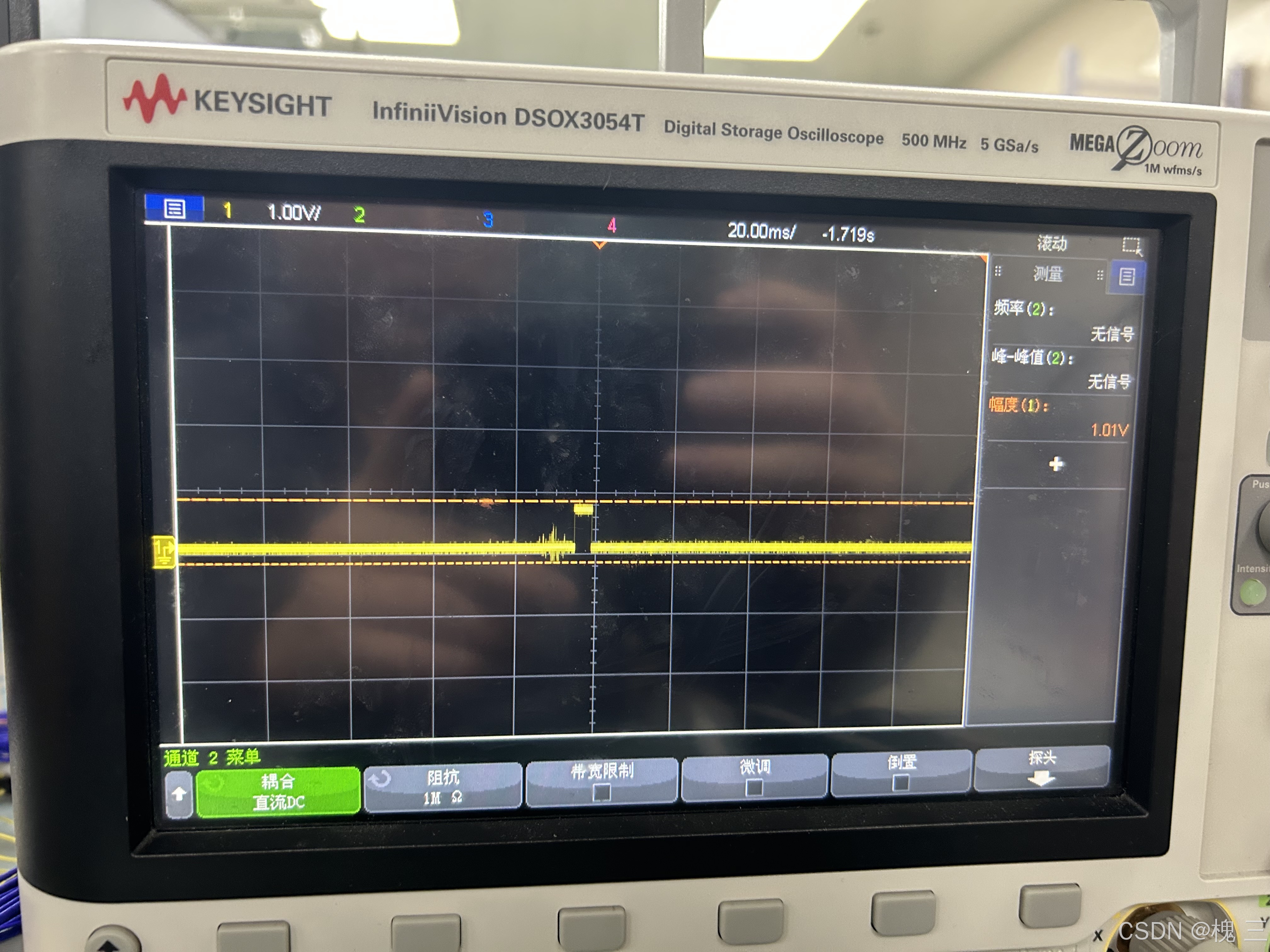

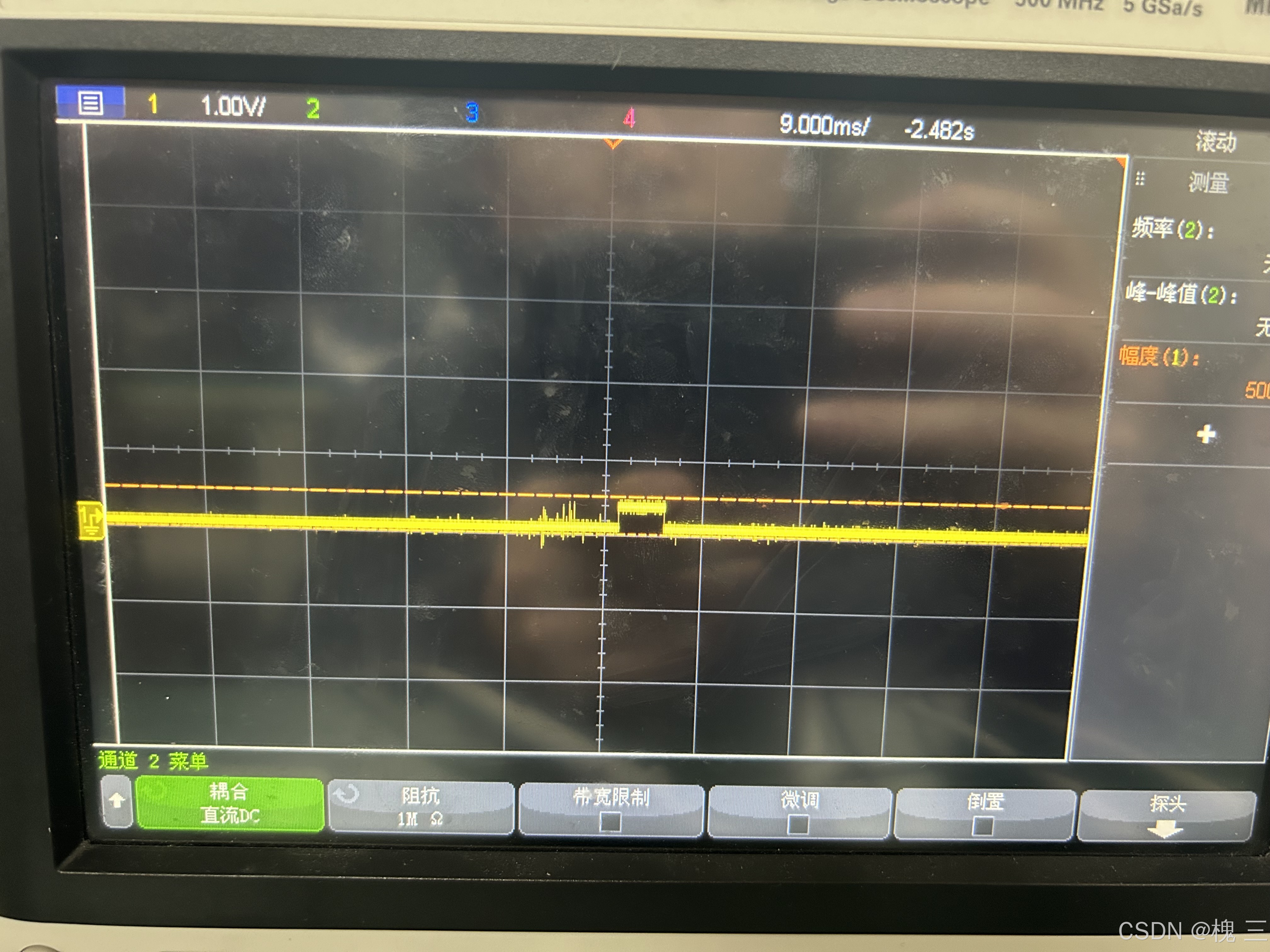

现象:绿色为CPLD 3V3供电,黄色为perst输出高脉冲,可确认发生在3V3上电完成,CPLD初始化阶段。

debug:

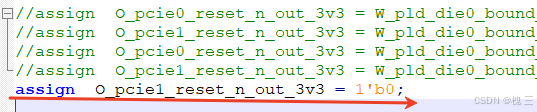

1.根据上图时序,考虑Verilog里perst的逻辑还未生效;

验证:将perst置0,示波器量测到脉冲复现。

2. 考虑CPLD默认三态时,外部上拉会影响;

验证,去掉外部上拉,并贴4.7K和2.2K下拉电阻做对比测试:

4.7K 脉冲被拉低到800mV左右

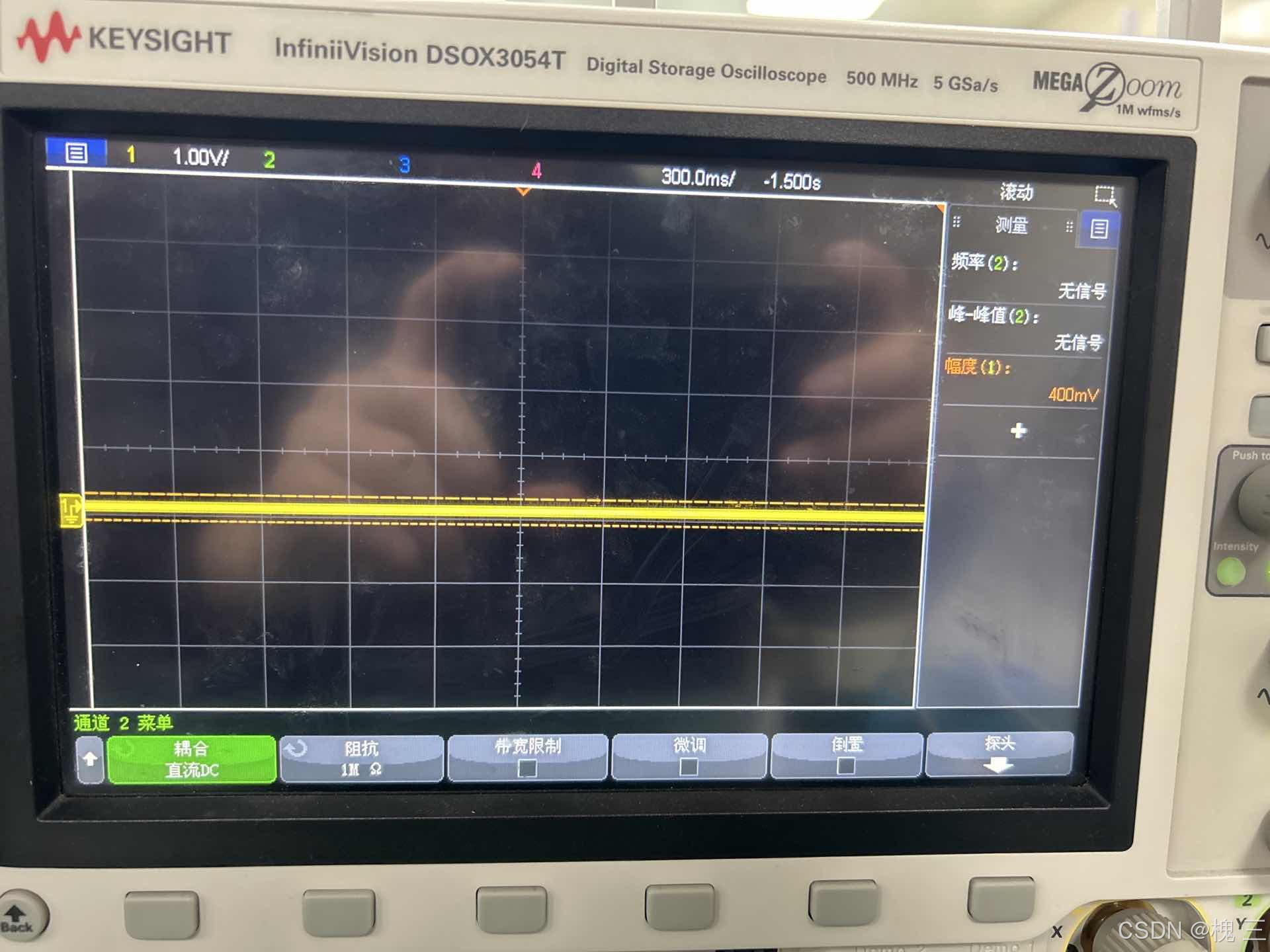

2.2K,脉冲被拉低到400mV左右;

结论:下拉有效,但根据波形,脉冲不是消失而是变小,像在和下拉打架,考虑三态可能还是受到某种上拉的影响。

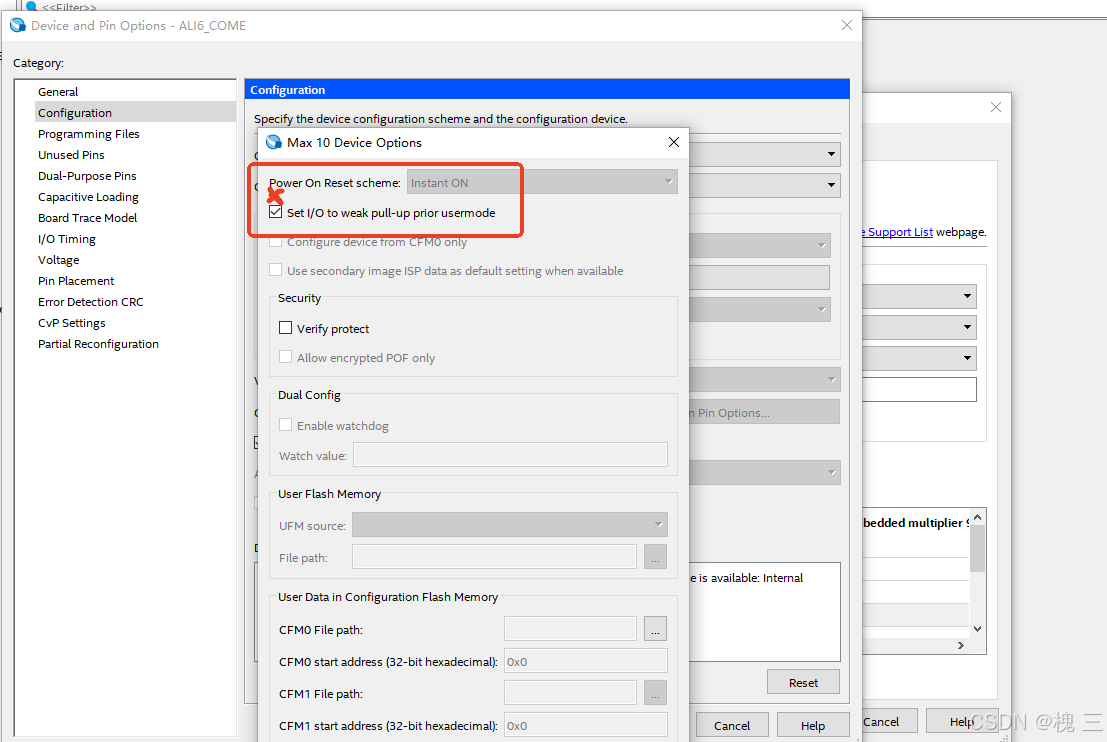

调整:检查发现,CPLD还有上电后默认弱上拉的配置,取消此选项,高脉冲消除~bingo

去掉外部下拉复测,高脉冲未再出现。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?