TX测试

一: GEN1、2、3采用自动化测试:

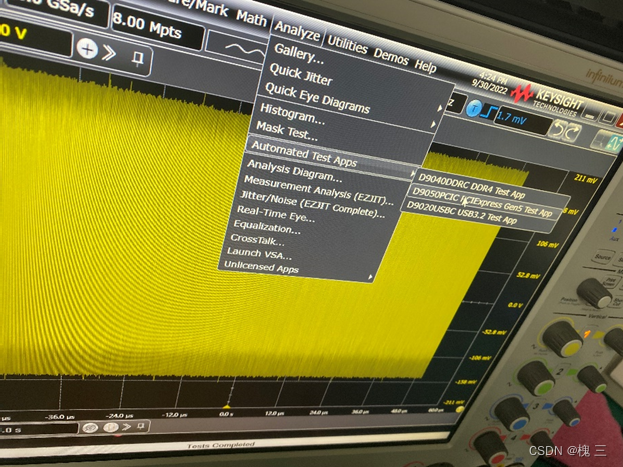

1. 点击infinum软件中Analyze->Automated Test Apps->D9050PCIC PCIExpress Gen5 Test App,进入自动化测试界面;

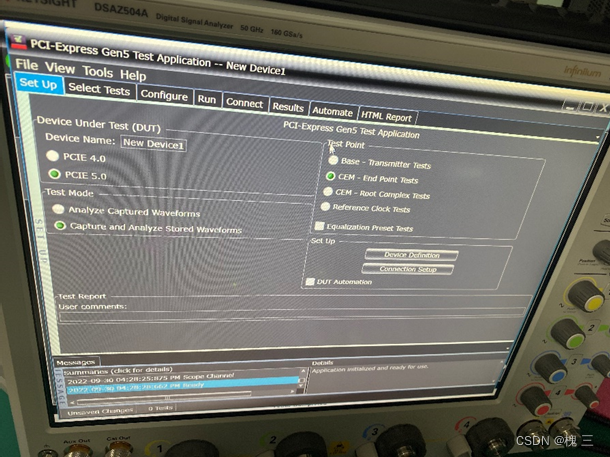

2. Set Up窗口:PCIE5.0->CEM-End Point Tests->Device Definition->勾选5G的-3.5dB&-6dB->选择8G的P0

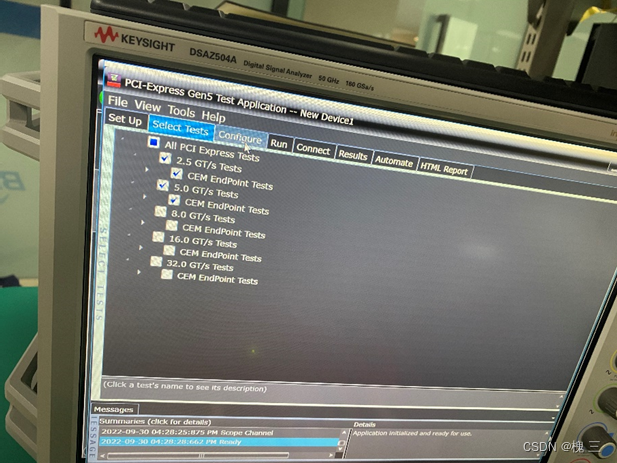

3. Select Test界面将Device Definition设置的测试项全部勾选:

4. Run界面,点击Run按钮;注意示波器屏幕弹窗提醒,确认对应的速率,按CEM板卡上按键使测试的码型和实际速率保持一致。

5. GEN3_P01~P10同样用自动化测试,将第2步的Device Definition中仅选择P01~P10,点击Run,按CEM板卡上按键使测试的码型和实际速率保持一致。

6.测试自动结束,导出Report PDF版本。

二: GEN4_P01~P10采用手动测试

- CEM板卡上Lanexx_P接示波器通道1,N接通道3;点示波器的autotest

- 点击Set up,设置Channel1+3差模有效,共模无效;设置带宽25G;

- 设置采样率80G,采样深度,采样时间;

- 通过第3步将200w个波形刚好呈现在屏幕中,保存成bin文件;

- 打开sigtest软件,导入bin文件,生成Report。

RX测试:

硬件环境:

误码仪M9070的TX->ISI pair24(选择哪个pair是经过校准后得到的)->CEM RX->add in card(1BF) ->CEM TX->误码仪的RX; 1BF板卡启动模式为XIP,可以PCIe启动并接CVD进行寄存器修改;

打开软件->setup->点击break+testart->当软件界面误码一栏的灯不亮+误码仪TX P9码型和1BF TX的P5码型均显示True时,表示1BF板卡成功连上了。

点击measurement->error ratio test进行为时1min的测试,误码≤1表示测试通过。

还可进行自动化测试,可测RX3项:compliace LEQ compliance LEQ Jitter Tolerance

2022.10.27是德科技实验室RX测试手记--

PCIe双芯板:1、上电码型为Gen1; 2、去掉一根RX的P或N就可以/电阻位加100或50Ω也可以测试通过;

更换为PCIe5的夹具板后1 2 问题不再复现。

对单芯板进行PWJ测试:码型上 抓第2个sine波,示波器关键步骤:25G->1+3channel->80M->14us时域长度->勾选off sinewave

RX的Gen3/4/5夹具各不相同,因为损耗不同,Gen4/5夹具板的板材不同

M8040误码仪:

软件:Station Config~,配置软件

原始信号autoscale调好以后再改差模会准确,减小失真(适用平时示波器进行AC Timing分析)

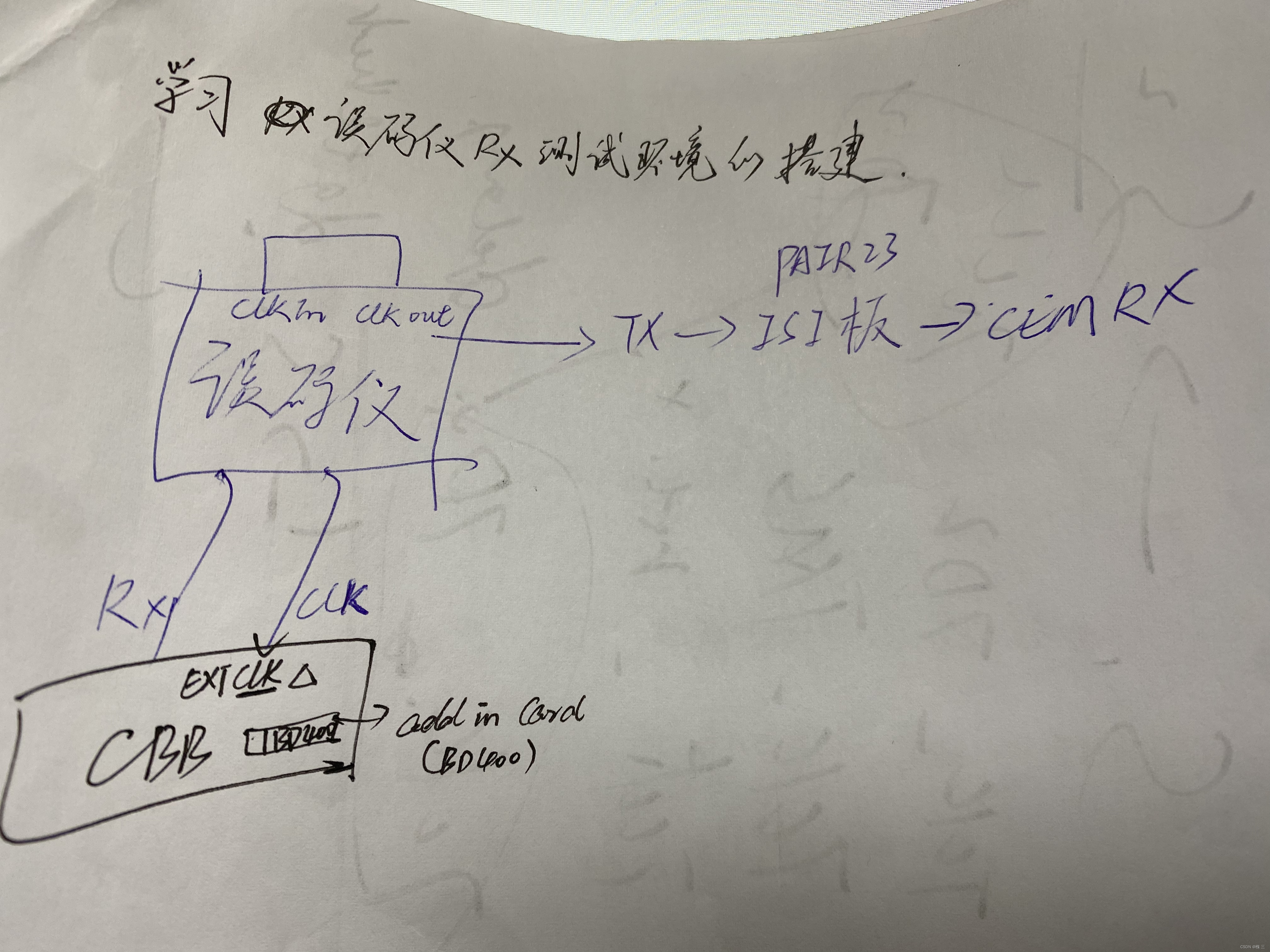

误码仪RX测试环境的搭建:

双芯板RX进不到loopback,软件显示2.5G信号时有时无,去掉ISI上cable线(为了降低损耗)仍fail,再测可以进入loopback;但RX test可以进入loopback不能表示信号OK,还要看误码率指标E12≤1。

单芯板lane15没加ISI损耗 出报告(lane15的走线最短,Lane0 最长)BER:10的-9次方

关掉共模后误码率测试pass

打开共模,调节Voltage:300mV pass;400mV是临界值,开始有误码。

结论:单芯板lane15的共模降到400mV以下 RX Test就pass

误码仪以及其他信号源无静电防护设施,使用时先关掉Global output,再换输出端子;单芯板lane0有时可以进到loopback(进入到loopback后才可以测到RX的test case),表现为Data1

->4 OK。

双芯板lane0 RX Test:

步骤:1.M8070B 软件初始化3min;

2.可以进到loopback(无ISI,P5码型),近端会选P5,信号最好;

3.加ISI:Pair23,每次更改要将软件初始化 ,远端trace变长,选P9;进不到loopback,误码较多;

4.尝试改共模:降到200mV,误码明显减少;100mV无误码,pass(跑了3次也有1~5个误码但很少)

软件中共模标定值520mV,误码仪会将此共模信号加进RX路径中。

单芯板lane15(走线最短)加ISI pair23测RX: 测试过程记录----

修改CMD FW寄存器

1.进不去loopback

2.换成双芯lane15后可以进到loopback(环境与1一致),返回1的环境

3.单芯板lane15(加ISI)RX出报告->进不去loopback(training阶段)->关掉Training的共模->进不去loopback->修改寄存器->可以进到loopback->加回ISI pair23->在training中下调共模,找到的码型是P5(不是P9)->再试1次是P9,还是会跳出loopback->软件重新training后解决,不再跳出loopback; 但TX信号不好,但可以测试了(进入loopback后才可开始测试)

(环境:关掉共模,有噪声源(差模sj rj)给到RX时,误码率为0(2min内),打开共模200mV->Margin有误码->继续测试,修改CMD,不减小共模(保持540mV),进行RX test:1次fail,2次进到loopback,但进到P6)->再测双芯lane0+ISI+共模520mV:信号很差误码多;去掉共模pass。

熟读《PCIe_5.0_PHY_Test_Spec_Ver1.0》文档

本文介绍了一种针对PCIe Gen5的测试方法,包括自动化测试和手动测试两种方式。自动化测试适用于GEN1、2、3,通过Infinum软件进行;手动测试则适用于GEN4,使用示波器和SigTest软件完成。

本文介绍了一种针对PCIe Gen5的测试方法,包括自动化测试和手动测试两种方式。自动化测试适用于GEN1、2、3,通过Infinum软件进行;手动测试则适用于GEN4,使用示波器和SigTest软件完成。

2020

2020

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?