1.新建文件夹命名fulladd

2新建一个工程,点击输入框,输入代码

module

fulladd(sum,c_out,a,b,c_in);

output sum,c_out ;

input a,b,c_in;

wire

s1, c1, c2 ;

xor

(s1,a,b) ;

and

(c1,a,b) ;

xor

(sum, s1,c_in) ;

and

(c2,s1,c_in) ;

or(c_out,c2,c1) ;

endmodule

module test;

wire sum,c_out;reg a,b,c_in;

fulladd fadd(sun,c_out,a,b,c_in) ;

/*

initia1

begin

#15 force fadd. sun=a&b&c_in;#20 release fadd.sun;

#10 $stop;

end

*/

initial

begin

a=0;b=0;c_in=0;

#10 a=0;b=0;c_in=1;

#10 a=0;b=1;c_in=0;

#10 a=0;b=1;c_in=1;

#10 a=1;b=0;c_in=0;

#10 a=1;b=0;c_in=1;

#10 a=1;b=1;c_in=0;

#10 a=1;b=1;c_in=1;

#10 $stop;

end

endmodule

3.点击运行按钮,开始运行检查错

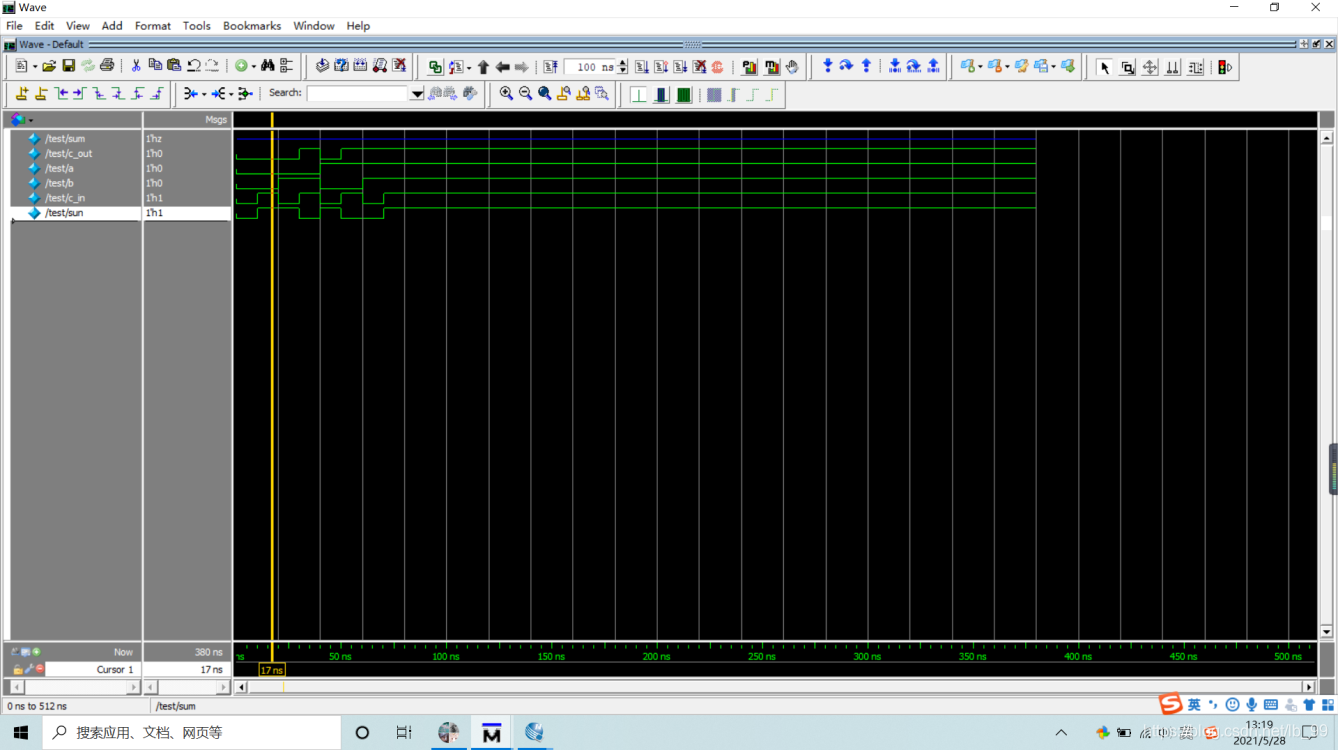

4.全部正确后,改变仿真途径为modelsim开始进行联合仿真

5.改变波长数值导出结果

6.视频链接:https://www.bilibili.com/video/BV1Yg41137mc?share_source=copy_web

这篇博客介绍了如何使用Verilog语言编写一个全加器模块,并通过Modelsim进行仿真。代码中详细展示了全加器的逻辑实现,包括异或门、与门和或门的使用。在仿真部分,设置了不同的输入组合,验证了全加器的功能。最后,提到了如何更改仿真路径和波长数值来观察波形输出。

这篇博客介绍了如何使用Verilog语言编写一个全加器模块,并通过Modelsim进行仿真。代码中详细展示了全加器的逻辑实现,包括异或门、与门和或门的使用。在仿真部分,设置了不同的输入组合,验证了全加器的功能。最后,提到了如何更改仿真路径和波长数值来观察波形输出。

1713

1713

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?