一、题目

题目要求对于一个lemming的行动进行走路,挖掘,掉落,死亡四个状态的转换。

二、解题过程

2.1 审题

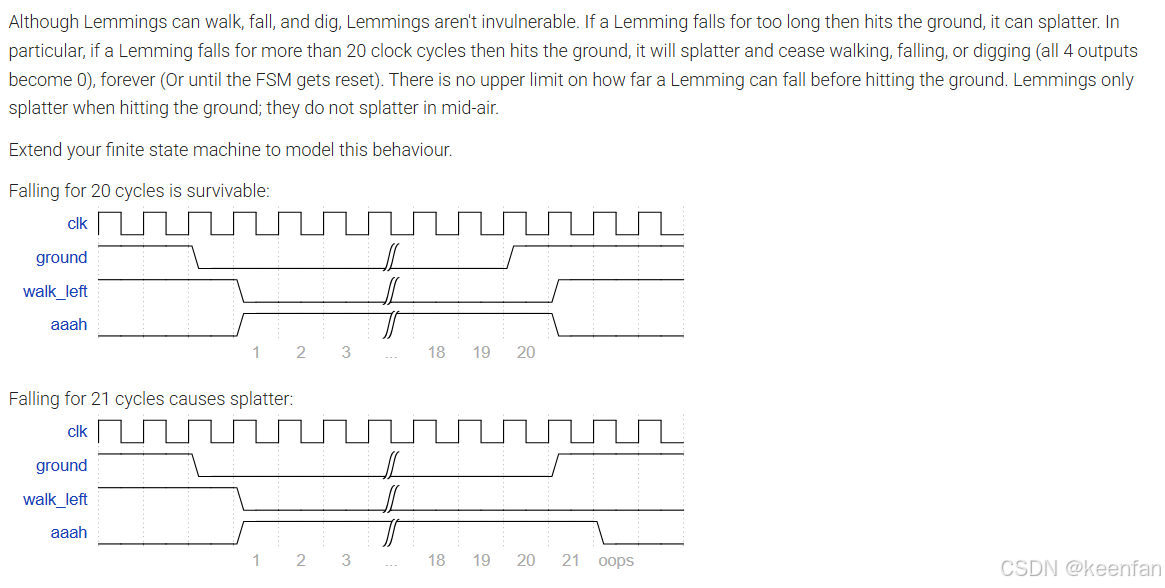

首先,有前三题以及前面状态机相关内容的铺垫,这题的初步思路非常清晰。将状态分为向左走,向右走,挖掘(左),挖掘(右),掉落(左),掉落(右),以及死亡这七个状态。前六个状态在Lemming3中已经练习过,那么,来考虑这里多出来的死亡状态。题中给出,当lemming掉落超过20个时钟周期时,lemming再次接触地面时将会splat,这里即理解为死亡。同时,题中也给出了两幅示意图,表示lemming在掉落20个时序时接触地面并不会导致死亡,在掉落21个时钟周期开始才会死亡。这里很自然想到,在状态为掉落时,提供一个参数作为计数器,通过该参数判断掉落状态持续的时钟周期数,以此判断是否进入死亡状态。

2.2 找不出的问题

在这一题的思路已经很清晰的情况下,很快编完了代码,但在编译时一度存在问题。代码如下:

module top_module(

input clk,

input areset, // Freshly brainwashed Lemmings walk left.

input bump_left,

input bump_right,

input ground,

input dig,

output walk_left,

output walk_right,

output aaah,

output digging );

reg

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

245

245

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?