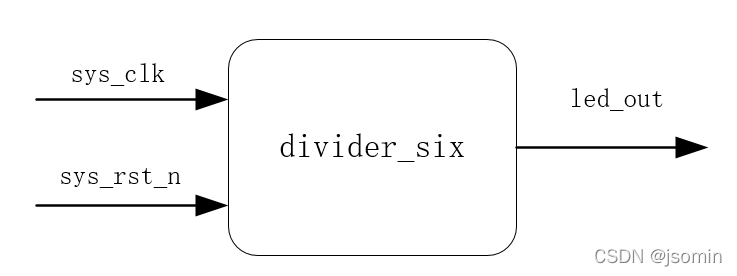

module divider_six

(

input wire sys_clk,

input wire sys_rst_n,

output reg clk_out

);

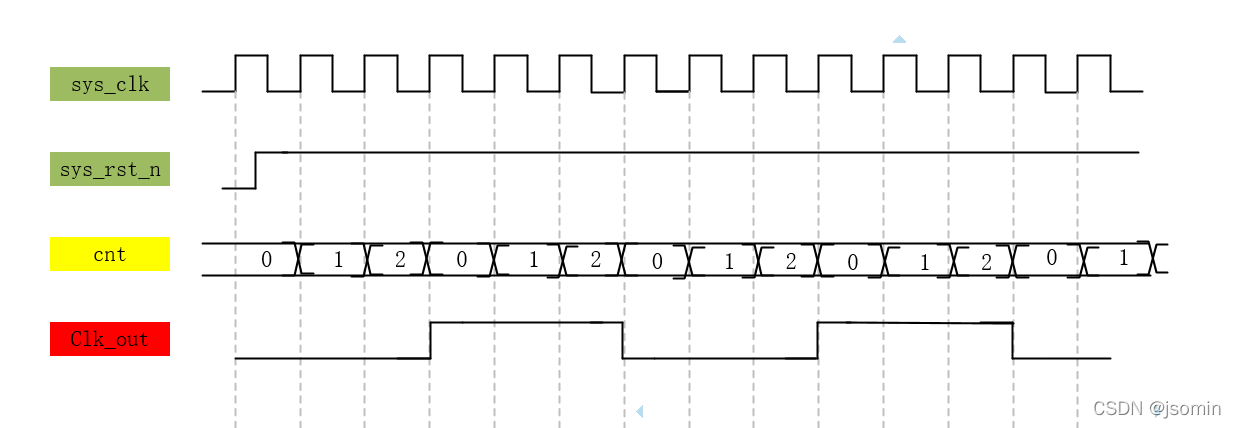

reg [1:0] cnt;

always@(posedge sys_clk or negedge sys_rst_n)//使用异步复位

if(sys_rst_n == 1'b0)

cnt <= 2'd0;

else if(cnt == 2'd2)

cnt <= 2'd0;

else

cnt <= cnt + 2'd1;

//输出信号

always@(posedge sys_clk or negedge sys_rst_n)//使用异步复位

if(sys_rst_n == 1'b0)

clk_out <= 1'b0;

else if (cnt == 2'd2)

clk_out <= ~clk_out;

else

clk_out <= clk_out;

endmodule`timescale 1ns/1ns

module tb_divider_six();

reg sys_clk;

reg sys_rst_n;

wire clk_out;

initial

be

本文档详细介绍了两个Verilog模块,一个是使用异步复位的六路分频器,另一个是带有同步复位功能的计数器。通过实例代码展示了如何设置定时器周期和复位逻辑。适合学习Verilog设计和时钟控制原理。

本文档详细介绍了两个Verilog模块,一个是使用异步复位的六路分频器,另一个是带有同步复位功能的计数器。通过实例代码展示了如何设置定时器周期和复位逻辑。适合学习Verilog设计和时钟控制原理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2873

2873

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?