在高速 PCB 设计中,信号完整性就像一场精密的 “接力赛”,而线宽线距则是决定接力棒能否平稳传递的关键。那些看似微小的尺寸变化,可能让高频信号从流畅传输变成 “跌跌撞撞”。

线宽:阻抗匹配的 “调节器”

线宽与信号完整性的核心关联在于阻抗匹配。PCB 上的导线并非理想导体,其特性阻抗由线宽、铜厚、介质厚度和介电常数共同决定。对于高频信号来说,阻抗不连续会导致信号反射,就像声波遇到障碍物会回声一样,严重时会让信号波形失真。

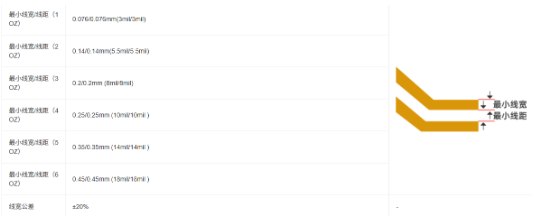

PCB 批量厂家的阻抗计算表显示:在 1 盎司铜厚、0.2mm 介质厚度的 FR-4 板材上,50Ω 微带线的标准线宽是 0.35mm(14mil)。若线宽偏差超过 ±0.05mm,阻抗就会偏离设计值 10% 以上。某通信 PCB 批量厂家的测试数据证实,当阻抗偏差达到 15% 时,10GHz 信号的反射损耗会从 - 20dB 恶化至 - 12dB,眼图张开度缩小 30%。

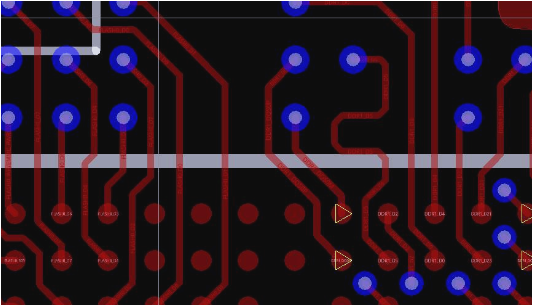

线宽突变是更危险的 “信号陷阱”。在导线拐角或分支处,若线宽突然从 8mil 变到 12mil,会形成阻抗台阶,导致信号反射。PCB 批量厂家推荐采用 “渐变过渡” 设计,让线宽变化率控制在 1:3 以内(即 1mm 长度内线宽变化不超过 0.33mm),这种处理能将反射损耗降低 60% 以上。某服务器 PCB 通过优化线宽过渡,成功解决了 PCIe 4.0 信号的抖动超标问题。

线距:串扰抑制的 “防火墙”

线距是控制信号串扰的关键。当两根导线距离过近时,高频信号产生的电磁场会相互耦合,就像两根平行的琴弦会共振一样,导致信号之间的干扰。串扰会造成信号误判,在高速数字电路中可能引发数据传输错误。

PCB 批量厂家的串扰测试表明:当线距等于线宽时,串扰耦合度约为 - 20dB;将线距增加到线宽的 3 倍,串扰可降至 - 40dB 以下。在 10Gbps 信号传输中,这意味着串扰导致的误码率从 1e-6 降至 1e-12。某 5G 基站 PCB 批量厂家严格执行 “线距≥3 倍线宽” 的设计规则,使射频信号的邻道干扰降低了 15dB。

平行布线长度同样重要。即使线距达标,过长的平行段仍会累积串扰。PCB 批量厂家建议,高速信号线的平行长度不宜超过信号波长的 1/10(如 10GHz 信号波长约 30mm,平行段应≤3mm)。通过插入接地导线(“隔离柱”),可在不增加线距的情况下将串扰再降低 10dB,这种方法在高密度 PCB 中特别实用。

不同速率下的线宽线距策略

信号速率不同,对线宽线距的敏感度也大相径庭。PCB 批量厂家会根据信号速率制定差异化方案。

低速信号(<100Mbps)对参数宽容度较高,线宽线距主要满足载流和绝缘要求即可。例如单片机的 GPIO 信号,采用 6mil 线宽、6mil 线距完全能保证信号完整性,过度追求精细参数只会增加成本。某家电 PCB 批量厂家的实践显示,低速电路采用 8mil/8mil 标准,比 6mil/6mil 方案成本降低 12%,且不影响性能。

高速信号(1-10Gbps)进入 “敏感区”,需精确控制阻抗和串扰。PCB 批量厂家会使用三维电磁场仿真软件,计算出最优线宽线距组合。如 USB 3.0 信号(5Gbps)在 0.2mm 介质层上,推荐采用 4.5mil 线宽、15mil 线距(3 倍线宽),配合差分对设计,可将阻抗控制在 90Ω±10%。

超高速信号(>10Gbps)则需要 “极致优化”。PCIe 5.0(32Gbps)信号的线宽偏差需控制在 ±0.5mil 内,线距需达到线宽的 5 倍以上。某数据中心 PCB 批量厂家引入激光直接成像技术,将线宽精度提升至 ±0.3mil,配合高精度层压工艺,使超高速信号的眼图测试通过率从 82% 提升至 97%。

信号完整性保障措施

为确保线宽线距符合信号完整性要求,PCB 批量厂家建立了全流程管控体系。

在设计阶段,提供 DFM 分析报告,指出可能影响信号的线宽线距问题。某 PCB 批量厂家的智能 DFM 系统能自动识别阻抗不连续点、串扰风险区域,并给出优化建议,使设计修改周期缩短 40%。

生产环节采用高精度工艺,激光蚀刻线宽精度可达 ±0.3mil,比传统机械蚀刻提升 50%。在线监测系统每小时抽样测量线宽,确保批量生产的一致性。某高速 PCB 批量厂家通过工艺优化,将同批次产品的阻抗偏差控制在 ±5% 以内。

成品测试环节增加信号完整性验证,对关键信号线进行时域反射(TDR)测试,测量实际阻抗曲线。对于超高速 PCB,还会进行误码率测试,确保线宽线距设计真正落地。

线宽线距对信号完整性的影响,本质是电磁场与导体尺寸相互作用的结果。从几 mil 的尺寸变化到信号的完整传输,中间隔着精密设计与制造的鸿沟。PCB 批量厂家的价值,就在于将这些微观参数转化为稳定可靠的信号传输通道。

239

239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?