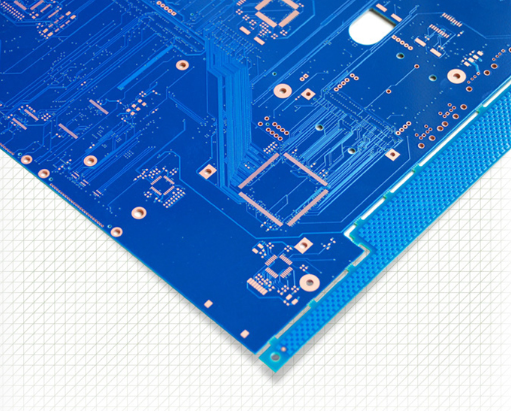

理论知识和技术工具最终要落实到实际设计中。作为PCB技术运营专家,我今天将分享PCB阻抗控制的实战技巧,帮助大家避免常见陷阱,提高设计成功率。

叠层设计:阻抗控制的基础

合理的叠层设计是阻抗控制成功的一半。对于多层板,我们通常遵循以下原则:

-

为关键阻抗控制走线提供完整的参考平面

-

相邻层之间保持一致的介质厚度

-

高速信号层应邻近参考平面层

以六层板为例,有三种常见结构形式。结构形式1(Top-Gnd-Signal-Power-Signal-Bottom)适合需要较低电源阻抗的场景;结构形式2(Top-Gnd-Signal-Signal-Power-Bottom)能为射频提供良好屏蔽;结构形式3(Top-Gnd-Gnd-Signal-Power-Bottom)在需要较多接地层时使用。

差分对设计:高速信号的守护者

差分信号(如USB、HDMI、PCIe)的阻抗控制尤为关键。设计时应遵循以下原则:

-

严格保持线间距一致,避免时序偏差和共模干扰

-

走线要平行、对称,避免90°拐角,采用45°或圆弧走线

-

尽量使用同层差分,避免层间差分信号

对于LVDS等低电压差分信号,差分阻抗通常控制在100Ω±10%,匹配电阻应尽量靠近接收端(距离不超过500mil,最好在300mil以内)。

过孔处理:阻抗连续性的挑战者

过孔是阻抗不连续的主要来源之一。为减轻其影响,我们可以:

-

减小过孔直径和焊盘尺寸

-

使用背钻技术消除过孔存根

-

在关键信号过孔周围添加接地过孔

布线技巧:细节决定成败

在实际布线中,有几个实用技巧值得关注:

-

元件PAD尽量靠近排列,缩短差分线长度,减少过孔数量

-

不同差分线对间距应大于3-5倍差分线间距,必要时加地孔隔离

-

LVDS信号应远离其他信号,最好使用不同的走线层

-

差分信号不可跨平面分割,以免导致阻抗不连续

工艺公差管理:设计与制造的桥梁

PCB制造存在不可避免的公差,设计时必须考虑这一因素。我建议:

-

关键信号预留阻抗调整空间

-

与制造商明确阻抗控制能力和公差要求(通常为±10%)

-

使用TDR测量验证实际阻抗值

案例分享:一次阻抗匹配失败的经验

某次项目中,我们的HDMI接口在测试中出现信号完整性问题。初步排查显示布线符合规则,但最终发现是差分对间距不一致导致阻抗偏差。通过TDR测量,发现实际阻抗在85Ω-115Ω之间波动,远超要求的100Ω±10%。解决方案是重新设计布线,确保全段线距一致,并在接收端精准匹配100Ω电阻。

优化策略:从合格到卓越

对于要求极高的设计,可以考虑以下进阶策略:

-

使用共面波导结构,通过侧面的接地屏蔽提高抗干扰能力

-

针对信号边沿速率优化阻抗匹配,而非仅仅关注直流阻抗

-

在频率域分析阻抗特性,确保在全频段内保持稳定

234

234

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?