四层PCB的数模转换器(DAC)设计直接影响信号保真度与系统可靠性。某头部电子实验室数据显示,四层板设计不当导致的信号失真率可达15%,而优化后可将总谐波失真(THD)降低至-80dB以下。本文基于IPC-2221标准与工程实践,系统解析四层数模转换器设计的核心技术路径。

一、四层板架构设计与电磁兼容性

-

分层策略与信号隔离

-

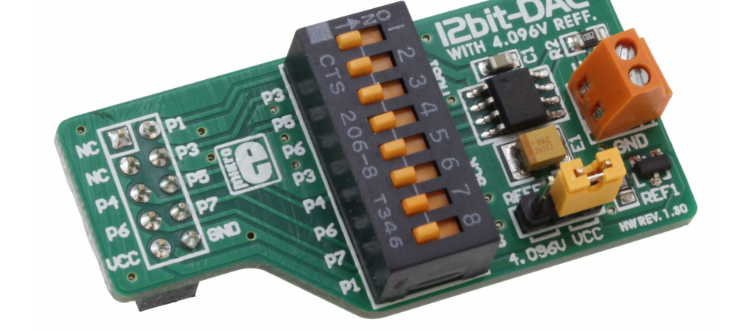

典型结构:TOP(模拟信号层)-GND(地层)-PWR(电源层)-BOTTOM(数字信号层)。地层为模拟信号提供低阻抗返回路径,抑制共模噪声;电源层通过层间电容实现高频去耦,降低数字开关噪声对DAC的干扰。

-

材料选型:选择Df≤0.005的低损耗基材(如Rogers 4350B),确保1GHz频段信号衰减≤0.2dB/inch;铜箔粗糙度Ra≤1.2μm,减少趋肤效应导致的信号畸变。

-

-

电源完整性强化

-

去耦电容布局:每个DAC电源引脚配置0.1μF陶瓷电容(距离≤1mm),并联10μF电解电容(距离≤5mm),形成多级滤波网络。

-

电源层阻抗控制:通过激光盲埋孔阵列(每0.5mm²配置φ0.3mm孔),将电源层阻抗降至≤0.5mΩ,抑制电源噪声波动。

-

二、DAC核心电路设计与优化

-

参考电压稳定性保障

-

参考电压(REF)引脚就近连接低噪声LDO,走线宽度≥2mm,并与地平面形成0.2mm隔离带,寄生电容控制在C<0.1pF。

-

添加0.1μF陶瓷电容并联10μF电解电容,电源抑制比(PSRR)提升至80dB@1kHz。

-

-

抗混叠滤波器设计

-

在DAC输出端添加二阶有源低通滤波器(截止频率=1.2倍信号带宽),采用SMA接口实现50Ω阻抗匹配,反射损耗≤-20dB。

-

滤波器布局采用四层板独立信号层,避免数字信号耦合干扰。

-

-

差分信号完整性控制

-

差分对阻抗严格匹配至100Ω±5%,线间距≥3倍线宽,串扰抑制比>50dB。

-

使用蛇形走线补偿长度偏差,相邻线段长度差控制在±0.5mm以内。

-

三、混合信号布局与干扰抑制

-

区域划分与走线策略

-

模拟区:DAC、参考电压、抗混叠滤波器集中布置于TOP层中央,远离数字IC与连接器。

-

数字区:SPI接口、时钟信号等数字电路布置于BOTTOM层,通过物理隔离减少串扰。

-

-

地平面分割与屏蔽

-

在模拟区与数字区交界处设置0.3mm宽隔离带,数字地(DGND)与模拟地(AGND)通过星形接地点单点连接。

-

关键信号线(如DAC输出)添加屏蔽过孔(每10mm一个),阻断电流路径。

-

-

热管理与应力释放

-

在DAC与MCU下方添加铜填充(厚度≥2oz),配合散热焊盘(尺寸≥2mm×2mm),控制结温<85℃。

-

采用柔性环氧树脂填充层压间隙,缓解热膨胀系数(CTE)失配导致的形变。

-

四、测试验证与调试方法

-

阻抗与信号完整性测试

-

使用Keysight DCA-X(上升时间35ps)进行TDR时域反射测试,关键节点阻抗偏差控制在±5%以内。

-

在1Gbps数据速率下验证眼图,要求眼高≥80% VPP,抖动<50ps RMS,误码率<1E-12。

-

-

EMC与长期可靠性验证

-

依据FCC Class B标准进行辐射测试,1GHz频段内辐射强度低于限值6dB,通过添加金属屏蔽罩(覆盖率>90%)达标。

-

执行-55℃~125℃热循环测试(1000次),阻抗漂移≤±3%,焊点无裂纹。

-

四层PCB数模转换器设计,需构建“架构-布局-工艺”协同优化体系:

-

架构维度:明确模拟/数字区域划分,强化电源与地平面完整性

-

布局维度:关键元件对称布局,差分信号阻抗严格匹配

-

工艺维度:高精度阻抗控制与热管理方案结合

80

80

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?