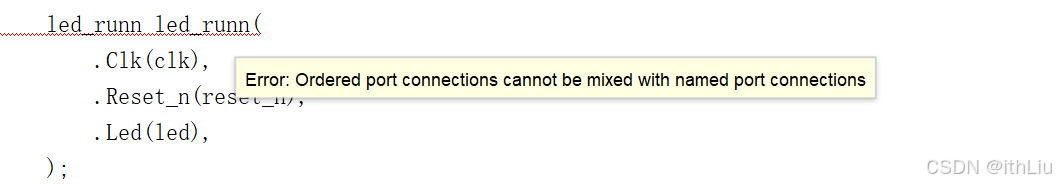

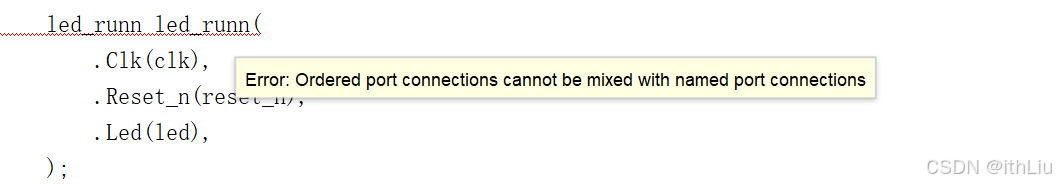

在使用VIVADO进行FPGA例化模块时提示错误“错误:,Error:Ordered port connections cannot be mixed with named port connections,(有序端口连接不能与命名端口连接混合),具体如下图:

简单看了一下好像格式啥的都正确,实则是由于在例化时不合规。

原因: 最后一行多了一个逗号!!!

在使用VIVADO进行FPGA例化模块时提示错误“错误:,Error:Ordered port connections cannot be mixed with named port connections,(有序端口连接不能与命名端口连接混合),具体如下图:

简单看了一下好像格式啥的都正确,实则是由于在例化时不合规。

原因: 最后一行多了一个逗号!!!

1万+

1万+

1231

1231

1万+

1万+

2万+

2万+