书籍:《炬丰科技-半导体工艺》

文章:Micro-LED 显示器量化生产关键技术

编号:JFKJ-21-303

作者:炬丰科技

摘 要

为快速推动 Micro-LED 显示器产业化发展,结合 Micro-LED 微显示器的性能特点、制造 工艺流程和产品应用优势,重点分析了基于硅、蓝宝石衬底的 GaN 外延生长技术、芯片侧壁原子 层沉积技术、芯片转移和晶圆级键合等技术。

关键词: 新型平板显示;微缩化发光二极管;有机化合物化学气相沉积;原子层淀积;晶圆键合

材料制造工艺与设备

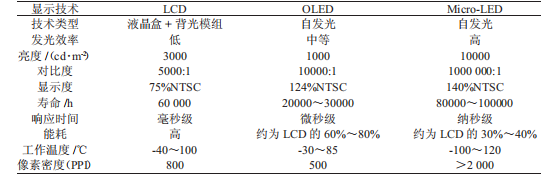

显示器产业技术正朝着高分辨率、高亮度、低功耗和柔性化快速发展,如图 1 所示,新型平板显 示技术主要包括液晶显示 (LCD)、等离子显示、有机发光二极管显示(OLED)和微缩化发光二极管显示(Micro-LED)等几类。

Micro-LED 微显示器制造工艺流程

Micro-LED 微显示器生产制造主要包括衬底外延生长、芯片制造、电路互联键合、性能检测等环节,各环节都有相应的材料、工艺、设备等关键技术要求。Micro-LED 微显示器基本工艺流程。

本文聚焦Micro-LED显示器的产业化发展,探讨了基于硅、蓝宝石衬底的GaN外延生长,芯片侧壁原子层沉积,以及芯片转移和晶圆级键合等关键技术,对于显示器技术的高分辨率、低功耗要求具有重要意义。

本文聚焦Micro-LED显示器的产业化发展,探讨了基于硅、蓝宝石衬底的GaN外延生长,芯片侧壁原子层沉积,以及芯片转移和晶圆级键合等关键技术,对于显示器技术的高分辨率、低功耗要求具有重要意义。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

793

793

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?