Corner可以分为对晶体管的偏差建模的PVT corner,以及对互联线偏差建模的RC Corner。

PVT Corner用于描述晶体管的全局工艺偏差。RC Corner 用于描述互联线工艺偏差。

PVT corner

PVT corner需要覆盖全局工艺偏差,温度偏差以及电压偏差。

process corner

Lot 与 Lot 之间, Wafer Wafer之间, Die 和 Die之间的工艺的偏差都是全局工艺偏差。全局工艺偏差的差别远大于局部工艺偏差的影响(local process variation)。由于全局工艺偏差的存在,导致CMOS的速度有的快,有的慢。从而导致芯片有快有慢。

Process corner被用于对全局工艺偏差进行建模。

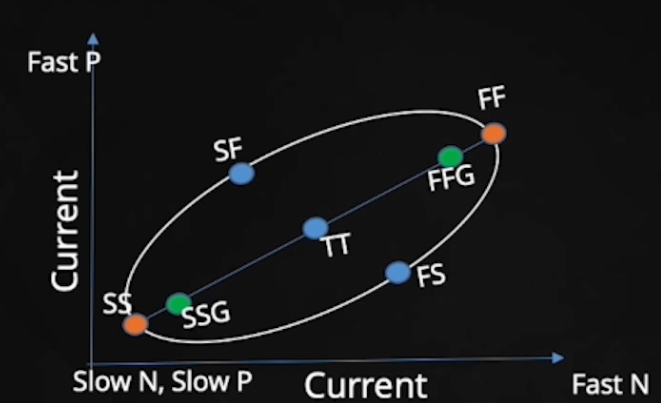

由于全局工艺偏差对CMOS中NMOS, PMOS的影响有所不同,因此按照晶体管的速度,可以分为以下五种process corner:

TT:Nominal

SS:Slow N Slow P

FF:Fast N Fast P

SF:Slow N Fast P

FS:Fast N Slow P

其中常用于进行时序签收的corner为SS FF。

比较先进工艺中,foundary会提供排除local process variation的spice model,即SSG FFG等。

voltage corner

晶体管的速度随着电压的升高而提高。因此,时序签收时需要考虑极限电压的情况,以保证芯片在整个电压范围能够正常工作。

temprature corner

温度会影响晶体管的速度。时序签收时,需要能够保证芯片在设计的整个温度范围能够正常工作。由于结温与环境温度的差异,需保留足够的设计余量。

RC Corner

工艺与温度会对芯片内部的互联线以及via的电阻,电容造成影响。RC Corner用于对互联线的偏差进行建模。

常用的RC Corner Typical Cbest Cworst RCbest RCworst

由于温度对于互联线以及通孔的RC有影响,因此RC Corner也需要考虑到温度的影响。

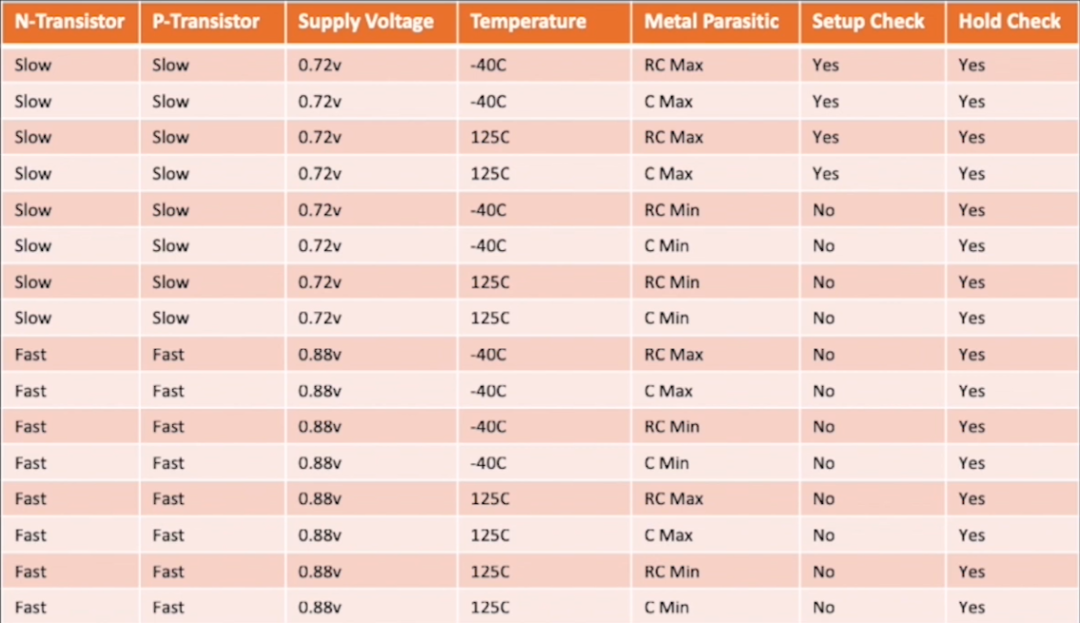

时序签收所用的Corner示例

电压范围:0.72 ~ 0.88 温度范围:-40C ~ 125C

待续

注:若使用的包含有局部工艺偏差的时序库,则在ocv设置中无需在考虑局部工艺偏差。设计余量的大小需根据实际工作的温度,电压的变化谨慎评估。

本文介绍了芯片设计中的Corner概念,包括PVT Corner(process, voltage, temperature)和RC Corner。PVT Corner关注晶体管的全局工艺偏差,如TT、SS、FF、SF、FS等不同情况,用于描述速度变化。电压和温度Corner确保芯片在电压范围和温度变化下正常工作。RC Corner则针对互联线和via的电阻电容偏差。时序签收会结合不同电压、温度范围及RC条件进行验证。"

77334038,5761255,使用Logstash从Kafka导入数据到Elasticsearch,"['数据处理', '日志收集', '大数据', 'elasticsearch集成']

本文介绍了芯片设计中的Corner概念,包括PVT Corner(process, voltage, temperature)和RC Corner。PVT Corner关注晶体管的全局工艺偏差,如TT、SS、FF、SF、FS等不同情况,用于描述速度变化。电压和温度Corner确保芯片在电压范围和温度变化下正常工作。RC Corner则针对互联线和via的电阻电容偏差。时序签收会结合不同电压、温度范围及RC条件进行验证。"

77334038,5761255,使用Logstash从Kafka导入数据到Elasticsearch,"['数据处理', '日志收集', '大数据', 'elasticsearch集成']

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?