使用VSCODE工具编辑Verilog语言的设置方法

本文主要介绍了通过Vscode工具来编辑verilog语言的设置方法,按照本文的步骤方法介绍,设置好vscode工具后能够以不同的颜色高亮显示verilog语言的要素,更重要的是能够自动检测语法错误,提高工具编辑语言的效率和效果

1.软件安装

这里的软件安装包括FPGA常用的编译工具vivado,vscode,以及ctags的插件,前面两种的安装这里不介绍,这里仅仅介绍ctags的插件的下载与安装

1.1ctags插件的下载和安装

ctags的下载源可参考下面的链接:

https://github.com/universal-ctags/ctags-win32/releases

注意,有时链接很难打开,多试几次,多个耐心,根据你使用的电脑是64位还是32位操作系统,选择下载合适的ctags插件。

2.配置

2.1vivado的配置

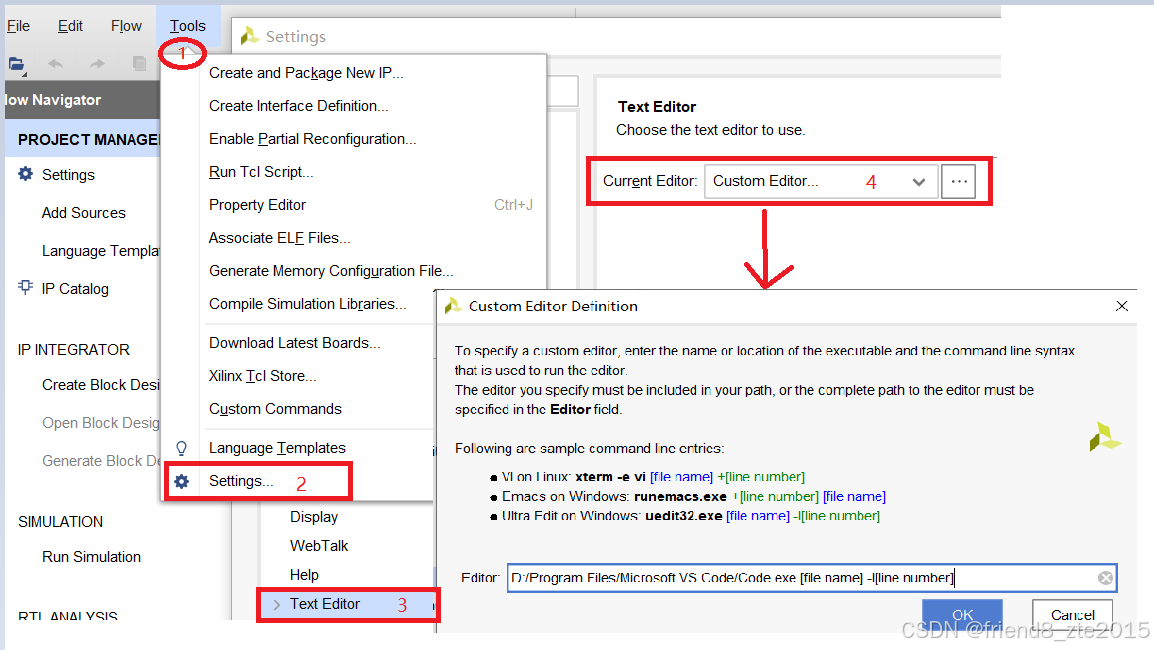

vivado的配置目的,是将vivado的编辑功能引入vscode,可参照下面图1所示的截图。图中分四步(红色的数字)打开和设置vivado界面,最后打开的Text Editor,选择Custom Editor,根据Vs code的安装位置,来设置,例如:D:/Program Files/Microsoft VS Code/Code.exe [file name] -l[line number]

注意后缀 [file name] -l[line number]不要更改,原样复制粘贴

图片:

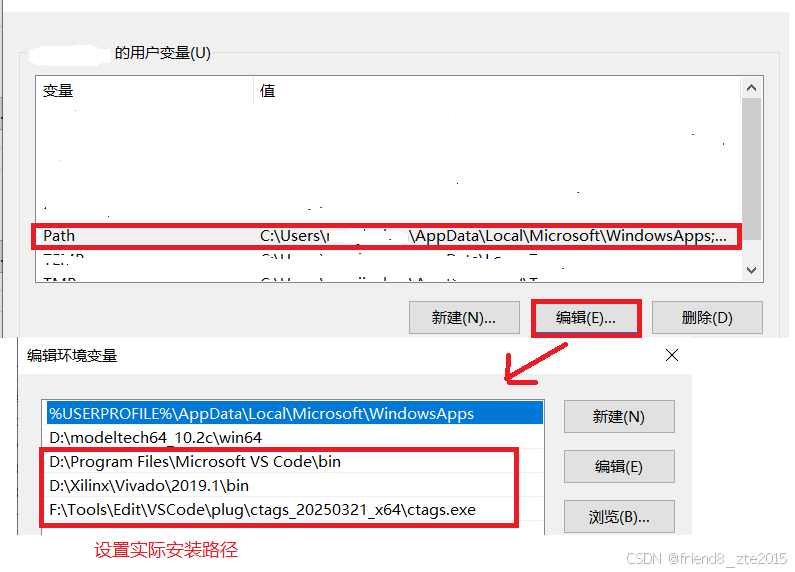

2.2环境变量的配置

选择我的电脑属性,高级系统设置,选择环境变量,如下图1b,所示,找到path所在的位置,选择编辑,参考红框的设置例子,选择你自己电脑中软件真实的安装路径进行设置

3.插件安装与配置

3.1verilog HDL插件安装配置

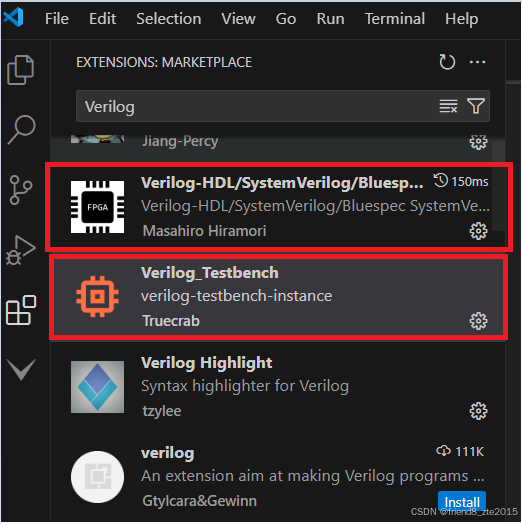

打开Vscode,选择File->Preferences->Extensions,然后选择框中输入Verilog,会搜索出verilog相关的很多插件,点击下面的install按钮就可以安装了。这里安装Verilog-HDL/SystemVerilog/Bluespec和Verilog_Testbench两个插件,安装好后会出现齿轮的标识,如下图2

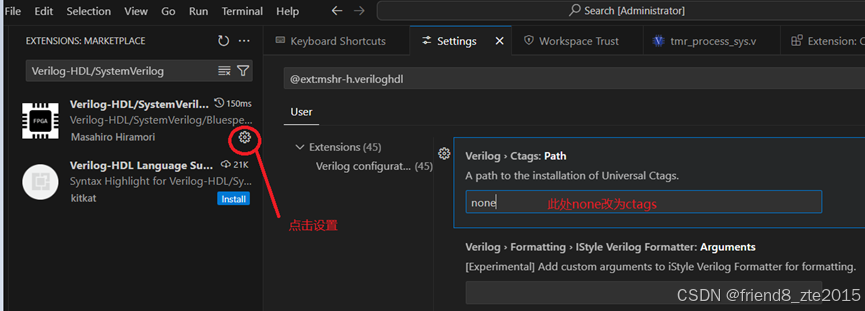

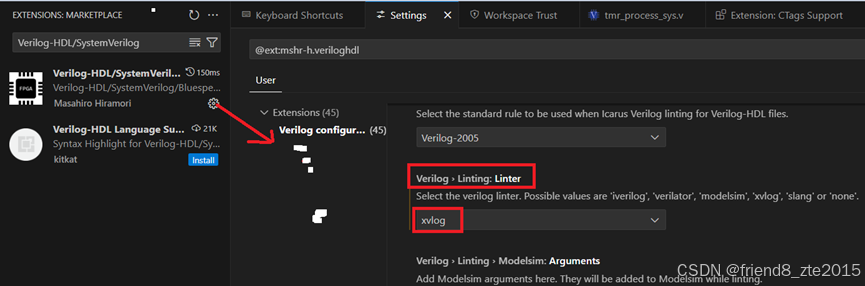

安装好后,点击齿轮标识然后选择菜单中的setting,如下图3a和3b所示,注意这两步的设置非常重要直接关系到vscode能否自动检测verilog的语法错误,按照图中红框和红字设置。注意图3a中的红框中的ctags需要添加具体的安装路径,比如笔者的安装路径是:F:\Tools\Edit\VSCode\plug\ctags_20250321_x64\ctags.exe,红字部分应该填写这个具体的路径,不能仅仅是ctags,否则ctags不起作用

Verilog_Testbench安装好后,无需特殊设置

最后特别注意:linter工具只会在保存(CTRL+S)之后进行语法检查,因此,在编写源码的过程中没有红色波浪线提示,是正常的,如果你需要立刻进行一次语法检查,可以立即保存一次。

4451

4451

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?