文章目录

一、常用插件

1.语法的高亮、简单的语法检查、代码片段、模块例化、定义跳转

插件:Verilog-HDL/SystemVerilog/Bluespec

1.1语法检查

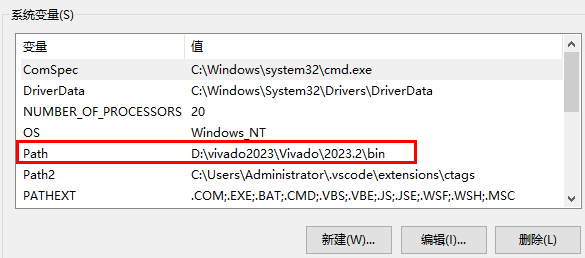

将vivado目录下的xvlog路径添加到系统环境变量中。

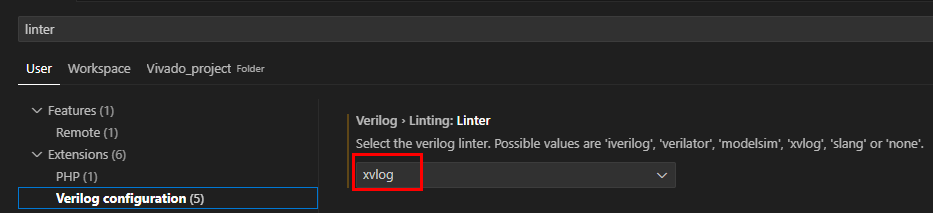

打开设置(快捷键为Ctrl + 逗号),将插件设置中的Linter更换成xvlog。

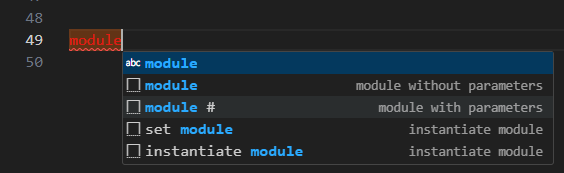

1.2代码片段

功能:在进行关键词输入时对代码片段文件中的模块自动填充,并且按Tab键后跳转到设置的下一个输入位置。

在VS Code默认安装的扩展程序地址中找到verilog.json,打开后修改可以设置自定义的一些代码片段。

C:\Users\Administrator\.vscode\extensions\mshr-h.veriloghdl-1.15.5\snippets\verilog.json

代码片段的设置参考视频:基于VS Code的Verilog编写环境搭建3:00位置

1.3模块例化

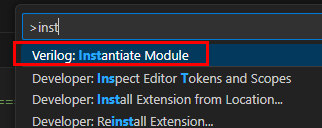

Ctrl+shift+P,在出现的扩展命令框中搜索inst,选择Verilog: Instantiate Module,再现在需要例化的文件即可生产例化模块。

1.4定义跳转

功能:鼠标放在变量上面会提示变量信息, 另外,按Control键点击变量名就会跳转到定义的地方。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5553

5553

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?