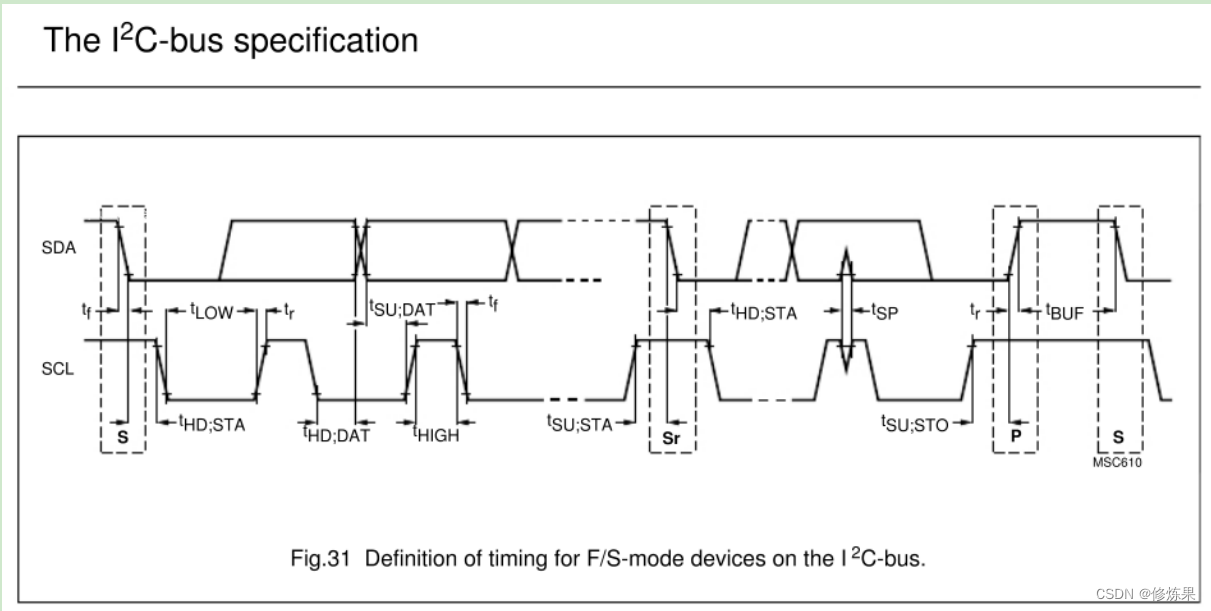

IIC 时序图

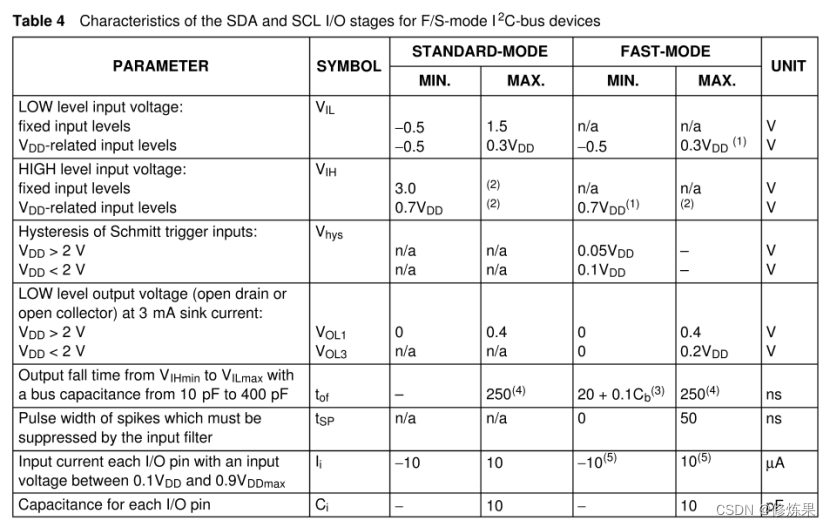

信号质量测试

1、vIL: 低输入电平。

2、vIH: 高输入电平。

3、vhys: 施密特触发器输入的滞后。

4、vOL1: VDD>2V时,低电平输出电压(漏极开路或集电极开路)。

5、vOL3: VDD<2V时,低电平输出电压(漏极开路或集电极开路)。

6、tof: 在有10pF到400pF的总线电容情况下,从VIHmin到VILmax的输出下降时间。

7、tSP: 必须由输入滤波器抑制的尖峰脉冲宽度时间。

8、Ii: 输入电压在0.1VDD和0.9VDDmax之间的每个I/O引脚的输入电流。

9、Ci: 每个I/O引脚的电容。

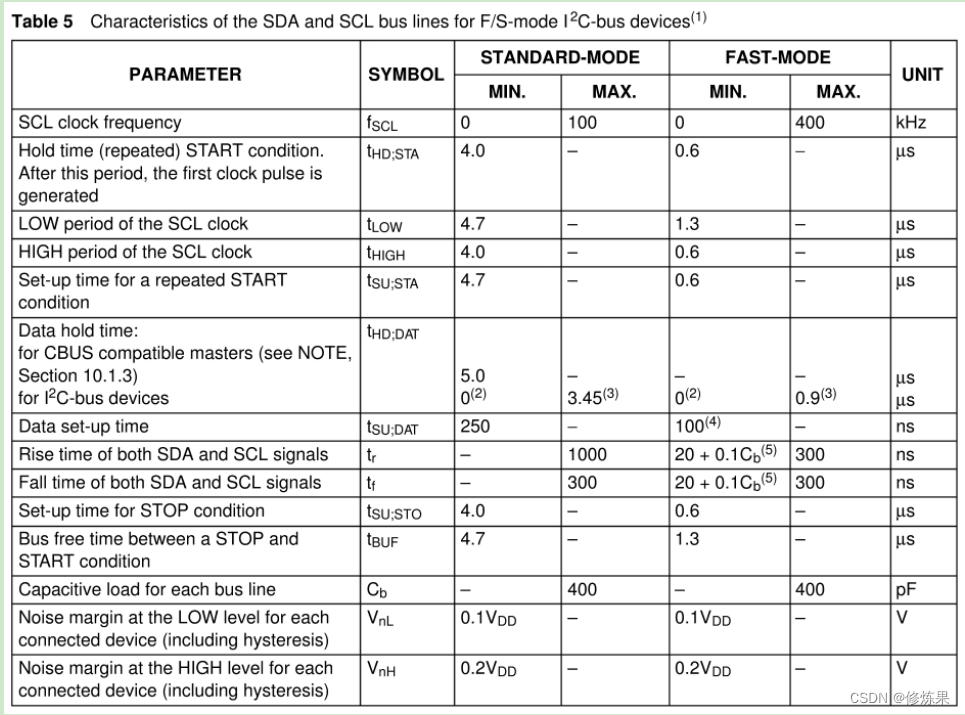

时序测试

1、fscl: 表示IIC的频率。

2、tHD;STA:开始状态的保持时间,表示IIC启动时SDA从低电平阈值(斜率为负)到SCL高电平阈值(斜率为正)的时间。

3、tLOW: SCL从低电平阈值(斜率为负)到另一个低电平阈值(斜率为正)的时间。

4、tHIGH: SCL从高电平阈值(斜率为正)到另一个高电平阈值(斜率为负)的时间。

5、tSU;SDA: SDA建链时间,SDA从低电平阈值(斜率为负)\高电平阈(斜率为正)值到SCL为低电平(斜率为正)的时间。

6、tHD;DAT: 数据保持时间,表示SCL从低电平阈值(斜率为负)到SDA为高电平阈值(斜率为负)\低电平阈值(斜率为正)的时间。

7、tSU;DAT: 数据建链时间,表示SDA为高电平阈值(斜率为正)\低电平阈值(斜率为负)到SCL低电平阈值(斜率为正)到的时间。

8、tr: 表示电压上升时间,从低电平阈值上降到高电平阈值的时间。

9、tf: 表示电压下降时间,从高电平阈值下降到低电平阈值的时间。

10、tSU;STO: 停止状态的建链时间,表示IIC停止状态时SCL为高电平阈值(斜率为正)到SDA低电平阈值(斜率为正)的时间。

11、tBUF: 在停止和开始时间之间的空闲时间。

12、Cb:每条IIC总线的容性负载,单位pF。

13、VnL: 在低电平时,每条总线的噪声裕量(包括输出滞后输入的情况)。

14、VnH: 在高电平时,每条总线的噪声裕量(包括输出滞后输入的情况)。

2705

2705

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?