一、IIC测试的指标

1、信号完整性指标

在 I²C 测试中,信号完整性指标是评估 I²C 通信质量的重要依据,主要聚焦于 SCL 和 SDA 这两条关键信号线。

①电信号:

SCL 和 SDA 的高低电平必须符合相应的标准,以确保数据的准确传输。

在标准的 I²C 通信中,高电平通常接“电源电压” VCC,低电平则接“电源地” GND 。例如,当电源VCC 为 3.3V 时,高电平可能在 3V 左右,低电平在 0.3V 以下。若电平出现异常,如高电平过低或低电平过高,就会导致接收端无法准确识别到准确的信号,从而产生数据错误。

②信号边沿特性:

上升时间和下降时间也是关键参数。

上升时间是指信号从低电平上升到高电平所需的时间,下降时间则相反。在 I²C 通信中,标准模式下,上升时间和下降时间一般要求在一定范围内,如标准模式下,上升时间最大为 1000ns,快速模式下最大为 300ns。若上升时间或下降时间过长,可能会导致信号传输延迟,影响通信速率,甚至可能引发数据采样错误。在高速 I²C 通信中,如果信号的上升沿和下降沿过缓,当 SCL 时钟信号变化时,SDA 数据信号还未稳定,就会导致数据采样错误,通信失败。

③信号噪声:

信号线上的噪声也是需要重点关注的问题。

噪声可能来自于电源干扰、外部电磁干扰等。噪声会叠加在正常的信号上,使信号发生畸变,增加误码率。当 I²C 总线附近存在强电磁干扰源时,如大功率射频电路,可能会在 SCL 和 SDA 线上引入高频噪声,干扰正常的通信信号,导致数据传输错误。

2、信号时序指标

I²C 通信是一种严格同步的通信方式,信号时序指标对于保证通信的准确性和可靠性至关重要。

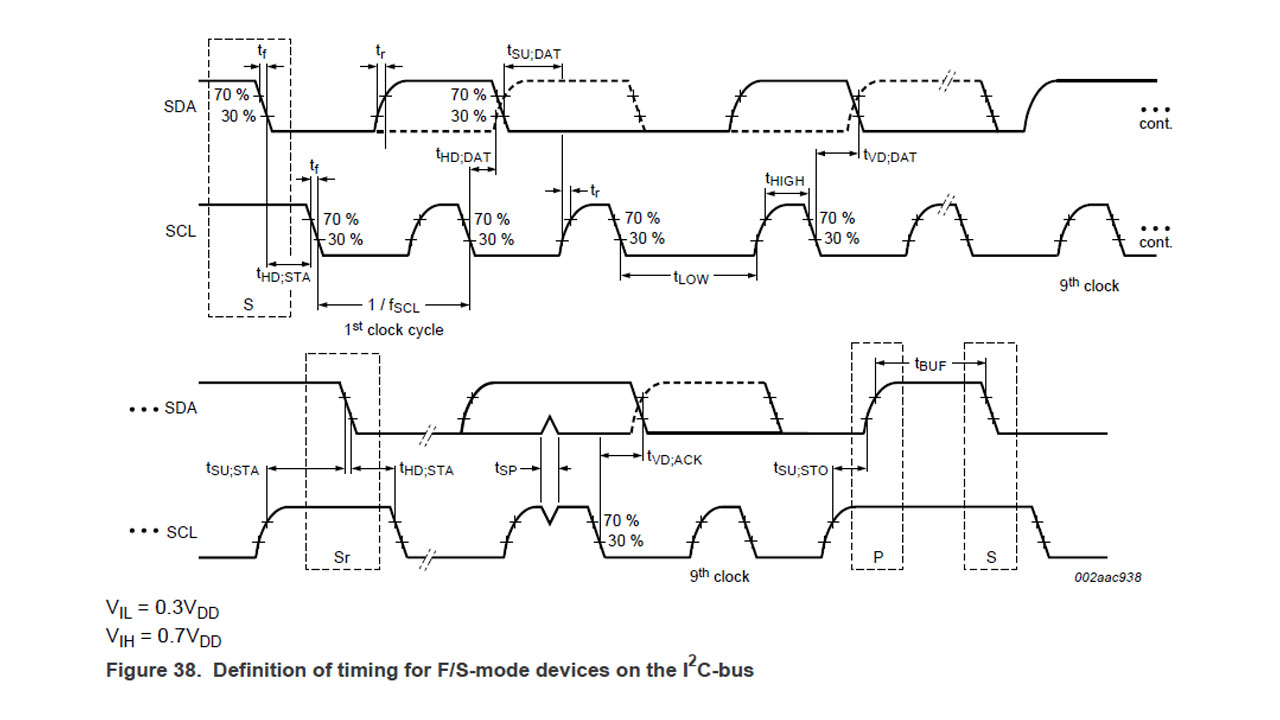

① 起始信号建立时间(tSU;STA)和保持时间(tHD;STA)

-

tSU;STA(起始条件建立时间):SCL为高电平时,SDA从高到低变化前的最小时间。

-

tHD;STA(起始条件保持时间):起始条件后,第一个SCL下降沿前的时间。

这两个参数确保了主机在发送起始信号时,从机能够正确识别。若起始信号建立时间过短,从机可能无法及时检测到起始信号,导致通信无法正常开始;若保持时间不足,可能会被从机误判为正常的数据信号变化,从而引发通信错误。

②停止信号建立时间(tSU;STO)

-

tSU;STO(停止条件建立时间):SCL为高电平时,SDA从低到高变化前的最小时间。

它保证了主机发送停止信号时,从机能够准确识别通信结束。如果停止信号建立时间不满足要求,从机可能会继续等待数据,而主机却已结束通信,导致通信状态不一致。

③数据建立时间(tSU;DAT)和保持时间(tHD;DAT)

-

tSU;DAT(数据建立时间):数据在SCL上升沿前必须稳定的最小时间。

-

tHD;DAT(数据保持时间):数据在SCL下降沿后必须保持的最小时间(通常为0)。

这两个参数确保了在 SCL 时钟信号的上升沿,主机和从机能够准确地采样到稳定的数据。在数据传输过程中,如果数据建立时间过短,数据信号在 SCL 上升沿时还未稳定,就会导致采样错误;若保持时间不足,数据信号可能在采样后立即发生变化,同样会造成数据错误。

④低电平时钟信号(tLOW)和高电平时钟信号(tHD;DAT)

-

tLOW(SCL低电*时间):SCL低电*的最小持续时间。

-

tHIGH(SCL高电*时间):SCL高电*的最小持续时间。

⑤总线空闲(tBUF)和信号边沿

- tBUF(总线空闲时间):停止条件到新起始条件之间的最小时间。

- 信号边沿:

tR(上升时间):SDA/SCL从低到高的最大时间。

tF(下降时间):SDA/SCL从高到低的最大时间。

二、IIC 测试的方法与工具

1、测试方法

在 IIC 信号测试中,示波器是最常用且关键的工具,能够直观呈现 IIC 信号的各种特性,帮助工程师准确判断通信质量和定位问题。

市面上任何一款台式示波器其操作都大同小异,选择合适带宽的示波器和合适的探头很重要,下面简要介绍使用示波器测试 IIC 信号的具体步骤。、

①硬件连接

首先,需要将示波器探头连接到IIC总线的SCL和SDA线上。通常情况下,SCL线连接到示波器的通道1,SDA线连接到通道2。为了确保信号完整性,建议使用高阻抗探头。

②设置解码模式

连接完成后,需要在示波器上设置解码模式。如果你在示波器上没找到“Decode”按钮,那么恭喜,你需要换一个带解码功能的示波器。以下步骤以泰克MSO系列示波器为例:

- 按下“Decode”按钮,进入解码设置菜单。

- 选择“I2C”解码模式。-- 这是专门针对 IIC 总线信号的解析模式

- 设置I2C总线的时钟频率和地址。-- (例如,如果 IIC 通信采用的是标准模式,时钟频率通常为 100kHz,就需要准确设置该频率值,以确保示波器能够正确同步和解析信号。)

- 选择要解码的数据类型,例如数据字节、地址或控制信号。-- (以便示波器在显示解码结果时,能清晰区分不同类型的数据 。)

- 将示波器的带宽设置为20M,避免引入到其他杂波。

- 设置触发条件,例如开始位、停止位或特定地址。

③解码结果

设置完成后,示波器将自动解码IIC总线数据并将其显示在屏幕上。解码结果通常包括以下信息:

数据字节:每个数据字节的十六进制值和二进制值。

地 址:设备地址或寄存器地址。

控制信号:开始位、停止位、ACK信号等。

时 间 戳:每个数据位的发生时间。

/************************************************************************************************************/

在测量过程中,若要更详细地观察信号细节,还可以对示波器进行一些高级设置。比如,利用示波器的过滤功能,过滤掉不需要的数据,如重复的地址或数据,使显示的波形和解码结果更简洁明了,便于分析关键信息;使用搜索功能,快速搜索特定的数据或地址,当需要查找特定的通信指令或数据时,该功能能大大提高分析效率;通过标记功能,对特定的数据或事件进行标记,方便后续分析时快速定位和参考。

④高级设置

除了基本的解码设置之外,泰克示波器还提供一些高级设置,例如:

过滤:可以过滤掉不需要的数据,例如重复的地址或数据。

搜索:可以搜索特定的数据或地址。

标记:可以标记特定的数据或事件,以便于后续分析。

⑤应用实例

泰克示波器测IIC的解码功能可以应用于各种场景,例如:

1.调试IIC总线通信问题:通过解码IIC总线数据,可以分析通信过程中的错误,例如地址冲突、数据错误或时序问题。

2.分析IIC设备的协议:通过解码IIC总线数据,可以分析设备的协议,例如寄存器地址、数据格式和控制命令。

3.测试IIC设备的性能:通过解码IIC总线数据,可以测试设备的响应时间、数据传输速率和可靠性。

⑥拓展

基础协议(UART/I2C/SPI):大多数中端示波器支持。

如果对通信协议有严格测试要求的话,建议选配带“Decode”按钮功能的示波器

/************************************************************************************************************/

三、常见问题及解决方法

1、通信失败问题

在 IIC 通信过程中,通信失败是较为常见且棘手的问题,其背后往往涉及多种复杂的硬件因素。

首先,线路连接问题是导致通信失败的常见原因之一。IIC 总线仅依赖 SDA 和 SCL 两根线进行通信,若这两根线出现断路、短路或者接触不良的情况,都可能导致信号无法正常传输。在实际的硬件设计中,曾遇到由于电路板上的 SDA 线路出现细微的断裂,肉眼难以察觉,结果导致 IIC 通信时断时续,最终完全失败。对于这种情况,工程师需要仔细检查线路连接,使用万用表等工具测量线路的通断,确保 SDA 和 SCL 线与各个设备的连接稳固可靠。

上拉电阻的设置也至关重要。IIC 总线采用开漏输出结构,需要上拉电阻将 SDA 和 SCL 线拉高到高电平。若上拉电阻的阻值选择不当,或者上拉电阻本身损坏,都会影响信号的电平状态,进而导致通信失败。若上拉电阻阻值过大,会使信号上升沿变缓,增加信号传输的延迟,甚至可能导致信号无法被正确识别;若上拉电阻阻值过小,则可能会消耗过多的电流,影响系统的稳定性。当遇到通信失败问题时,需要检查上拉电阻的阻值是否符合设计要求,并使用万用表测量其实际阻值,看是否存在损坏的情况。

设备损坏同样可能引发通信失败。连接在 IIC 总线上的主机或从机设备,若其内部的 IIC 接口电路出现故障,如芯片损坏、引脚短路等,就无法正常进行通信。曾经在一个项目中,由于从机设备受到静电冲击,导致其内部的 IIC 接口芯片损坏,尽管主机不断发送通信指令,从机却毫无响应,通信彻底失败。为了排查设备是否损坏,可以尝试更换新的设备进行测试,若更换后通信恢复正常,则说明原设备存在问题。

2、时序不满足问题

I²C信号时序不满足规范会导致总线通信异常甚至完全失效。具体问题可能表现为数据错误、设备无响应、通信中断或总线死锁等。以下是时序不满足时的典型问题及其原因分析:

1、起始/停止条件失效

-

问题现象:

-

主设备发送起始(START)或停止(STOP)信号后,从设备未响应。

-

总线误触发虚假起始/停止条件(例如,SDA/SCL边沿不满足时序要求)。

-

-

主要原因:

-

tSU;STA/tSU;STO不满足:起始/停止条件的建立时间不足,导致从设备无法正确识别信号。

-

tHD;STA不满足:起始条件保持时间过短,主设备未等待足够时间即拉低SCL,导致从设备未准备好响应。

-

2、 数据传输错误

-

问题现象:

-

接收方读取到错误数据。

-

ACK/NACK位未被正确响应(例如,从设备未拉低SDA)。

-

-

主要原因:

-

tSU;DAT不满足:数据在SCL上升沿前未稳定,导致接收方采样到中间电*(亚稳态)。

-

tHD;DAT不满足:数据保持时间不足,从设备未在SCL下降沿后及时锁存数据。

-

tLOW/tHIGH不满足:SCL高低电*时间不足,设备来不及完成数据读写操作。

-

3、总线竞争与仲裁失败

-

问题现象:

-

多主设备场景下,总线仲裁失败,导致数据冲突。

-

设备意外占用总线,引发通信混乱。

-

-

主要原因:

-

tBUF不满足:停止条件后总线空闲时间不足,新起始条件过早触发,导致设备未释放总线。

-

信号边沿时间(tR/tF)过长:SDA/SCL上升/下降时间超过规范,多个设备对总线状态判断不一致。

-

4、时钟同步问题

-

问题现象:

-

主从设备时钟不同步,SCL被意外拉低。

-

通信速率不稳定(例如,快速模式设备与标准模式设备混用时)。

-

-

主要原因:

-

tLOW/tHIGH不匹配:主设备生成的SCL高低电*时间与从设备要求不符(尤其高速模式 vs 标准模式)。

-

时钟拉伸(Clock Stretching)冲突:从设备拉低SCL的时间过长,导致主设备超时。

-

5、信号完整性问题

-

问题现象:

-

波形畸变(如振铃、过冲、边沿不陡峭)。

-

长距离通信时数据丢失。

-

-

主要原因:

-

tR/tF超标:信号边沿时间过长,导致高低电*转换期间被误判为中间状态。

-

总线电容过大:未根据总线电容(Cp)选择合适的上拉电阻,导致边沿时间增加。

-

6、典型故障场景示例

场景1:ACK位未被响应

-

现象:主设备发送完一字节数据后,未检测到从设备的ACK(SDA未被拉低)。

-

可能原因:

-

tSU;DAT不足:从设备未在SCL上升沿前稳定数据,导致ACK信号未正确生成。

-

tHD;STA不足:起始条件后主设备未等待足够时间即发送数据,从设备未初始化完成。

-

场景2:数据位随机错误

-

现象:通信中偶尔出现某几位数据错误。

-

可能原因:

-

tR/tF过大:信号边沿时间长,在SCL采样窗口内SDA仍处于变化状态。

-

电源噪声干扰:时序余量不足时,噪声易导致电*跳变。

-

7、调试与解决方法

①示波器分析:

-

捕获SDA/SCL波形,检查各时序参数是否满足规范(如起始/停止条件、数据建立/保持时间)。

-

关注信号边沿质量(tR/tF)和总线电容影响。

②硬件优化:

-

调整上拉电阻值:根据总线电容和模式要求,减小电阻以加快边沿速度(例如,快速模式常用1-10kΩ)。

-

缩短走线长度,减少分布电容和电感。

③软件配置:

-

确保主设备时钟频率(fSCL)与从设备支持的模式匹配。

-

在关键位置增加延时(如起始条件后等待tHD;STA,停止条件后等待tBUF)。

④兼容性设计:

- 混合模式(如高速模式与标准模式设备共存)时,需通过协议切换(如Hs-mode代码头)避免冲突。

3、信号干扰问题

信号干扰也会对 IIC 通信的时序产生负面影响。在实际的硬件环境中,IIC 总线周围可能存在各种电磁干扰源,如其他高速信号线、射频电路等。这些干扰源会在 SDA 和 SCL 线上产生噪声,使信号发生畸变,导致时序出现偏差。

当 IIC 总线与高速 USB 信号线并行布线时,USB 信号的高速切换可能会在 IIC 总线上产生串扰,干扰 IIC 信号的正常传输。为了减少信号干扰,可以采取优化布线的措施,如将 IIC 总线与其他高速信号线分开布局,增加它们之间的距离;使用屏蔽线来传输 IIC 信号,减少外界电磁干扰的影响;在 IIC 信号线上添加滤波电容,对高频噪声进行滤波处理。

待补充。。。。。。

5373

5373

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?