高速先生成员--周伟

上期的文章聊聊1.6T光模块的仿真中做了本期的预告,本期文章开始我们主要聊一下光模块相关的协议,以及怎么从协议里找到我们关心的具体指标。闲话少说,直接上干货。

我们在光模块分类这篇文章中提到了有很多种光模块,因此也对应了很多种不同的协议,但为了不让大家太迷惑,我们特意收缩下范围,计划主要集中讲我们常用的几个协议,所以目前来看我们主要有10Gbps、25/28Gbps、56G-PAM4和112G-PAM对应的协议。接下来我们就针对性的来说说这几种信号的协议吧。

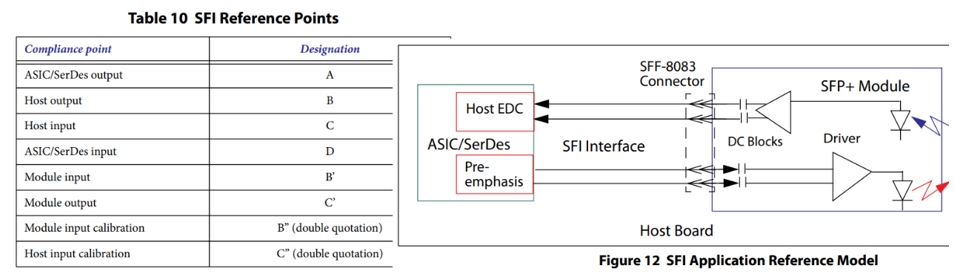

针对10Gbps的光口,我们主要的信号就是SFP+、XFP等,参考的协议主要有SFF8431、10GBase-R和Fiber Channel(10GFC)等,不管是哪个协议基本上都是定义了系统的要求,也就是Host和Module一起。一般10GE光口我们参考SFF8431的协议会比较多,下面就以这个协议来举例说明。在这个协议里面,我们基本没有看到直接有对模块本身的插损要求,只有分段回损要求,另外10G光口的测试上也是结合MCB和HCB来一起看的,大致如下图所示。

基本上按照3种不同的段来进行分段指标要求,一个是Host+HCB的指标,此时是看B和C点的指标要求,其中B点为Host经过HCB输出的端口,这个点对应光模块的B’,也就是从MCB进入模块的端口;C点为进入HCB到Host主板这个点的端口,同时也对应光模块测试点的C’,从光模块的输出到MCB的端口;还有就是A、D两个

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2291

2291

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?