PCB设计中如何防止时钟偏差

在PCB设计中,作为设计者都希望时钟信号能够准确的到达芯片终端。但是在实际应用中,时钟偏差的问题会导致 时钟信号提前或延迟到达某些芯片。这样就会导致芯片的数据完整性不一致。

1. 什么是时钟偏差

时钟偏差是一种时钟信号以不同的间隔到达不同目的地的现象。时钟信号通常用于PCB设计的信号同步。例如,串行外设接口(SPI)使用时钟信号在设备之间发送和接收数据。

理想情况下,主设备到多路从设备传输信号时,时钟信号的传播时间没有延迟。时钟总线上连接的所有设备都应同时接收到信号。然而,在实际应用中,时钟会发生传播延时并且时钟脉冲可以以不同的间隔到达不同的设备。导致时钟偏差的原因主要是寄生电容和时钟信号的长度。

一个时钟信号发送源是同一个,当被分别发送给A和B时,若是A和B的路径长度不一样,这样到达终端设备的时间肯定也不一样。其中这里面的时间偏差便是时钟偏差。

2. 时钟偏差如何影响PCB

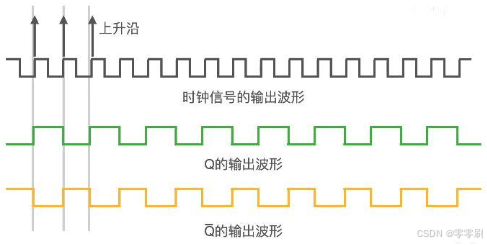

在电子学中,时钟信号用作元器件的时间参考,以锁存接收引脚上的数据位。一些协议在时钟上升沿上锁存数据,而另一些协议在时钟下降沿上锁存数据。无论锁存的机制如何,稳定可靠的时序参考都很重要。

在出现时钟偏差的情况下,时钟信号可能比预期到达的更早或更晚。当时钟

订阅专栏 解锁全文

订阅专栏 解锁全文

3001

3001

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?