DDR时序约束

1. 介绍

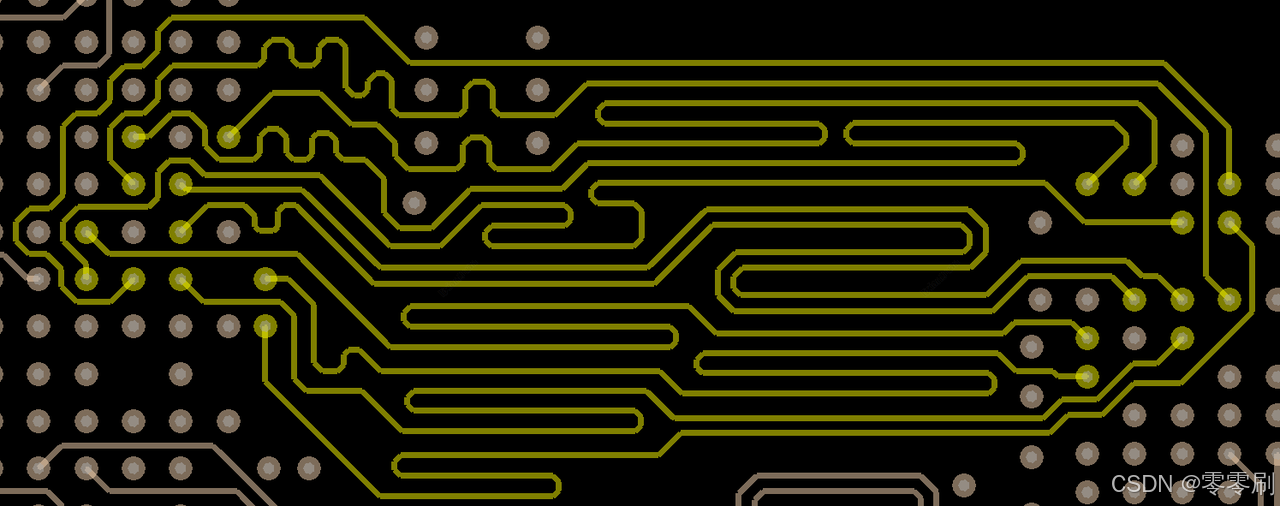

- 线长匹配:DDR的线长误差控制为±10mils,这个对于时序很重要,以防止数据损坏和操作故障。

- 阻抗控制:常规下单端阻抗控制为50Ω,差分线阻抗控制为90Ω,需保持阻抗的一致性,以避免信号反射和损耗。

- DDR布线工具:用Allegro提供的Auto Delay Tune和Timing Vision等高级功能,以实现有效的DDR走线和约束管理。

DDR布线必须遵守解决现有电气挑战的设计指导,以保持信号完整性和功能。设计者首先要考虑DDR的时序约束从而再进行设计,这对于消除静电和确保信号质量至关重要。将约束或设计规则应用于DDR布线设计中。

2. DDR的介绍

PCB布线中通常会用到双倍数据速率(DDR)存储器。顾名思义,DDR存储器允许在单个时钟周期内发生两次数据位转换,从而使在单个周期内使数据量增加一倍。“double data rate” 意味着它可以在时钟时序的上升沿和下降沿上获取数据,这点与RAM不同,RAM仅在一个时钟沿上获取数据。考虑到DDR时序约束,存储器件通常采用手动布线,以保证对布线问题的控制,例如地址、数据和控制信号之间的间距。

订阅专栏 解锁全文

订阅专栏 解锁全文

5221

5221

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?