人生中第一遍博客哈哈哈,本人现在准大三,在暑假里既没有参加电赛,也没有其他事,所以目前在学习朱有鹏老师的嵌入式物联网课程,今天学到了打开和关闭icache的操作,话不多话,我来分享一下我学习的知识和经验吧。

1. iCache简介

- 我用我自己的话我对icache的理解说一下吧:iCache实际上就是一种内存,它是Cache的一种,Cache主要用于高速的缓存,如果说两种传输介质的传输速度相差太大的话,就可以用Cache来进行缓冲,我曾经在做51单片机的AD采样的时候,由于51单片机的内部没有自带有AD转换的功能,所以当时采用了一款高速的AD采样芯片(20M以上),但是由于51单片机的速度实在太慢,所以说在这两者之间就有传输和处理的速度差了,AD发过来的数据太快,51处理的太慢,所以在这种情况下,就是可以用Cache缓冲的,而在芯片内部,也有Cache的原因在于CPU和DDR之间传输数据的时候,这两者的处理速度也是差别很大的,所以说要加上Cache,以增加数据传输的速度(为什么在后面会说明)

- iCache是Cache的一种,Cache有iCache和DCache两种,其中iCache用于存指令,DCache用于存数据。

2. iCache加快传输数据的原理

- 在没有iCache的情况下,CPU是如何读取指令的呢?我们知道平时程序和指令平时存储在flash中,当需要的时候,就会从flash被调用到内存中去,再从内存调用到寄存器中,最后再被CPU调用,当加了iCache后,就在寄存器和内存中间加了一个缓冲区,而iCache它的特性就是会从flash中把程序中很多条指令一次性都加载到其中去,只要不发生特殊的情况,执行当前一句代码的下一句代码的可能性要大很多,因此,CPU就可以不必从读取速度低的内存中读取指令,而是可以从相对高速的iCache中读取,iCache就是这样的机制,其增加的速度就是iCache和内存存取速度的差,当然,一切都建立在程序正常执行的情况下。

3.S5PV210中的iCache

- 如上图所示即为S5PV210中的iCache示意,其中分别有32KB的iCache和32KB的dCache

- 那么我们该如何打开关闭iCache呢,这里就必须要讲到ARM的CP15协处理器了

4.ARM的CP15协处理器

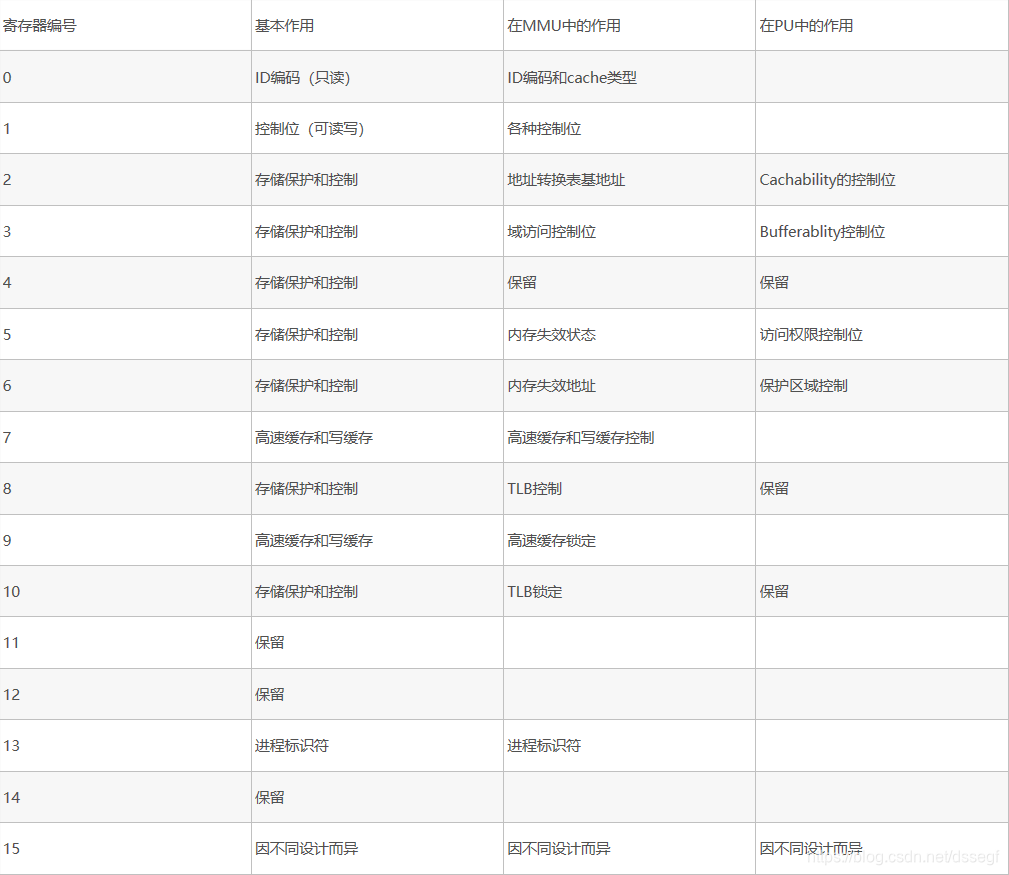

- ARM的CP15协处理器中有0-15共16个寄存器,其中每个寄存器的作用如下图所式(图片来自于网络):

在这里我们要对ICache进行操作,主要就是操作CP15的寄存器C1

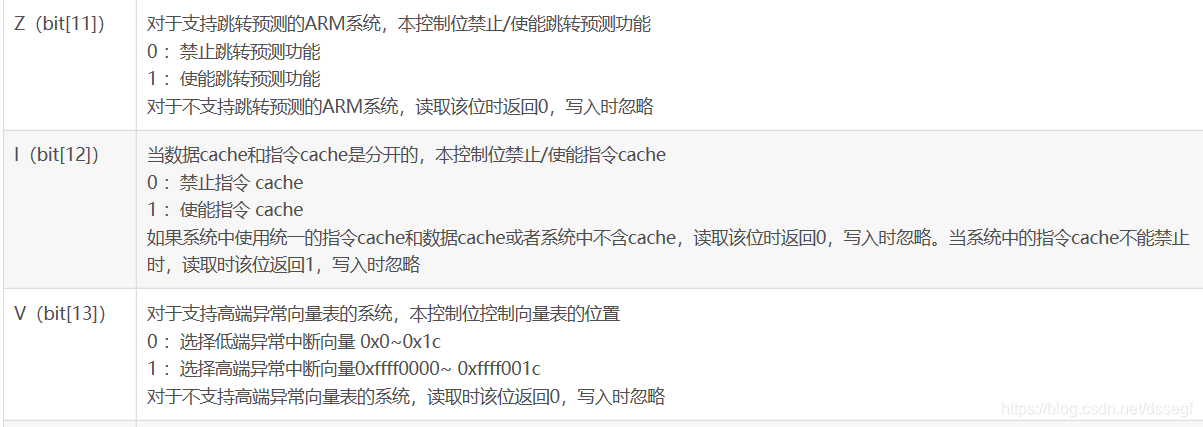

下图是C1寄存器中各部分控制位的作用(只截取了部分控制位的描述):

这样我们已经很清楚了,只要我们在CP15中的C1的I控制位(bit12),写入0或1,就可以禁止或者使能iCache

5.使用mrc和mcr指令开启关闭iCache

- 我们使用ARM汇编的指令对寄存器中的位进行操作,观察效果

- mrc指令:用于读取协处理器中的寄存器

- mcr指令:用于把数据写入到协处理器中的寄存器中

MRC {cond} coproc,opcode1,Rd,CRn,CRm,opcode2

MCR{cond} coproc,opcode1,Rd,CRn,CRm,opcode2 - 这里我想用比较通俗的语言解释一下各个部分的意义

coproc:就是说需要使用哪一个协处理器这里就填它的编号就OK,我们使用的是CP15,就写p15就可以

opcode1:对于CP15寄存器来说,opcode1永远为0,不为0时,操作结果不可预知

Rd:目标寄存器的协处理器寄存器,就是说需要读取的那个寄存器

CRn: 存放第1个操作数的协处理器寄存器. ,填写读取出来的值存放到哪一个寄存器中

CRm: 存放第2个操作数的协处理器寄存器. (用来区分同一个编号的不同物理寄存器,当不需要提供附加信息时,指定为C0),这里不需要提供附加信息时,指定为C0

opcode2:可选的协处理器特定操作码. (用来区分同一个编号的不同物理寄存器,当不需要提供附加信息时,指定为0),这里指定为0

因此我们读取的操作就为:

mrc p15,0,r0,c1,c0,0; // 读出cp15协处理器的c1到r0中

然后我们使用bic 命令使bit12置0以关闭iCache,bic指令的使用方法就是哪一位置1,哪一位就变成0了,bic命令的具体操作可以参考下面的链接:arm汇编 bic和orr指令

bic r0, r0, #(1<<12) // bit12 置0 关icache

同理可以使用orr命令使bit12置1以开启iCache

orr r0, r0, #(1<<12) // bit12 置1 开icache

然后使用mcr指令再把r0中的数据写入到CP15的c1寄存器里面去

mcr p15,0,r0,c1,c0,0;

6.补充说明

- 由于S5PV210启动时,iCache是自动开启的,所以说在这里开启iCache的操作没有多大意义

- 之前学习的时候总有疑惑,为什么不直接把数据写到CP15的c1里面去呢?后来明白了朱有鹏老师把值读出来,再只改变bit12的值,最后再写到c1里面去的做法是很有道理的,因为我们必须保证在c1中只有bit12改变,而其他位的值不能改变,因此需要采用这种似乎看起来比较麻烦的方法。

7.试验现象

- 在尝试把500ms的流水灯程序分别用开启或者关闭iCache条件下进行试验,发现关闭iCache后,流水灯延时的时间有了明显的延长,说明iCache的开关确实非常影响CPU的处理速度

本文详细解析了iCache的工作原理及其对CPU处理速度的影响。通过对比开启与关闭iCache的流水灯程序运行时间,证实了iCache的重要性。同时,介绍了如何通过ARM汇编指令操作CP15协处理器寄存器C1来实现iCache的开关。

本文详细解析了iCache的工作原理及其对CPU处理速度的影响。通过对比开启与关闭iCache的流水灯程序运行时间,证实了iCache的重要性。同时,介绍了如何通过ARM汇编指令操作CP15协处理器寄存器C1来实现iCache的开关。

837

837

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?