文章目录

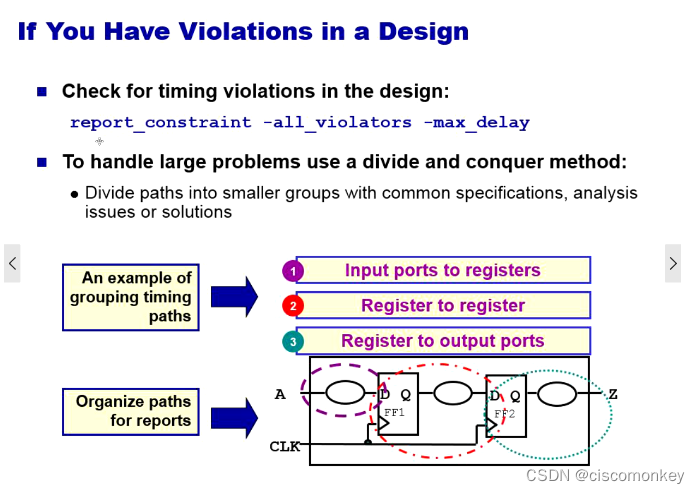

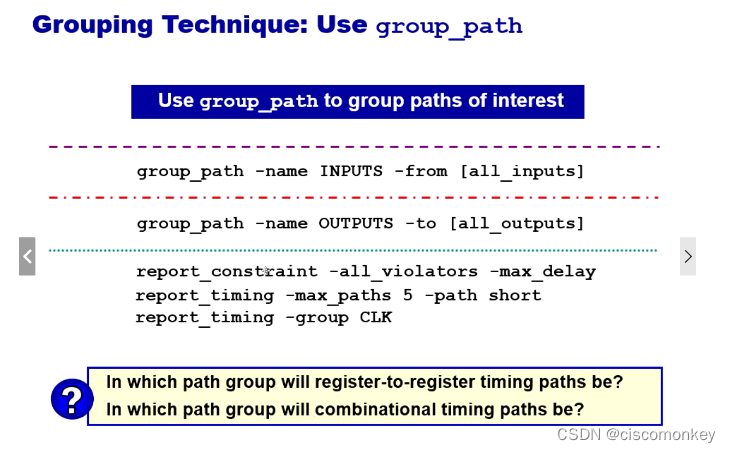

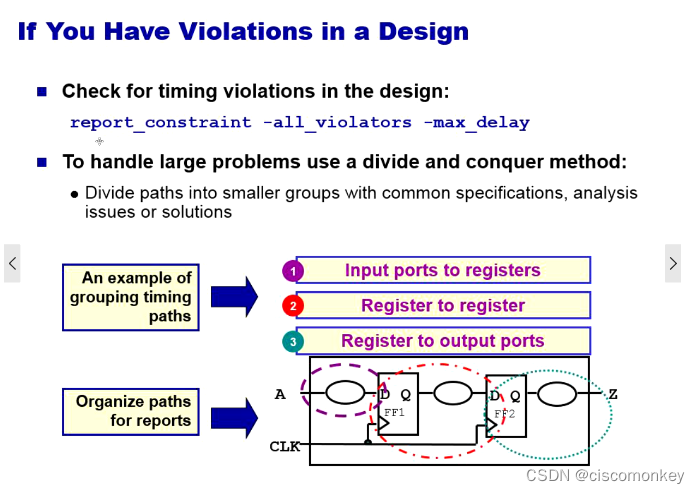

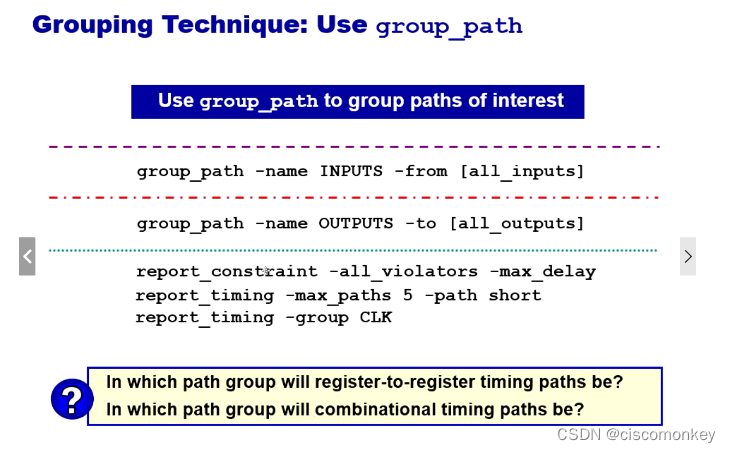

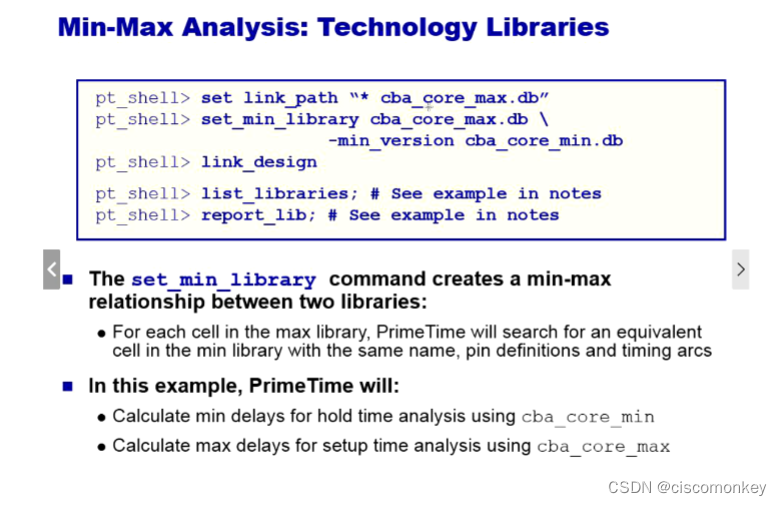

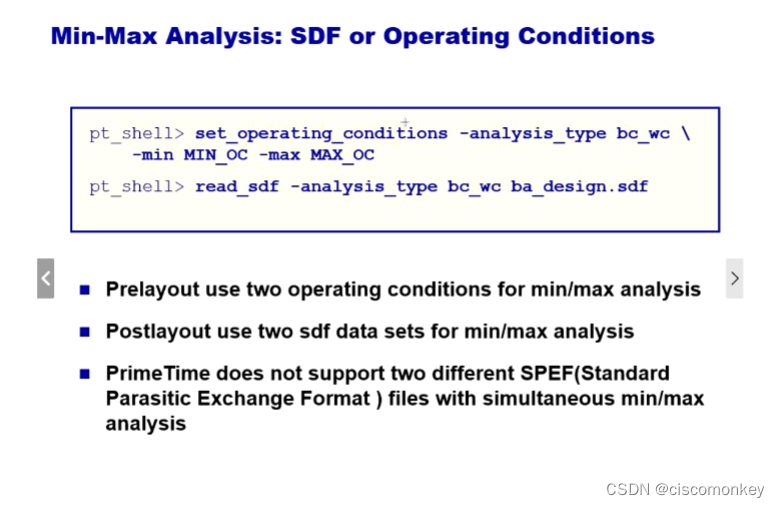

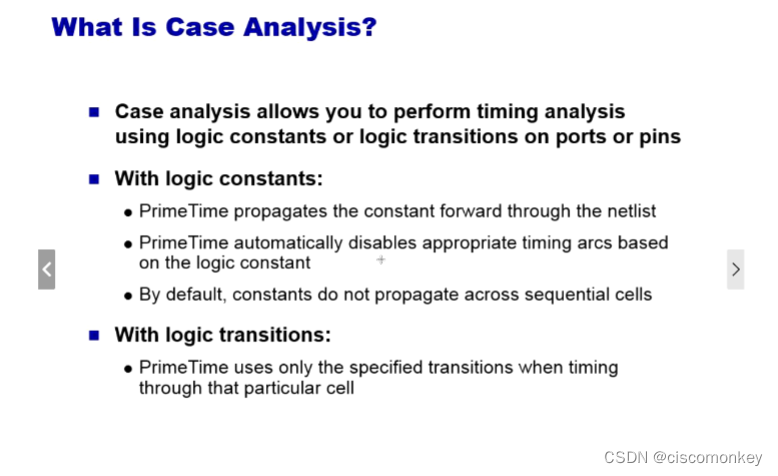

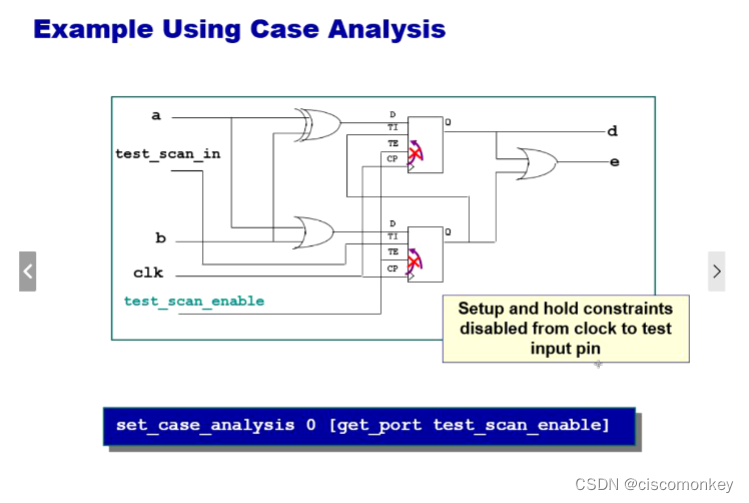

本篇文章介绍的是如何去分析timing

由于博客内容为空,暂无法提供包含关键信息的摘要。

由于博客内容为空,暂无法提供包含关键信息的摘要。

7853

7853

5404

5404

1889

1889

6332

6332

2115

2115

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?