一、NIOS-Ⅱ简介

- 2004年,Altera 正式推出了Nios II 系列32位RISC嵌入式处理器:Nios

II系列软核处理器是Altera的第二代FPGA嵌入式处理器,其性能超过200DMIPS,在Altera

FPGA中实现仅需35美分。Altera的Stratix 、Stratix GX、 Stratix II和

Cyclone系列FPGA全面支持Nios II处理器,以后推出的FPGA器件也将支持Nios II。- Nios Ⅱ系列包括3种产品,分别是:

Nios Ⅱ/f(快速)——最高的系统性能,中等FPGA使用量;

NiosⅡ/s(标准)——高性能,低FPGA使用量;

Nios Ⅱ/e(经济)——低性能,最低的FPGA使用量。

这3种产品具有32位处理器的基本结构单元——32位指令大小,32位数据和地址路径,32位通用寄存器和32个外部中断源;使用同样的指令集架构(ISA),100%二进制代码兼容,设计者可以根据系统需求的变化更改CPU,选择满足性能和成本的最佳方案,而不会影响已有的软件投入。- 特别的,Nios Ⅱ系列支持使用专用指令。专用指令是用户增加的硬件模块,它增加了算术逻辑单元(ALU)。用户能为系统中使用的每个NiosⅡ处理器创建多达256个专用指令,这使得设计者能够细致地调整系统硬件以满足性能目标。专用指令逻辑和本身NiosⅡ指令相同,能够从多达两个源寄存器取值,可选择将结果写回目标寄存器。同时,NiosⅡ系列支持60多个外设选项,开发者能够选择合适的外设,获得最合适的处理器、外设和接口组合,而不必支付根本不使用的硅片功能。

——摘自百度百科

-

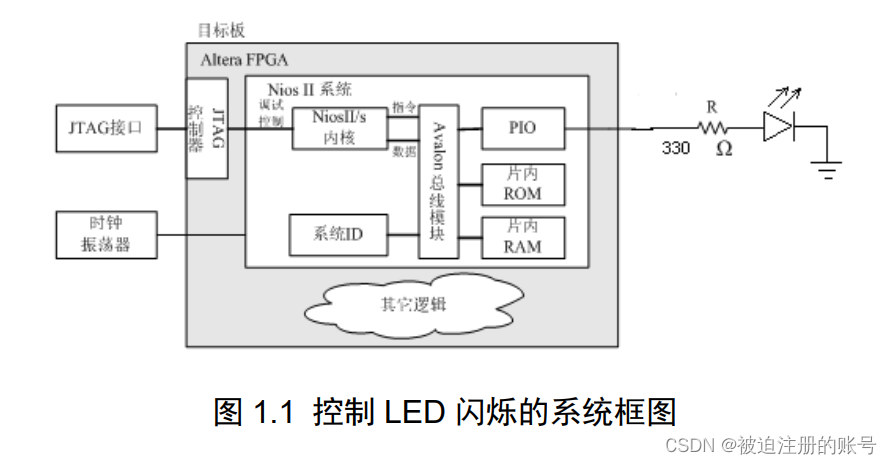

本次实验需要在FPGA上通过Nios Ⅱ软核完成流水灯控制,由于控制 LED 灯闪烁的用户程序代码很小,可将其固化在片内 ROM 来执行。变量、堆栈等空间使用片内 RAM,不使用任何片外存储器。整个系统的框图如图 1.1 所示。

-

从图 1.1 控制 LED 闪烁的系统框图可知,其它逻辑与 Nios II 系统一样可存在于 FPGA中。Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。为了简单起见,本实验在 FPGA 内不包括其它逻辑。

二、创建项目

1.在Quartus18.0中新建一个工程

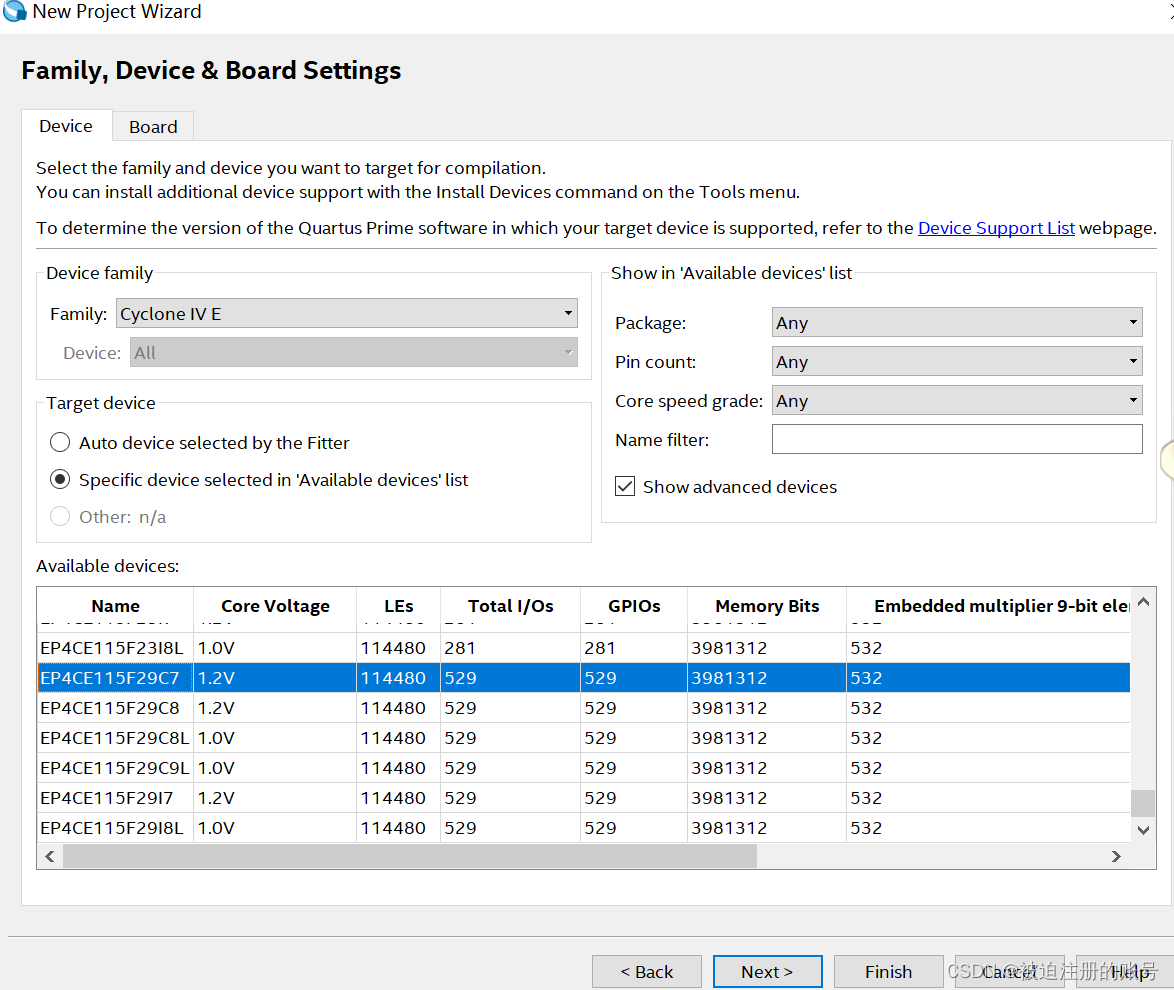

选择如图所示的芯片,直接Finish即可

2.Qsys设计

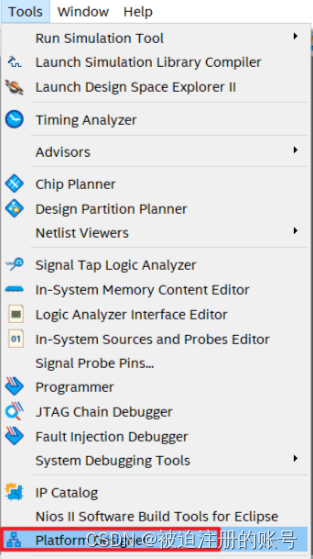

(1)进入Tools -> Platform Designer

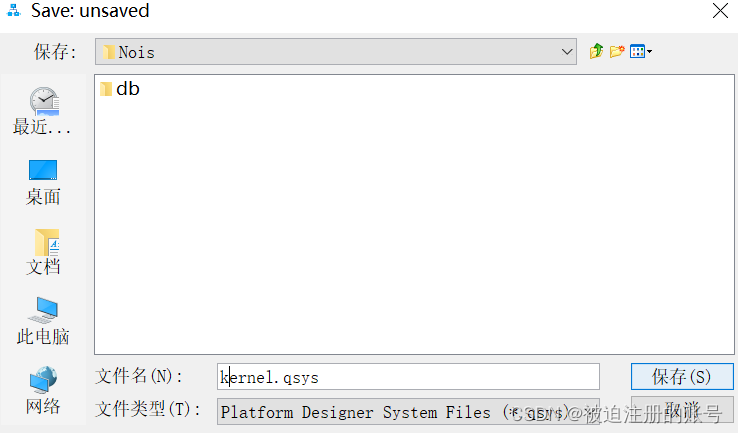

进入后,首先点击File -> Save ,保存为Kernel.qsys

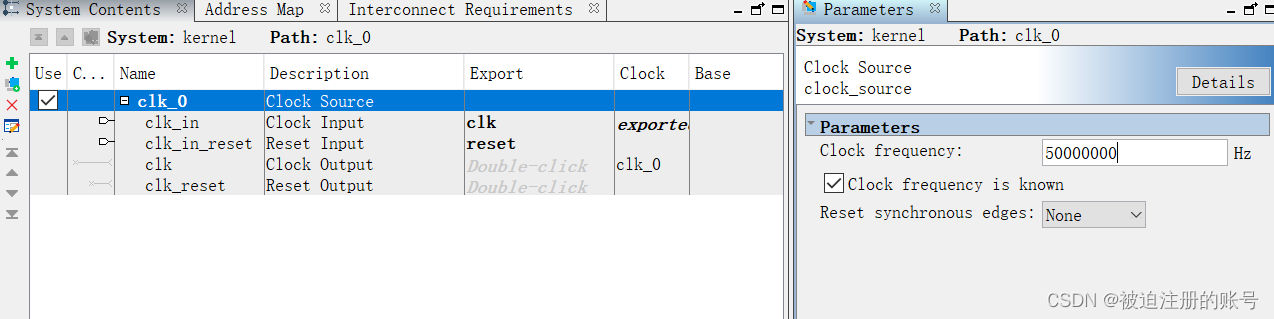

(2)设置时钟主频

双击clk_0,将时钟调整为50MHz

(3)添加 CPU 和外围器件

从 PD 的元件池中选择以下元件加入到当前设计的系统中:Nios II 32-bit CPU、jtag uart、片上存储器、PIO、system ID

- 添加 Nios II 32-bit CPU

在“component

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1352

1352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?