Logsim使用

参考

Logisim的基本使用方法(详细)教你如何使用Logisim-优快云博客

鼠标点击左边栏“逻辑门”旁边的小三角,会出现“异或门”,“与非门”等,鼠标点击其中的一个就可以拖到右边的白板中。

第二栏的小手是来改变输入的,箭头是用来连线的,“A”是用来编写文字的。

熟悉了就可以构建虚拟电路了。

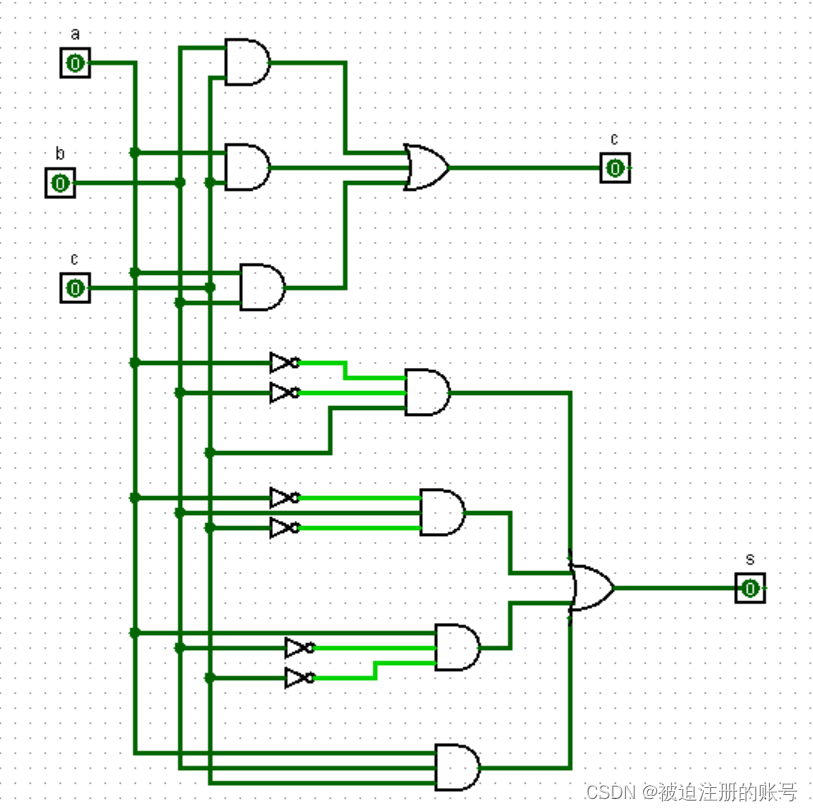

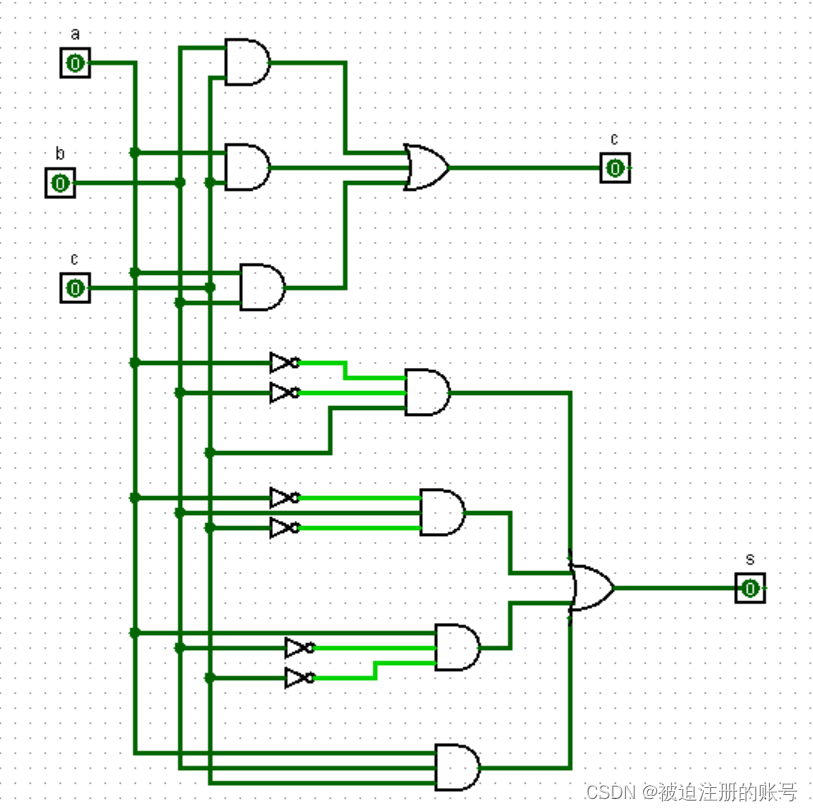

1位全加器

1bit

4bit

相同的元件直接Ctrl+D即可复制

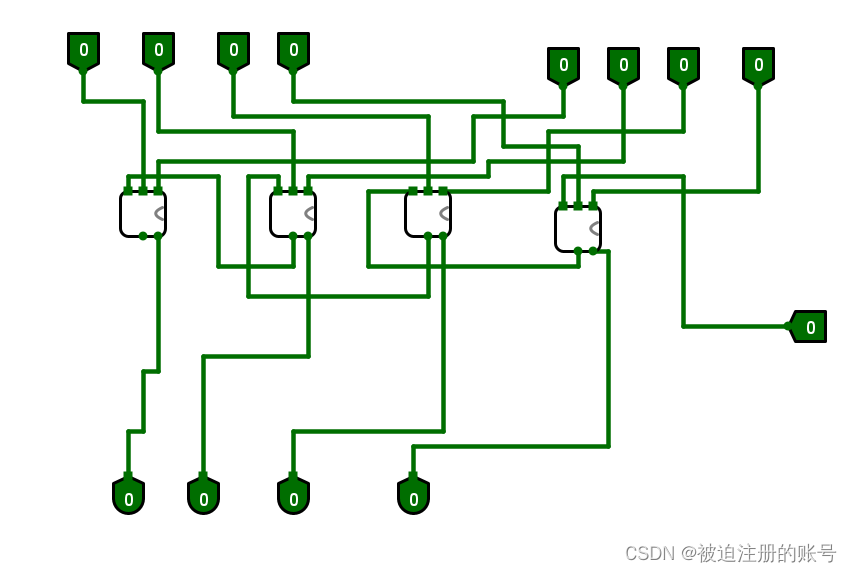

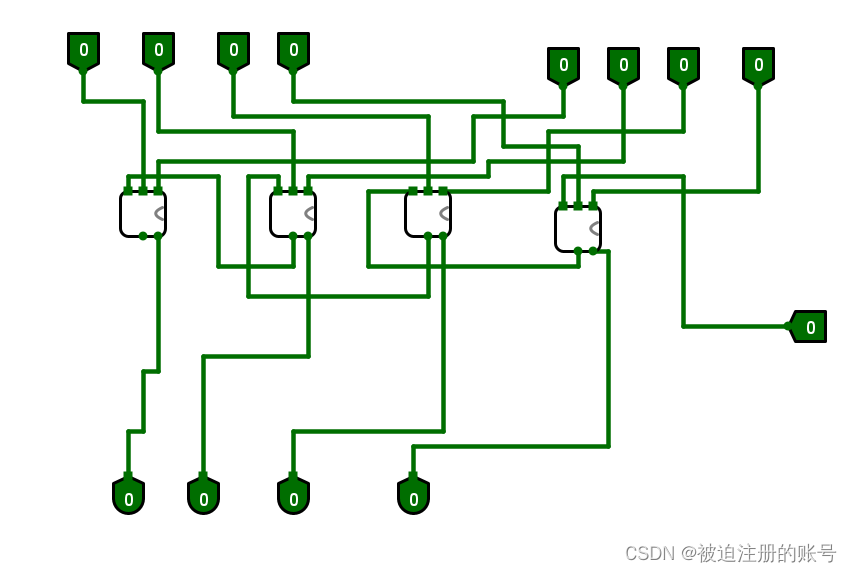

4位全加器

将4个封装后的1位全加器串联

本文介绍了Logisim软件的基本使用方法,包括逻辑门的选择、操作界面说明(如鼠标、输入控制和连线功能),并以1位和4位全加器为例,展示了如何构建和复制电路。

本文介绍了Logisim软件的基本使用方法,包括逻辑门的选择、操作界面说明(如鼠标、输入控制和连线功能),并以1位和4位全加器为例,展示了如何构建和复制电路。

参考

Logisim的基本使用方法(详细)教你如何使用Logisim-优快云博客

鼠标点击左边栏“逻辑门”旁边的小三角,会出现“异或门”,“与非门”等,鼠标点击其中的一个就可以拖到右边的白板中。

第二栏的小手是来改变输入的,箭头是用来连线的,“A”是用来编写文字的。

熟悉了就可以构建虚拟电路了。

1bit

4bit

相同的元件直接Ctrl+D即可复制

将4个封装后的1位全加器串联

5054

5054

2万+

2万+

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?