1.实验目的:

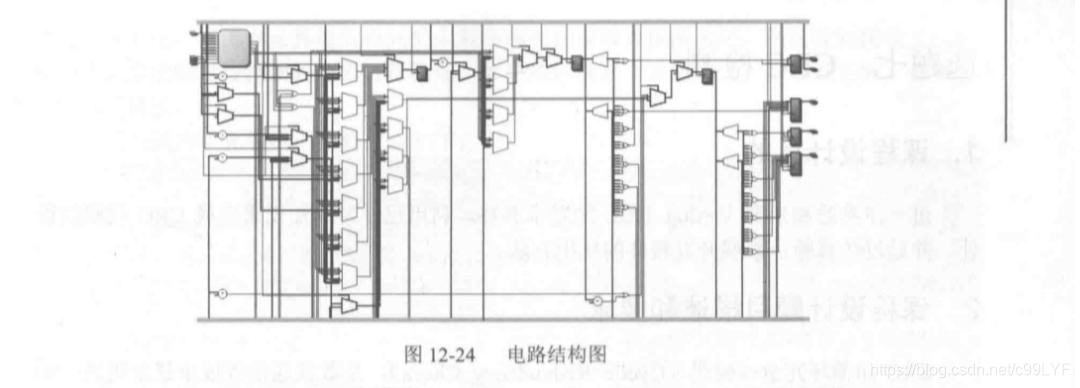

使用verilog HDL硬件描述语言乒乓球游戏电路设计

2.实验内容:

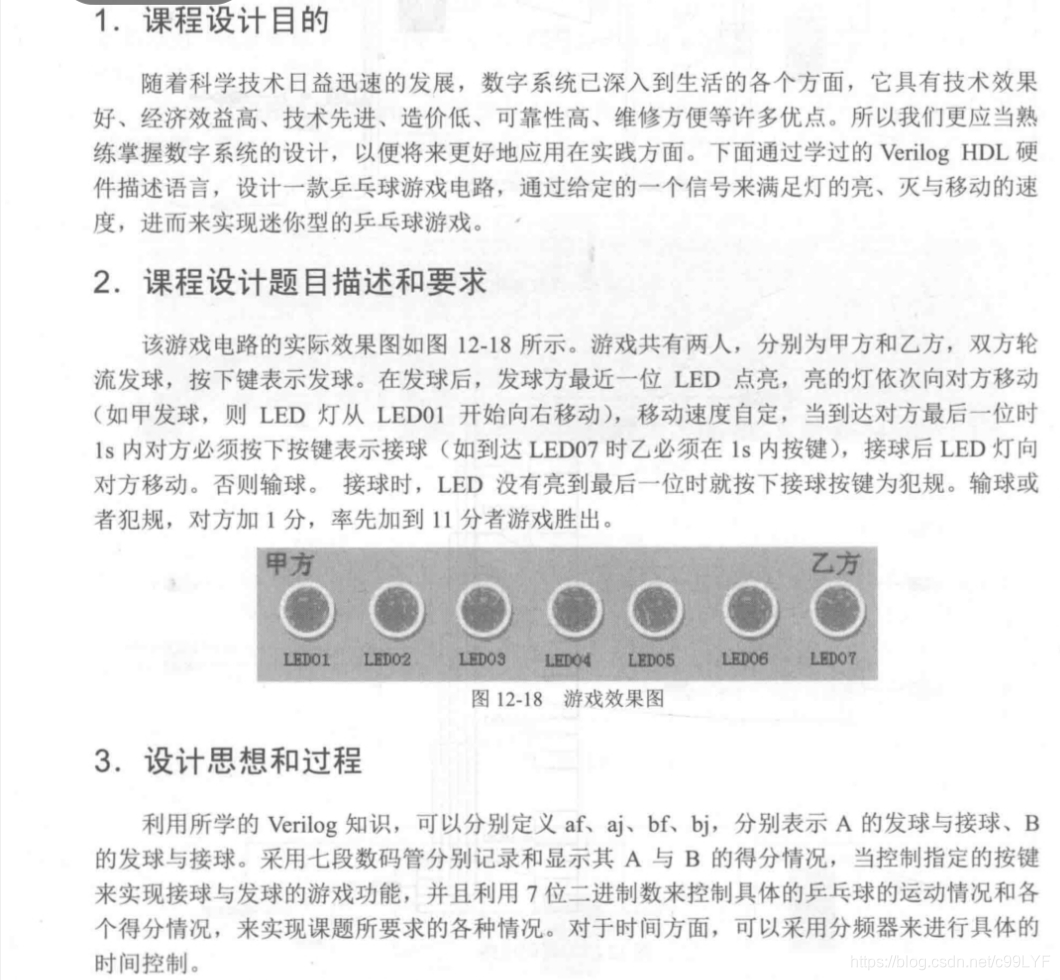

3.实验原理:按照视书上的内容,书写和运行代码,完成仿真操作

实验代码:

(1)

module pingp(clk, reset, push1, push0, led, decode1, decode2, decode3, decode4, clk_out);

input clk, reset;

input push1, push0;

output [6:0] led, decode1, decode2, decode3, decode4;

output clk_out;

fenpin hz(clk, reset, clk_out);

ctl ctll(.clk(clk),.reset(reset),.push1(push1),.push0(push0),.led(led),

.decode1(decode1),.decode2(decode2),.decode3(decode3),.decode4(decode4));

endmodule

module ctl(clk, reset, push1, push0, led, decode1, decode2, decode3, decode4);

input clk, reset;

input push1, push0;

output [6:0] led, decode1, decode2, decode3, decode4;

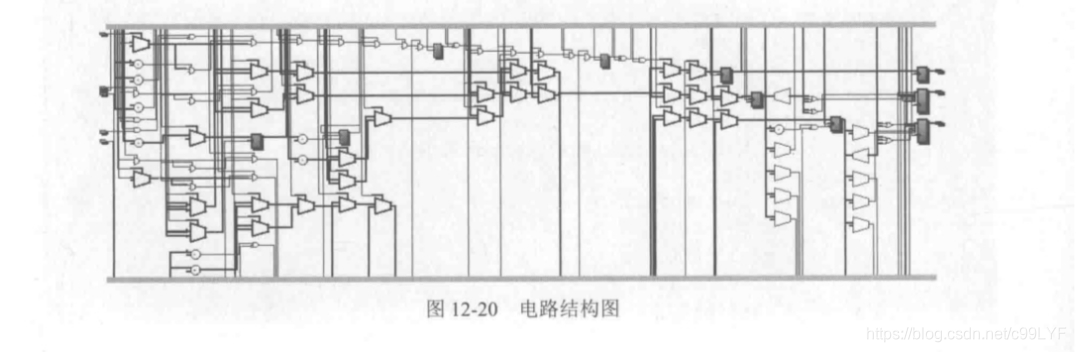

reg [3:0] M,N;

reg [6:0] led, decode1, decode2, decode3, decode4;

reg [2:0] state;

parameter s0=3'b000,

s1=3'b001,

s2=3'b010,

s3=3'b011,

s4=3'b100;

always@(posedge clk)

begin

if(reset)

begin

led<=7'b0000000;

M<=4'b0000;

N<=4'b0000;

end

else

begin

case(state)

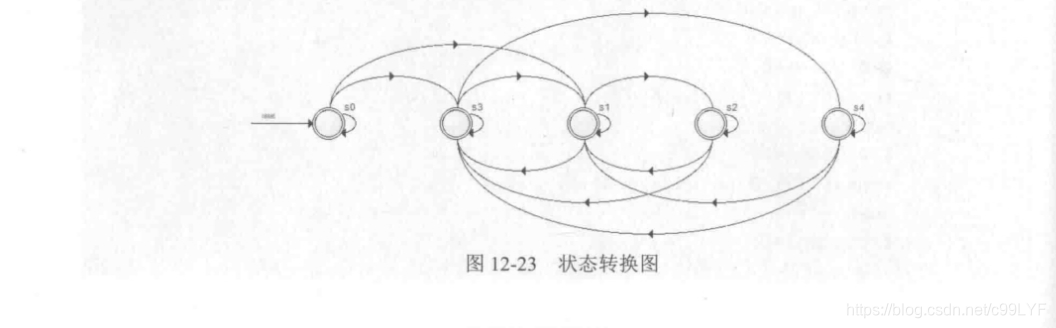

s0: //初始发球

begin

led<=7'b0000000;

if(push0)

begin

state<=s1;

led<=7'b1000000;

end

else if(push1)

begin

state<=s3;

led<=7'b0000001;

end

end

s1: //甲发球或甲接球后,球的移动

begin

if(push1)

begin

state<=s0;

M<=M+4'b0001;

end

else if(led==7'b0000001)

begin

state<=s2;

end

else

begin

state<=s1;

led[6:0]<=led[6:0]>>1;

end

end

s2:if(push1) //乙接球

begin

state<=s3;

led

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2122

2122