单端鲁棒低功耗8T SRAM单元的设计与分析

1 引言

随着静态随机存取存储器在集成电路中因高密度和稳定性而被广泛使用,对SRAM的需求正在增加[1]。

低功耗电路的需求不仅在逻辑电路中迅速增长,在存储元件中也同样如此。因此,必须降低SRAM单元的功耗。本文提出了一种8T SRAM单元,以在电路级上减少漏电、静态和动态功耗。目前有多种技术可用于降低待机功耗。其中一种是采用睡眠技术,该技术通过使用高阈值电压的p型MOSFET切断单元的电源电压,并通过使用高阈值的n型MOSFET断开接地路径,从而降低待机功耗[2]。然而,这种方法存在严重局限性,即由于亚阈值漏电流与阈值电压呈指数关系,导致亚阈值漏电流显著增加。为解决此问题,本文提出了一种动态可变电压电平技术,可显著降低功耗和漏电流。本研究描述了利用该技术降低电源电压并提高地电平电位,以最大程度地减少漏电流和功耗[3]。

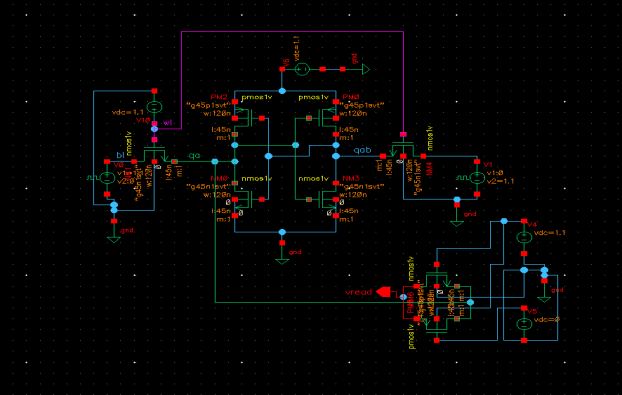

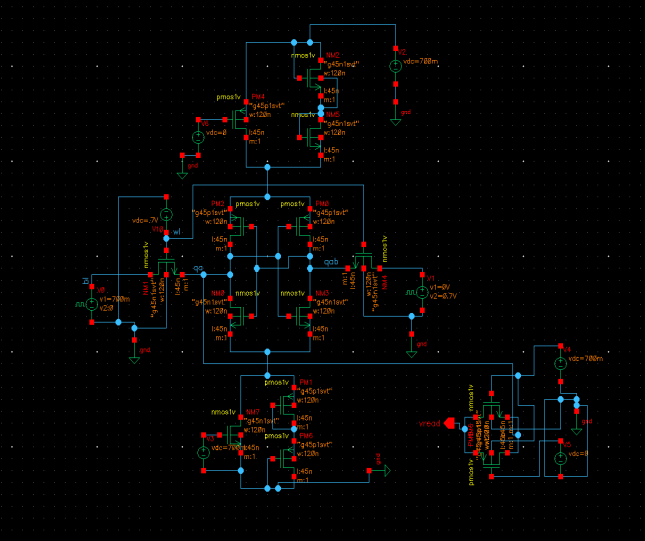

本文提出了一种基于45纳米技术的8T SRAM单元,该单元由八个晶体管组成,其中两个反相器交叉耦合(M1、M2、M3、M4),晶体管M5和M6为访问晶体管,M7和M8为读取访问晶体管,构成一个传输门。

本文的结构如下:第2节描述了所提出的8T SRAM单元及其读写操作。第3节描述了该电路中的漏电流及功耗。第4节描述了各种技术。第5节给出了简要结论。

2 电路的读写操作

所提出的8T SRAM单元具有三种工作模式,即写入模式、读取模式和保持模式。写操作开始时,先切断电路中的传输门连接,然后将需要写入的数据放置在 BL上,其互补数据放置在位线反(BLBAR)上。Q 和Qb是两个存储节点。M1和M2是上拉PMOS晶体管, M3和M4是下拉晶体管。字线(WL)负责在激活和保持模式下保持数据。该SRAM单元由两个交叉耦合反相器构成,即反相器1(inv1)后接反相器2(inv2),第一个反相器的输出作为第二个反相器的输入,反之亦然。在此单元中,使用一个传输门来读取数据。RWLB是RWL信号的反相。当RWL和 RWLB均被置位且传输门导通后,存储在节点Q处的数据将被传输并读出[4]。

传输门的一个主要优点是,它消除了传统8T SRAM单元在读取时所需的传感器放大器和预充电电路,从而降低了功率。

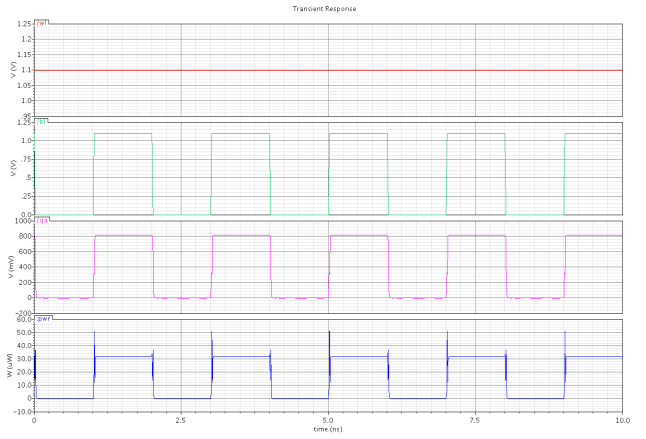

2.1 读取和写入波形

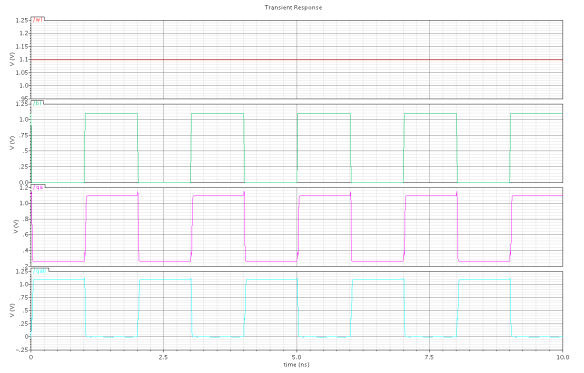

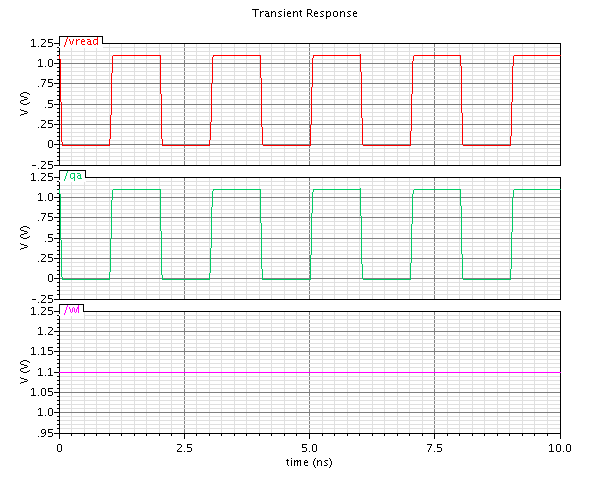

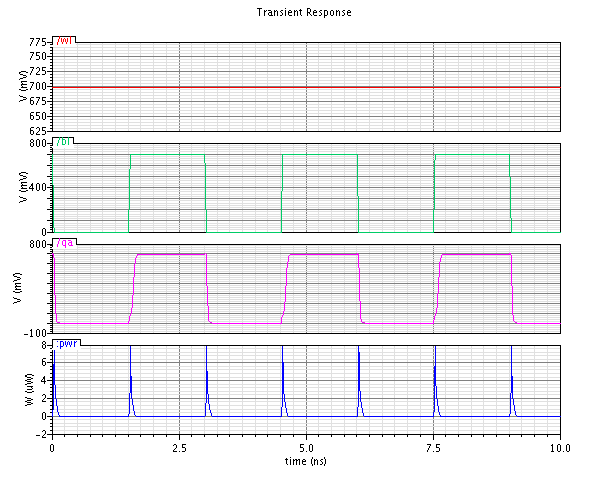

读操作 :在读操作期间,存储在Q节点的数据被传递到传输门的输入端,此时两条字线RWL和RWLB均被置位。然后从读路径rout获取输出。

写操作 :在写操作期间,需要写入的数据被放置在位线(Bit Line)上,其互补数据被放置在BLBAR上,随后字线(WL)被置位为高电平。

保持模式 :在保持期间,字线保持关闭,单元处于空闲状态[5]。写操作和读操作的输出波形如图2和图3所示。

3 漏电流

导致漏电流的因素有多种,例如PN结反向偏置电流、亚阈值漏电、漏致势垒降低、体效应、栅氧化层隧穿、热载流子注入、栅致漏极漏电和穿通。但漏电流的主要来源是亚阈值漏电。亚阈值电流是指当MOS晶体管的栅极电压低于阈值电压时,在源极和漏极之间流动的电流。当晶体管处于关态时,可根据以下公式得到漏电流 [6]。

$$ I_{sub} = I_o \left(1 - e^{-\frac{V_{DS}}{nV_T}}\right) $$

其中,$ I_o = \mu C_{ox}(w/l_{eff}) \cdot \frac{nV_T}{q} $,W为宽度,L为长度,$\mu$为载流子迁移率,$V_T$为热电压,$\eta$为漏致势垒降低系数,n为亚阈值摆幅系数。$V_{TH}$为阈值电压,$V_{GS}$为栅源电压。

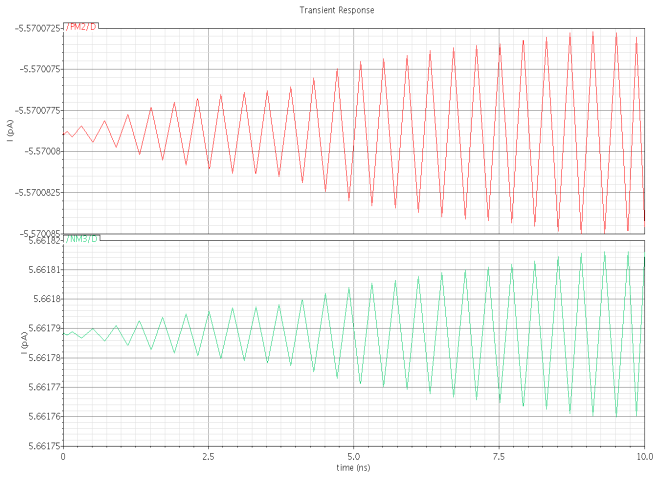

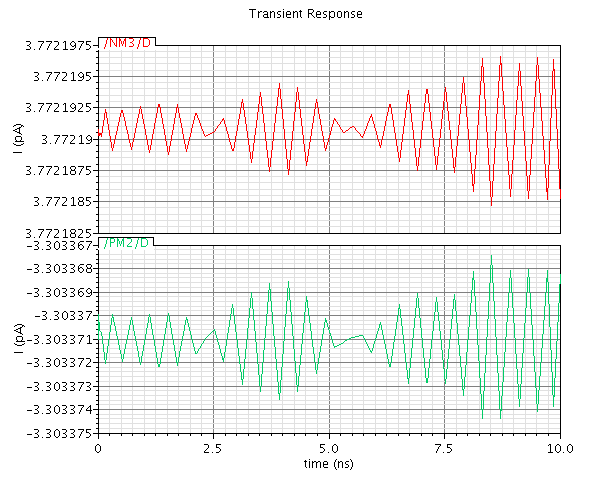

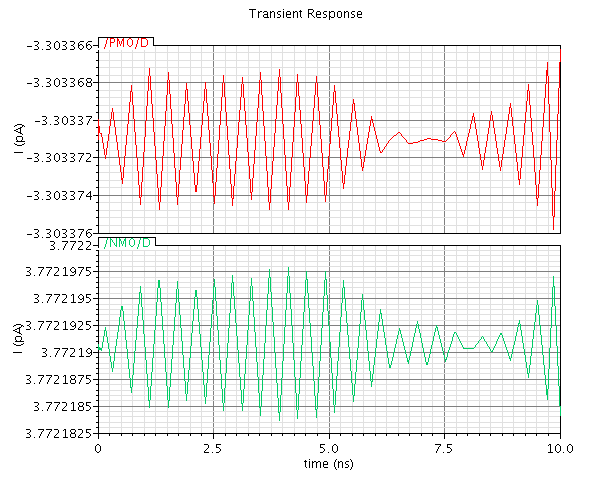

3.1 漏电流是针对在操作期间处于关断状态的特定晶体管进行计算的。

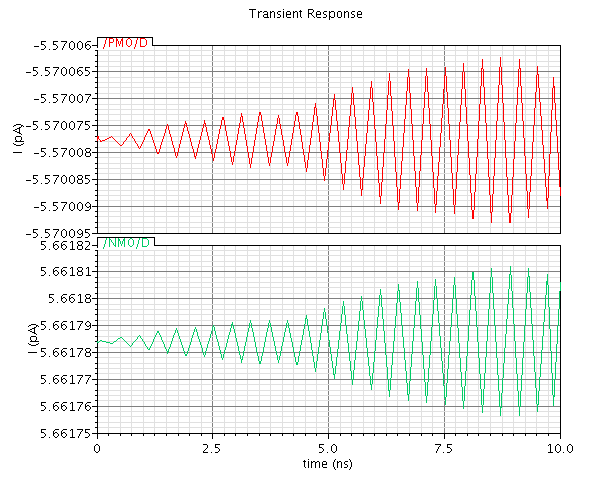

A) 在Q节点写入1

在Q节点写入1时,晶体管M2和M3将处于关闭状态,因此我们将从这两个节点获取漏电流。

M2晶体管的漏电流 = 4.27 pA

M3晶体管的漏电流 = -10.43 pA

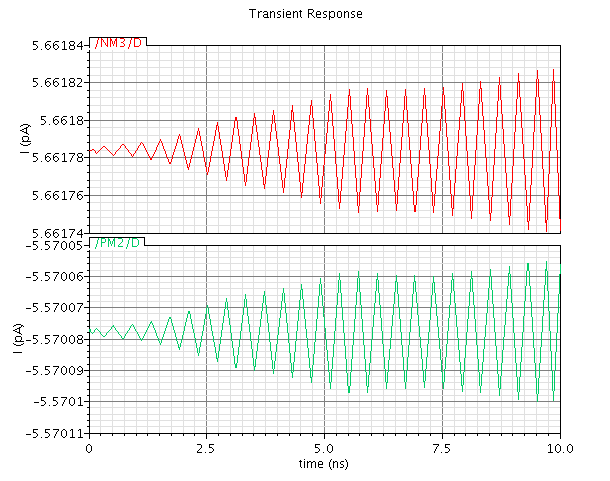

B) 在Q节点写入0

对于在Q节点写入0的情况,晶体管M1和M4将处于关闭状态,因此我们将从这两个节点获取漏电流。

M1晶体管的漏电流 = 5.66 pA

M4晶体管的漏电流 = -5.57 pA

3.2 功耗

SRAM单元的功耗是静态和动态功耗的总和。静态功耗是由于漏电流[7]引起的。

动态功耗有以下几种类型:

a) 开关:由于寄生电容引起的电流充放电所致。

b) 短路:由于输入变化缓慢,即在反相器中当PMOS和 NMOS同时导通时,导致短路功耗。

在45纳米技术下,通过对两条位线施加电压脉冲且字线被置位,并进行瞬态分析来计算动态功耗[8]。

4 漏电流和功耗控制技术

4.1 动态可变电压电平技术

在此技术中,电源电压不直接连接到SRAM单元,而是通过一个PMOS与两个串联的NMOS晶体管并联来设置一个较高的动态电压。同时,使用一个NMOS与两个串联的PMOS并联来提升地电位。该技术在工作模式下使地节点电压为0伏,在待机模式下则提高地电压。在上层电压节点处,该技术在工作模式下提供完整的Vdd电压,而在待机模式下将电源电压降低至Vd电平。

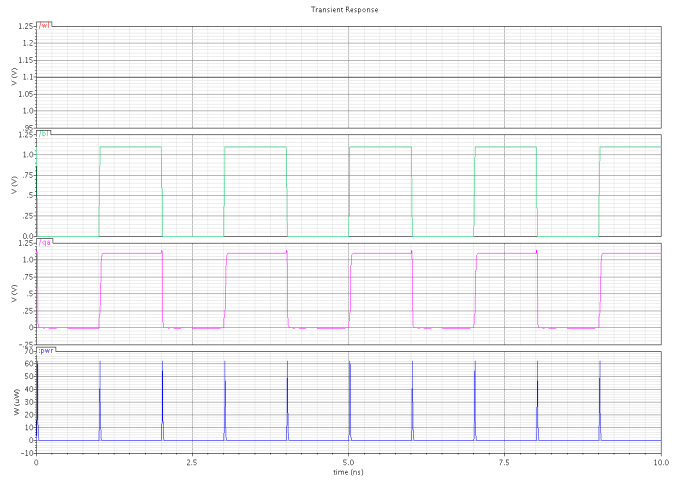

仿真结果显示了功耗的降低,如图8所示。

4.2 电源电压缩放结合动态可变电压电平技术

图9显示了结合技术的示意图,其中电源降低至0.7V。

表1显示了传统的8T SRAM单元与提出的两种技术之间的比较。与传统的8T相比,提出结构的总功耗降低了98.8%,这是由于电源电压缩放与动态VVL技术相结合所致。

表1. 动态功耗方面的比较

| 耗功散率 | 传统的 8T SRAM | SVL 技术 | 功率缩放结合 with SVL 技术 |

|---|---|---|---|

| 静态 | 3.19 uW | 32.1 pW | 8.42 pW |

| 动态 | 16.1 uW | 736.3 nW | 181 nW |

表2. 漏电流方面的比较

| 漏电流 | 传统的 8T SRAM | SVL 技术 | 功率缩放结合 with SVL 技术 |

|---|---|---|---|

| Write‘1’(NMOS, PMOS) | 4.27 pA, -10.43 nA | 5.66 pA, -5.57 pA | 3.3 pA, -3.3 pA |

| Write‘0’(NMOS, PMOS) | 5.66 pA, -5.77 pA | 5.66 pA, -5.57 pA | 3.3 pA, -3.3 pA |

5 结论

随着CMOS技术缩放到45纳米,功耗已成为超大规模集成电路设计中的一个非常关键的问题。本文提出了一种低功耗单端8T SRAM单元。针对45纳米技术的8T SRAM单元中的漏电流和功耗分析表明,漏电流在待机模式下的总功耗中占据显著比例。本文详细研究了采用动态VVL技术降低电源电压并提高地节点电压以减少漏电流的方法。分析表明,在写操作中,结合VVL技术降低电源电压可显著降低静态和动态功耗。

尽管提出的SRAM单元在延迟和面积上有所增加,但低功耗的优势可以弥补这一缺点。因此,该提出的SRAM单元可广泛应用于笔记本电脑、手机、存储卡等领域,以提供低功耗优势。综上所述,这些技术已显著降低了8T SRAM单元中的漏电流和功耗。

987

987

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?