1.1 UVM是什么?

UVM 是 Universal Verification Methodology 的缩写,即通用验证方法学。它起源于 OVM(Open Verification Methdology),是由 Cadence, Mentor 和 Synopsys 联合推出的新一代的验证方法学。

1.1.1UVM主要用在什么地方

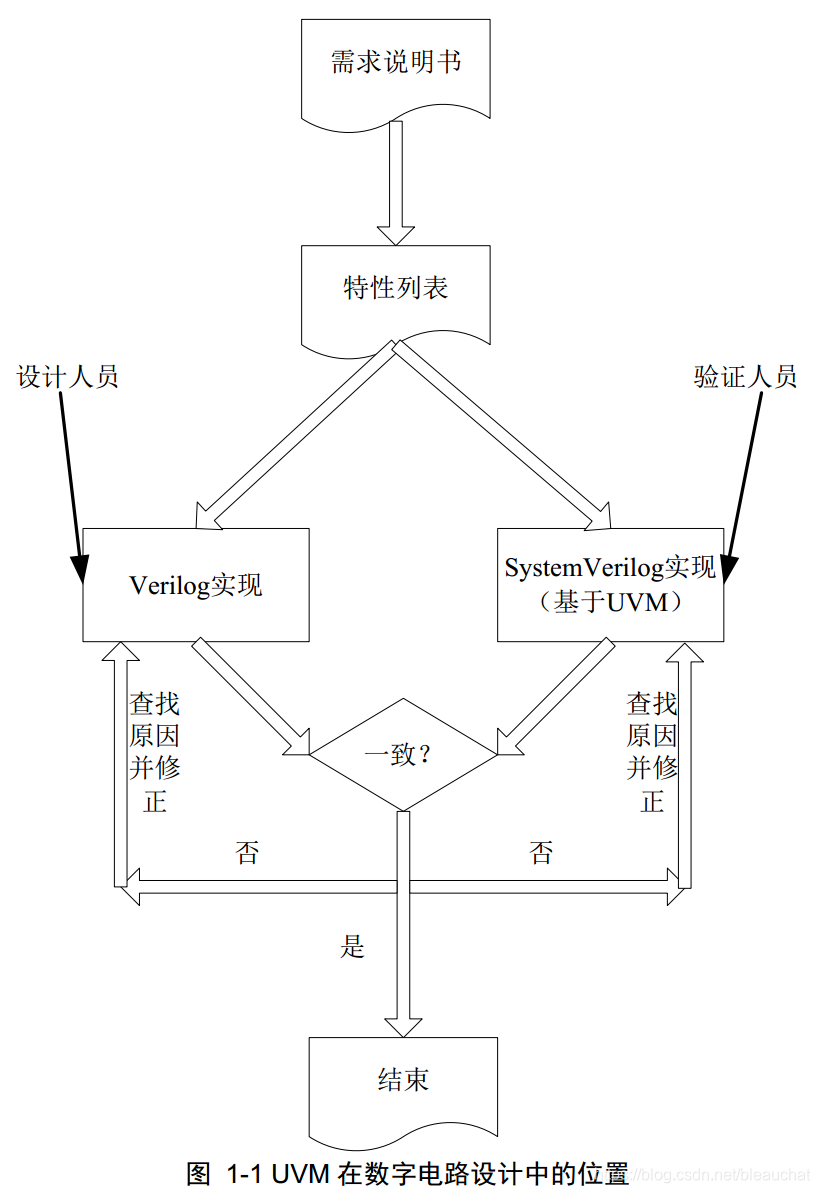

UVM 主要用于验证数字逻辑电路的正确性。何谓验证?在数字电路的设计流程中,最开始的时候会定义需求,把需求细化成为特性列表(feature list),之后设计人员利用 verilog 或者 systemverilog 把特性列表翻译成为 RTL 代码。在翻译的过程中,由于各种各样的原因,如设计人员自身对于 feature list 的理解不清,设计人员不小心遗漏了某种情况,这样翻译后的 RTL 代码就不能完全的反映 feature list。验证的含义就是把 feature list 和 RTL 代码比对,看看 RTL 是否能实现 feature list 的功能。被测试的 RTL 代码通常称为 DUT(Design Under Test)或者 DUV(Design UnderVerification);

1.1.2 验证在现代IC流程中的位置

现代IC前端的设计流程如图所示:

在上面的这幅图中,设计人员使用的是 verilog,其实这里也完全可以使用systemverilog 实现。就如我们可以使用 c++来写 c 代码,并可以完全的用 c++的编译器来编译 c 的代码一样, systemverilog 也完全包含了 verilog,换言之, verilog 只是

systemverilog 的一个子集;

通常的IC设计从一份需求说明书开始,IC工程师会把它细化为特性列表;设计工程师根据特性列表,将其转化为设计规格说明书,在这份说明书中设计工程师会详细阐述自己的方案, 描述清楚接口时序信号、使用多少RAM资源、如何进行异步处理等;验证工程师根据特性列表,写出验证规格说明书,将会说明如何搭建验证平台、如何保证验证完备性、如何测试每一条特性、如何测试异常等;

当设计说明书完成后,设计人员开始用verilog将特性列表转换为RTL代码;验证人员则开始使用验证语言,搭建第一个测试用例(test case);当RTL代码完成后,验证人员开始验证这些代码(DUT design under test)的正确性;

1.1.2 验证的语言

验证是服务于设计的,现在通常有两种设计语言:verilog和 VHDL;verilog由于其通用性在IC设计领域占据了主导地位,基于verilog的验证语言主要有:

(1)verilog: verilog是针对设计的语言, verilog在验证方面的最大不足是功能模块化、随机化验证上的不足,这导致更多的是直接测试用例(激励是固定的,其行为也是固定的),而不是随机测试用例(激励在一定范围内是随机的);

(2)systemC:其本质上是一个C++库,在C++中用户需要自己管理内存,指针会把人搞得头大;

(3)system verilog:它是一个verilog的扩展集,可以完全兼容verilog;其具有所有面向对象语言的特性:封装、继承和多态;同时还为验证提供了一些独有的特性,如约束、功能覆盖率;

1.1.3 何谓方法学

有了system verilog后是不是足以搭建一个验证平台了呢?答案是肯定的,只是很难;就像汉语是优秀的语言一样,自古以来无数的名人基于它创造了很多优秀的篇章,在这些篇章的基础上,作家通常引用几句就会使自己的文章出彩,这些优秀的篇章就是汉语言的库;同样system verilog作为一门优秀的语言,但如果仅仅使用它来进行验证是远远不够的,有很多直接的问题需要考虑,如:验证平台有哪些基本组件,各个组件之间如何进行连接和通信,每个组件的行为有哪些等等....从UVM的角度讲,方法学只是一个库!!

UVM 是建立在 systemverilog 平台上的一个库,它提供了一系列的接口,让我们能够更方便的进行验证。什么是库? 我们大家都学习过 C 语言,其中的 stdlib.h,stdio.h, math.h 等就是 C 语言的库。库之最其本的目的就是方便人们的使用。像一个 sin 函数,如果没有 math.h,让自己来写,那要怎么写呢?使用泰勒展开吗?那要展开多少级呢?库则把这些基本的、同时又经常使用的细节给隐藏了,让我们更加方便的编写验证平台;

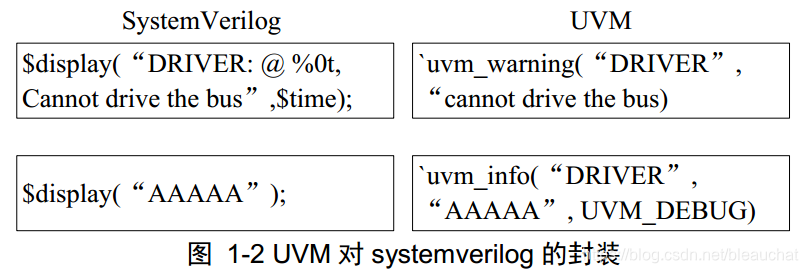

如下面的第一例子所示,我们期望在信息打印时同步输出时间,在 systemverilog中只能在 display 语句中调用 time 函数。但是在 uvm 中,只要使用 uvm_warning 或者 uvm_error 或者 uvm_info 宏等, UVM 会自动帮你添加时间。在第二个例子中,经

常会在出错的时候要打印一些字符,当后来问题解决的时候,我们不希望这些语句出现,于是就只能把 display 语句手工删除。但是在 UVM 中,通过设置 uvm_info 宏的 verbosity 特性,可以设置在正常运行的时候不打印这些信息,而只在调试的时候才打印,从而根本不必删除这些语句;

1.2 学了UVM之后能干什么?

1.2.1 验证工程师

1.2.2 设计工程师

在IC设计领域,验证与设计不分家;

UVM验证方法学精要

UVM验证方法学精要

UVM(通用验证方法学)是基于SystemVerilog的一种验证标准,由行业巨头联合推出,用于数字逻辑电路的验证。本文介绍了UVM的起源、在IC设计流程中的角色、与SystemVerilog的关系及验证语言的比较,强调了方法学的重要性。

UVM(通用验证方法学)是基于SystemVerilog的一种验证标准,由行业巨头联合推出,用于数字逻辑电路的验证。本文介绍了UVM的起源、在IC设计流程中的角色、与SystemVerilog的关系及验证语言的比较,强调了方法学的重要性。

4960

4960