滤波处理时产生的位宽增加是基于滤波的乘累加运算造成的;位宽增加的上限是非零乘法运算系数以2位底的对数向上取整再加上原始系数位宽,如下公式;

但是实际当中系数较小,不会达到最大位宽;

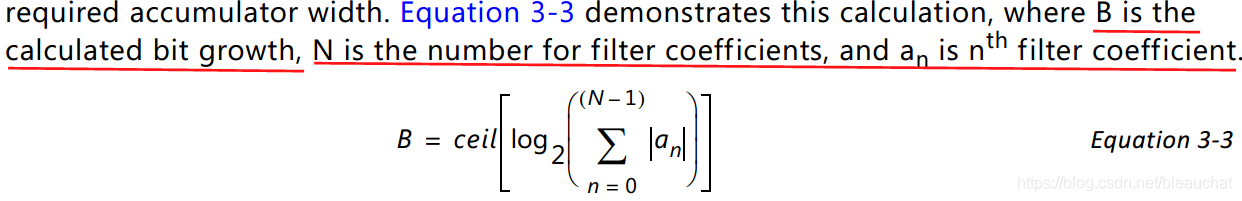

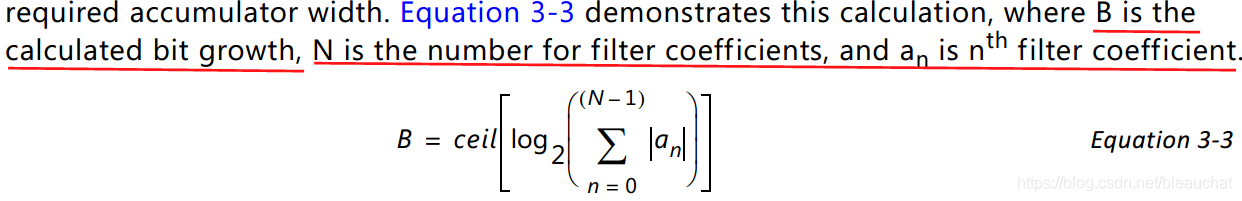

实际增长的位宽如上是式3-3所示;

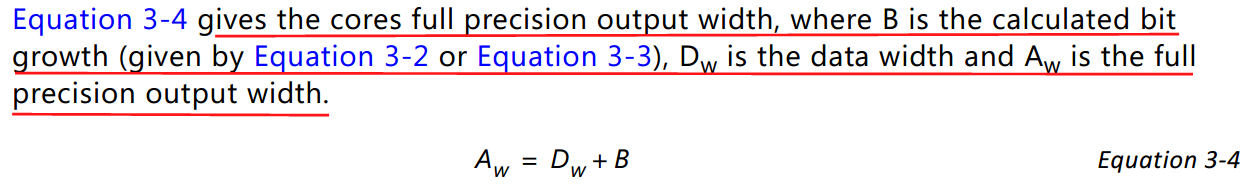

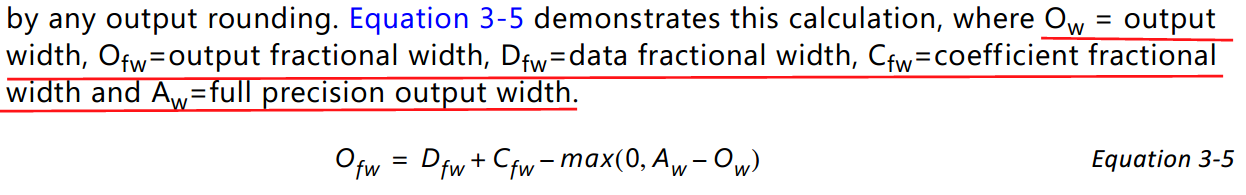

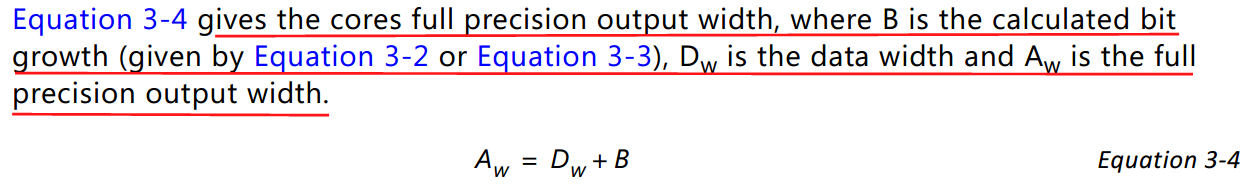

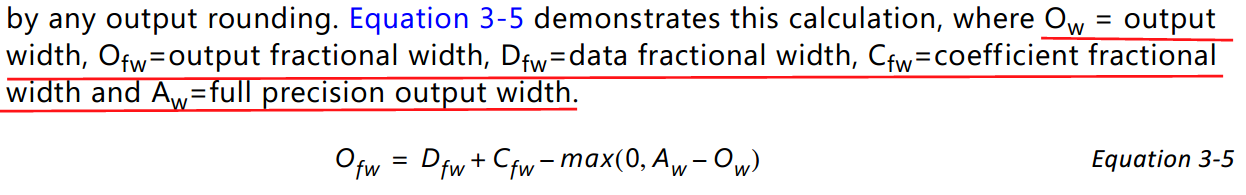

3-4给出了输出的全精度位宽;上面的式子是在没有考虑小数位的情况下计算得到的最终位宽,下面给出考虑小数位的情况:

本文深入探讨了滤波处理过程中位宽增加的原因,详细解析了位宽增加的上限计算公式,并提供了考虑小数位情况下的输出全精度位宽计算方法。

本文深入探讨了滤波处理过程中位宽增加的原因,详细解析了位宽增加的上限计算公式,并提供了考虑小数位情况下的输出全精度位宽计算方法。

滤波处理时产生的位宽增加是基于滤波的乘累加运算造成的;位宽增加的上限是非零乘法运算系数以2位底的对数向上取整再加上原始系数位宽,如下公式;

但是实际当中系数较小,不会达到最大位宽;

实际增长的位宽如上是式3-3所示;

3-4给出了输出的全精度位宽;上面的式子是在没有考虑小数位的情况下计算得到的最终位宽,下面给出考虑小数位的情况:

2万+

2万+

1874

1874

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?