用于超宽带应用的超低功耗LNA设计技术

摘要

本文提出了一种改进低噪声放大器(LNA)性能的设计技术。该技术基于MOSFET器件在射频(RF)应用中的一个新的工作参数(OP)。该技术用于优化超宽带(UWB)应用中低噪声放大器(LNA)的参数。所提出的方法可预测最佳偏置点,以最大化LNA性能。仿真结果表明,与传统方法相比,所提出的方法可将品质因数(FoM)提高70%,同时对噪声系数(NF)和线性特性无显著影响。

索引词 —低噪声放大器(LNA),超宽带(UWB),超低功耗(ULP),品质因数(FoM)

I. 引言

由于持续的技术进步,MOS晶体管的射频性能已得到改善。在器件领域,短沟道MOSFET在先进的深亚微米技术[1]中具有远高于100 GHz的截止频率(fT)等高频参数。尽管这些参数在射频工作下表现出广阔的MOSFET设计空间[2],但它们通常不能保证最佳的射频电路性能。

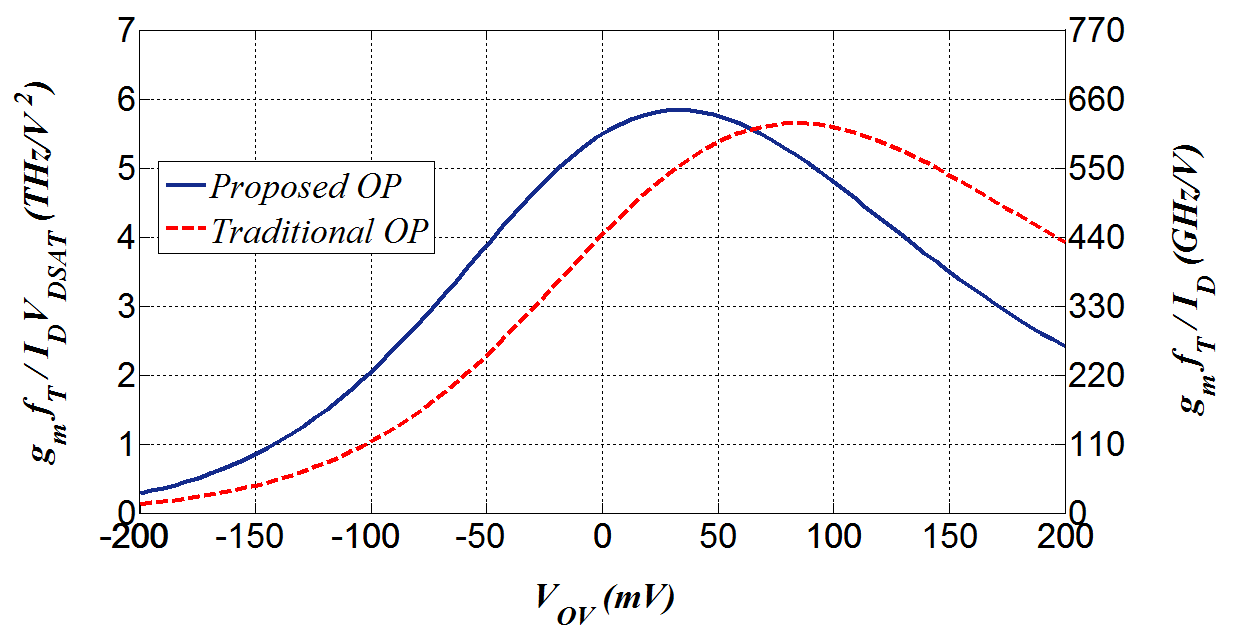

在低噪声放大器(LNA)的设计中,一个用于确定最佳偏置的简单方程在初始设计阶段非常有帮助。在[1],[2] gmfT/ID中,已提出将其作为射频MOSFET器件的品质因数(FoMRF)。但是,尚未详细探讨使用gmfT/ID作为品质因数FoMRF的基本物理原因。在[3]中,考虑了漏源饱和电压(VDSsat)对功耗的影响。对于模拟放大器的增益性能,gm²/ID被视作一种品质因数,因为它表示单位直流功耗下的功率增益[4]。然而,对于宽带应用,品质因数可能比gm²/ID更复杂,因为除了增益、噪声性能和功耗外,还应考虑带宽。最近,(gm/ID)·(gm/gds)·fT 被提出作为偏置指标或OP,通过将本征增益(gm/gds)引入OP[5],[6]中。然而,OP可以比之前所有建议提供更多信息。

在本文中,我们将证明可作为低噪声放大器设计中MOSFET器件的OP。该方法被发现与电路级品质因数非常接近。针对低噪声放大器的各项性能,在初始设计阶段,一个用于确定栅极和漏极偏置最优值的简单方程非常有帮助。共栅极(CG)低噪声放大器因其宽频简单匹配电路、高线性度、低功耗以及相比共源极低噪声放大器更优的反向隔离特性,被广泛应用于超宽带应用中[7]。因此,将采用超宽带共栅极低噪声放大器作为设计示例,以验证我们所提出方法的有效性和能力。

II. 设计挑战

在无线传感器网络和便携式设备等许多应用中,降低功耗是可取的。可通过将MOSFET器件偏置在中等或弱反型区来降低功耗[8]。假设晶体管工作在饱和区边缘,沟道长度调制可以忽略不计[2],漏源电流因此由公式(1)表示:

其中,Cox是单位面积栅氧化层电容,UT是热电压,n是亚阈值斜率因子,亚阈值斜率(S)为= 2.3 n UT,μ是载流子迁移率,VGS是栅源电压,VT是阈值电压。该方程的主要问题在于未考虑VDS的影响。因此,我们将采用gm/ID查表法[9]。

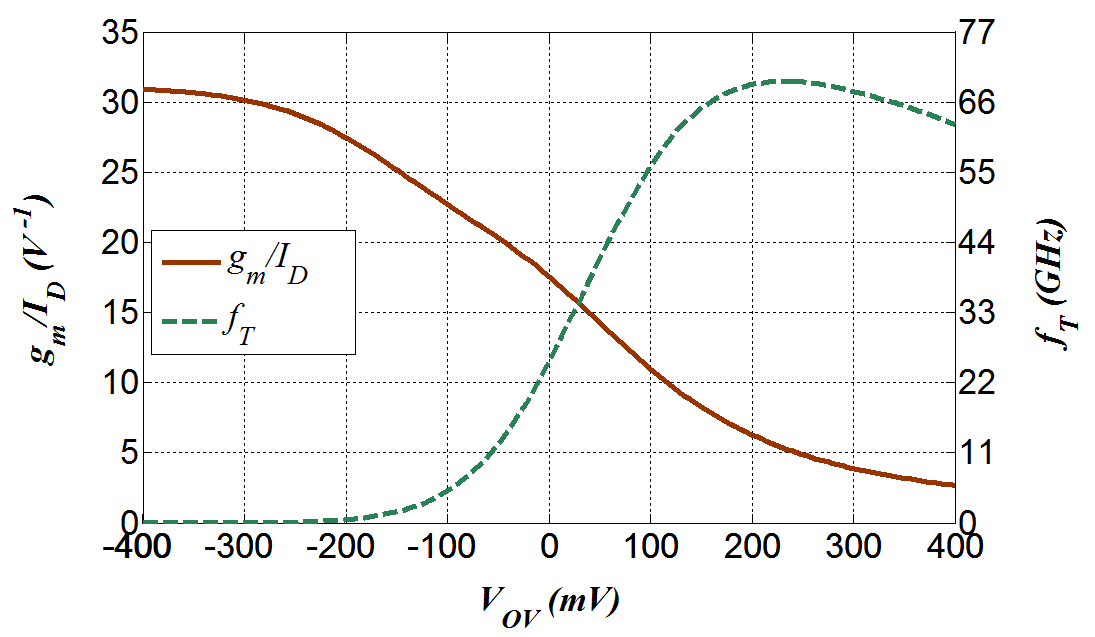

针对超低功耗应用的低噪声放大器设计方法之一是通过降低ID实现的。这可以通过减小过驱动电压(VOV= VGS ‐ VT)来提高gm/ID[3]实现。然而,如图1所示,VOV的减小会导致fT下降。因此,噪声系数()将增大,带宽将减小。因此,确定晶体管的工作点是低噪声放大器设计中的主要挑战。相应地,我们需要了解影响fT的各种参数: fT的通用表达式可写为[1]:

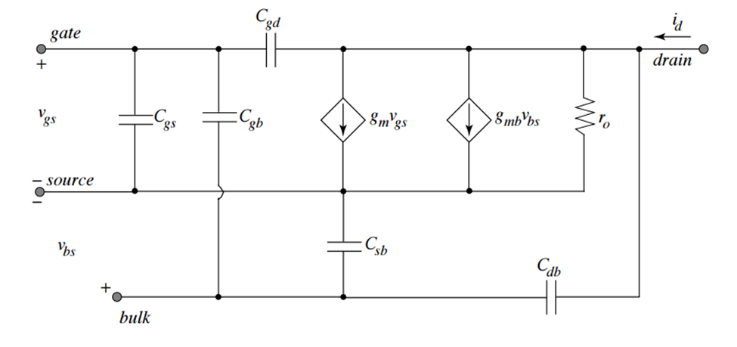

其中Cgg 定义为连接到栅极的Cgg=(Cgs+Cgb +Cgd),如图2所示。

III. 设计方法

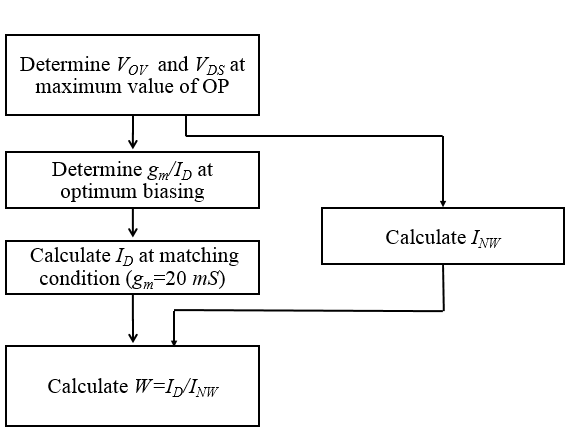

设计方法基于一维工作点来确定VOV[3],或更准确地使用二维工作点确定VOV和VDS 。接着,我们从图1中确定gm/ID 。然后,在每种情况下根据匹配条件的阻抗(gm=20毫西门子)计算ID的值。最后,根据gm/ID方法论[9],通过将ID除以单位宽度电流(IN W )来计算W。

1. 一维工作点 [3]

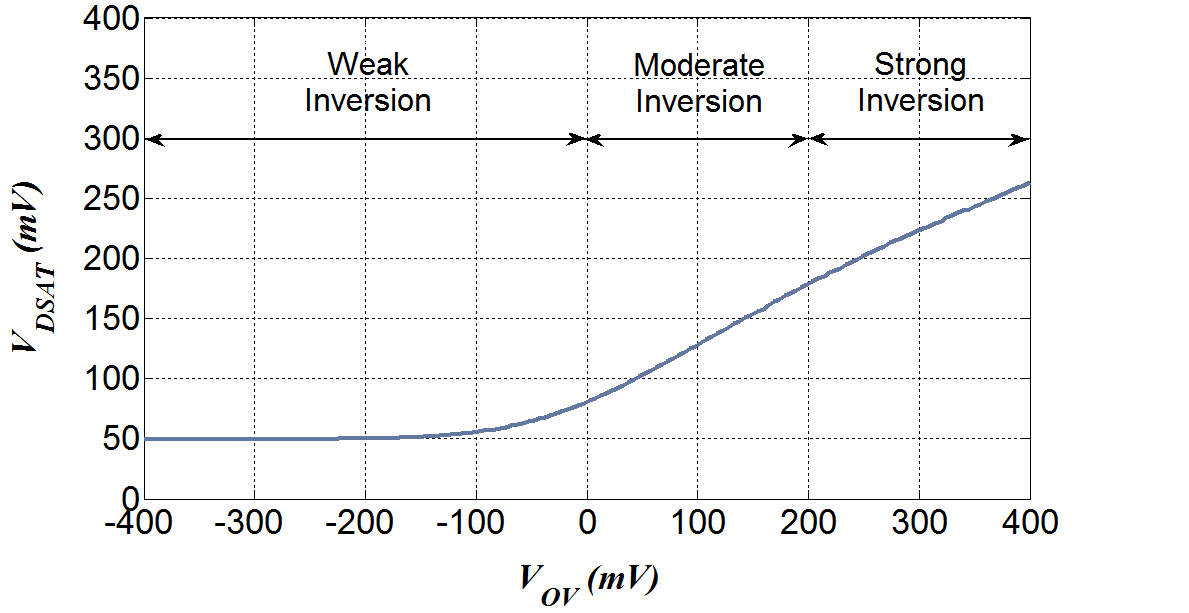

在MOS晶体管中,为了使晶体管工作在饱和区,VDS应大于VDSsat 。此外,在强反型和中等反型下,VDSsat与VOV成正比,而在弱反型时,VDSsat几乎保持不变,如图4所示。因此,降低VDSsat可使MOS晶体管在更小的VOV下工作。这导致工作在更高的gm/ID ,并降低ID。此外,这还允许在低VDS和低压电源(VDD)下工作,从而降低功耗。

因此,VDSsat被提议作为所提出的1D OP中的关键设计参数,如下所示:

1D OP = gmfT / ID × VDSsat (3)

一维工作点在较小的VOV (接近VT)处达到最大值,如图5所示。当使用传统操作点和一维工作点 [3]时,得到两个峰值。这些峰值仅用于确定VOV (一维)。

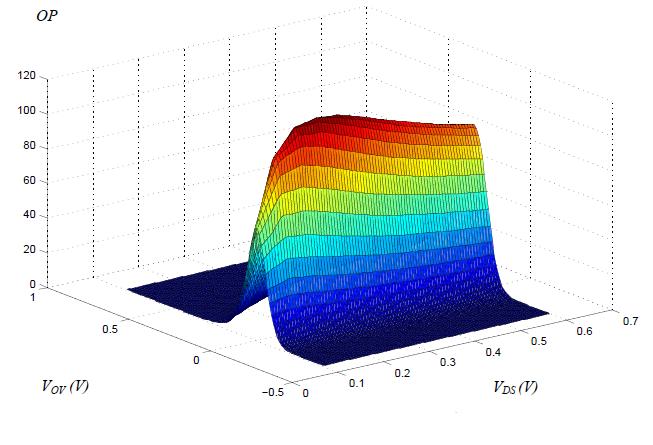

2. 二维工作点

电路的性能取决于VOV和VDS (二维)的选择。然后,我们可以确定各个MOS器件的W/L和ID 。尽管如前一节所述,VOV 是主要决定因素,但VDS 也会对功耗产生显著影响。

超宽带低噪声放大器具有四个重要特性:增益(G)、带宽(BW)、噪声系数(F)和功耗(PD)。低噪声放大器的整体性能可以用许多文献中定义的品质因数(FoM)来表示,如下所示:[10],[11]

我们可以利用MOSFET小信号等效电路(图2)为上述每个因素推导出解析表达式。功率增益定义为:

当MOSFET的输入电阻(Rin)等于信号源或天线的电阻(Rsig=50 Ω )时,满足匹配条件。噪声系数推导如[2]所示:

其中是MOSFET沟道热噪声的功率谱密度,在饱和区几乎与ID成正比。因此,我们可以写出以下方程:

低噪声放大器中的功耗简单表示为 PD = ID × VDD。最后,带宽与 fT 成正比,因此我们可以写出:

该表达式被用于以获得如图所示的MOSFET的最佳偏置(VOV和VDS)6.

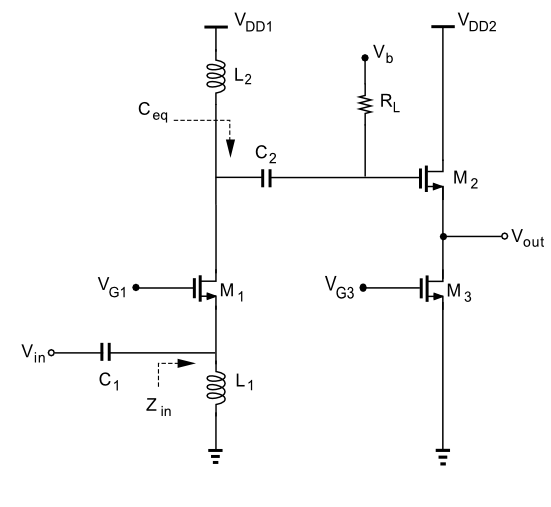

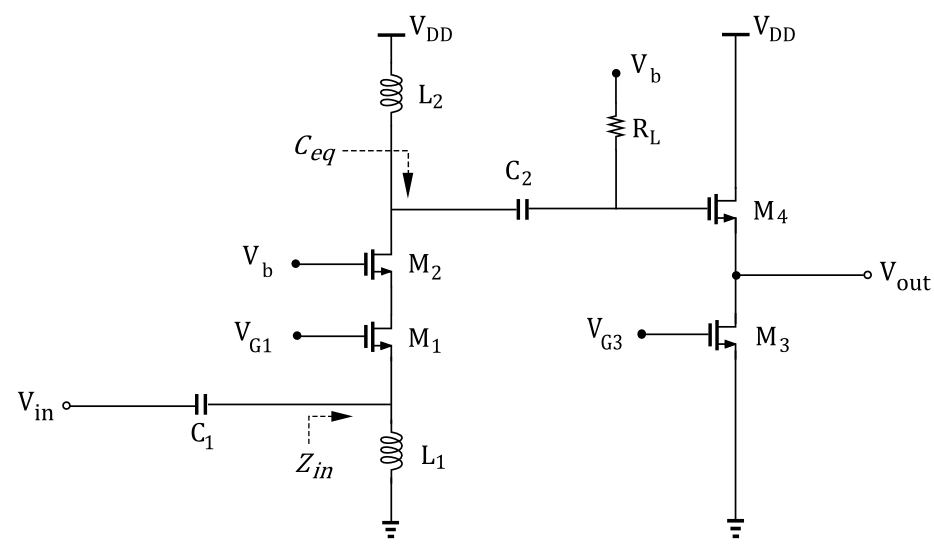

IV. 电路架构

低噪声放大器电路如图7.a所示。该电路采用130纳米UMC CMOS技术设计并进行仿真,使用单级共栅极结构(M1)。输入电容(C1)用于补偿晶体管输入阻抗(Zin)的虚部,其表达式为:

其中,Cgs1是M1的栅源电容,Cpar1是电感(L1)的寄生电容。在VDD1= 0.25V下,C2用于隔离偏置在VDD2= 0.5 V和Vb=0.8 V的输出缓冲器(M2和M3)。该缓冲器通过负载电阻RL进行偏置。RL的值决定低噪声放大器增益,并根据公式(11)和(12):

Amax ≈ gm × RL (11)

其中Amax是低噪声放大器核心的最大电压增益,

其中,Cgd1是M1漏极处的等效电容,Cpar2是负载电感(L2)的寄生电容。

表1显示了图7.a的偏置参数和电路元件值。在最小晶体管长度(Lmin=0.12 μm)下计算M1参数,以获得最大fT。我们从二维工作点得到最优的 VOV和VDS。可以忽略电感(L1和L2)的寄生电阻的影响,并认为VDD1与VDS取值相同。然后使用Gm/ID设计方法(图3)来确定最佳偏置参数。电路元件代表无源元件的值以及输出缓冲晶体管(M2和M3)的尺寸。

表1:M1偏置参数和电路元件

| 参数 | 值 | 组件 | 值 |

|---|---|---|---|

| M1 Bias Parameters | Circuit Components | ||

| VOV | 50 mV | C1 | 2 pF |

| VDS | 250 mV | L1 | 4 nH |

| VDSsat | 103 mV | C2 | 1 pF |

| (gm/ID) | 14.5 | L2 | 11.25 nH |

| ID | 1.38 mA | RL | 2 kΩ |

| IN W | 0.0167 mA/μm | M2 (W/L)₂ | 40 / 0.12 |

| W | 82 μm | M3 (W/L)₃ | 80 / 0.12 |

V. 结果与讨论

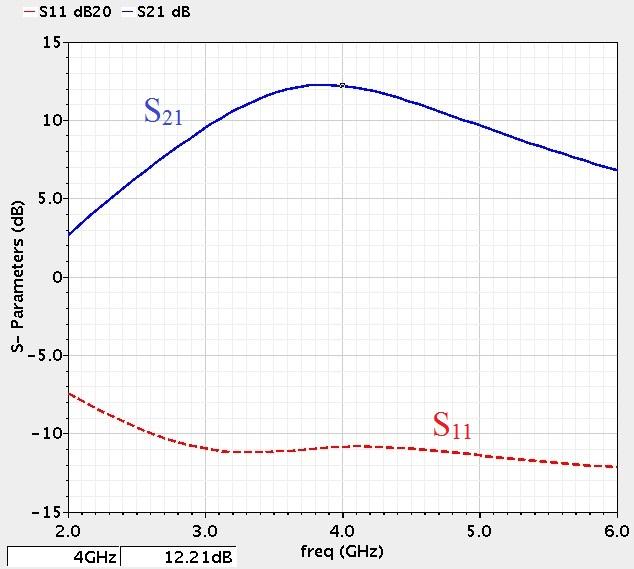

在3–5 GHz频段内,所设计低噪声放大器的S参数和噪声系数随频率变化的仿真结果如图8所示。结果表明,在采用二维工作点的设计情况下,该低噪声放大器功耗为0.35 mW,并实现了最大功率增益(S21)为12.2 dB。输入回波损耗(S11)小于–10 dB,最小噪声系数为1.9 dB。表2显示了所提出方法的结果与以往出版物的比较。

无法在同一电路架构上同时应用2D OP和1D OP的结果[3],原因有两个。首先,在传统1D OP的高VOV (84 mV)下,我们无法设计单级CG(图7.a),因为这将导致Zin不稳定,且无法达到S11 > –10 dB,但在2D OP的较低VOV (50 mV)下是可行的。其次,如果我们将其与共源共栅共栅极结构一起使用,将会失去2D OP的全部优势(图7.b)。因此,我们可以将使用单级共栅极为二维工作点技术的两大主要优势之一,此外还包括确定最佳VDS。

VI. 结论

一个简单的品质因数(FoM)可用于超宽带低噪声放大器(UWB LNA)设计优化。第一个二维工作点(2D OP)从一个小信号等效电路中解析推导得出,并通过电路仿真进行了验证。该方法成功预测了最优的栅源和漏源偏置电压,显著改善了低噪声放大器的整体性能。所提出设计的品质因数(FoM)在宽带低噪声放大器领域中是最高的。

表2:低噪声放大器性能比较

| 参数 | This 文献* | [3]* 2017 | [3]* 2017 | [5] 2016 | [6] 2015 | [7] 2011 | [11]* 2017 | [12] 2012 |

|---|---|---|---|---|---|---|---|---|

| S11 (dB) | < –10 | < –18 | < –16 | < –10 | < –10 | < –10.3 | < –7.5 | < –8 |

| BW (GHz) | 3 – 5 | 3 – 5 | 3 – 5 | 0.6 – 4.2 | 0.1 – 7 | 2.6 – 10.5 | 3.2 – 10.64 | 3.1 – 4.8 |

| 增益max S21 (dB) | 12.2 | 10.6 | 10.2 | 14 | 12.6 | 9.4 | 17 | 13 |

| 噪声系数 (dB) | 1.9 – 2.1 | 2.24 – 3.12 | 2.19 – 3.04 | 4 – 6 | 5.5 – 6.5 | 5.5 – 6.5 | 2.5 – 5.7 | 3.5 – 4.5 |

| 输入三阶交调截点(dBm) | - | 16 | –16.9 | –16.6 | -10 | - | 9 | NA |

| PD (mW) | 0.35 | 0.45 | 0.58 | 0.25 | 0.75 | 0.99 | 16.5 | 3.4 |

| FoMLNA | 34 | 14.9 | 11.4 | 20.4 | 11 | 6.65 | 1.8 | 1.46 |

| 使用的OP | 2D OP | 1D OP | 1D OP | Gm吹嘘 | Gm吹嘘 | CG | 共源共栅 | CS Gm吹嘘 |

| 电路架构 | CG | 共源共栅 | CG | 共源共栅 | CG | 共源共栅 | CG | 共源共栅 |

| CMOS工艺 | 130 nm | 130 nm | 130 nm | 130 nm | 90 nm | 180 nm | 180 nm | 130 nm |

*仿真结果

549

549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?