文章目录

第一篇

去耦电容的作用

电源噪声抑制

去耦电容的主要功能之一是抑制电源噪声。当集成电路(IC)快速开关时,会从电源中瞬间抽取大电流,从而引发被称为 “噪声” 的电压波动。这种噪声会在整个电路中传播,不仅会导致信号完整性问题,还可能造成电路故障。将去耦电容靠近集成电路的电源引脚放置时,电容会充当 “本地能量储备库”,为高频噪声提供一条低阻抗通路,使其被分流到地。这一过程有助于维持稳定的电源电压,同时将噪声对电路的影响降至最低。

高频滤波

除抑制电源噪声外,去耦电容还兼具高频滤波功能。它们能有效 “旁路”(即分流)高频噪声成分,防止这些噪声进入电路中的敏感部分。通过为高频信号构建一条通往地的低阻抗通路,去耦电容有助于保持信号完整性,避免产生不必要的干扰。

瞬态响应改善

去耦电容在改善电源瞬态响应方面也发挥着关键作用。当集成电路对电流的需求突然增加时,电源可能无法瞬时响应,进而导致暂时性的电压下降。此时,去耦电容作为本地能量储备库,会在这些瞬态过程中提供所需电流,帮助维持稳定的电压水平。这一点对于存在快速开关操作的高速数字电路而言,尤为重要。

影响去耦电容选型的因素

工作频率

工作频率是确定去耦电容容值的关键因素。不同容值的电容在不同频率范围内效果不同。通常情况下,容值较小的电容在高频下效果更显著,而容值较大的电容则更适合低频场景。重要的是,要先分析电路中存在的噪声的频率谱,再选择能有效针对这些频率的电容容值。

电容的频率响应

电容具有与频率相关的阻抗特性。在低频时,电容的阻抗较高;而在高频时,其阻抗会降低。这种特性可以用容抗公式来描述:

Xc = 1 / (2πfC)

其中:

Xc 表示容抗,单位为欧姆(Ω)

f 表示频率,单位为赫兹(Hz)

C 表示电容,单位为法拉(F)

随着频率的升高,容抗会降低,这使得电容能够为高频噪声提供一条低阻抗通路。

基于频率选择电容容值

基于频率选择去耦电容容值时,通常会组合使用不同容值的电容,以覆盖较宽的频率范围。一种典型的做法是:使用大容量电容(例如 10 微法至 100 微法)来处理低频噪声并提供大容量能量存储,同时搭配小容量陶瓷电容(例如 0.1 微法至 1 微法)来针对性抑制高频噪声。

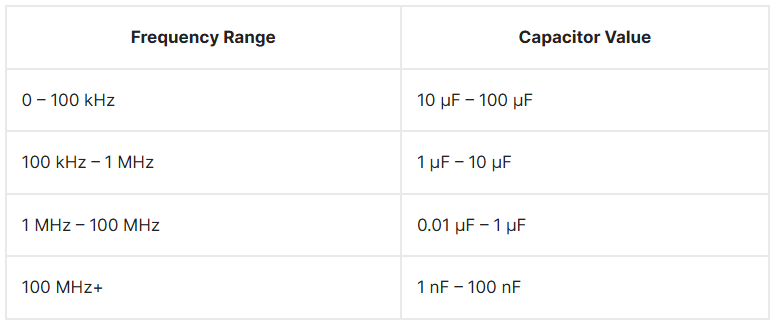

以下是一个基于频率选择电容容值的示例:

重要说明与去耦电容选型相关因素

需重点注意的是,以下数值均为通用参考标准,具体数值可能会根据电路的实际需求有所不同。

电源电压与电流

电路的电源电压和电流需求也会影响去耦电容的数值选型。通常而言,电压和电流需求越高,就需要越大容量的电容,以确保充足的能量存储,并最大限度减小电压波动。

电压额定值

选择去耦电容时,务必考虑电容的电压额定值。电容的电压额定值应高于电路中预期的最大电压(包括所有瞬态尖峰电压)。一个实用的经验法则是:所选电容的电压额定值至少应比标称电源电压高 50%。例如,若电路工作电压为 5 伏(V),则应选择电压额定值至少为 7.5 伏(V)的电容,以预留安全裕量。

电流额定值

去耦电容的电流额定值是另一项重要考量因素。电容应能承受预期的纹波电流,且不会出现过热或长期性能衰减的情况。纹波电流指的是流经电容的电流中的交流分量,其大小受开关频率、负载电流等因素影响。电容制造商通常会提供产品的纹波电流额定值,因此必须选择能够承受电路中预期纹波电流的电容。

印制电路板(PCB)布局与放置

去耦电容在印制电路板(PCB)上的放置位置和布局,对其性能发挥起着关键作用。合理的放置方式有助于减小电容与被去耦集成电路(IC)之间的阻抗,从而确保最佳性能。

放置准则

在 PCB 上放置去耦电容时,应遵循以下准则:

将电容尽可能靠近被去耦 IC 的电源引脚。这能最大限度减小电容与 IC 之间的电感和阻抗,实现有效的噪声抑制。

使用短而宽的走线将电容连接到电源层和接地层。此举可降低走线电感,并为高频噪声提供低阻抗通路。

若使用多种容量的电容,应将容量较小的电容放置在更靠近 IC 的位置,容量较大的电容则放置在稍远的位置。小容量电容主要针对高频噪声,而大容量电容则用于提供大容量能量存储,并处理低频噪声。

避免将去耦电容放置在过于靠近高速信号走线的位置,以最大限度降低串扰和干扰风险。

电源层与接地层

在多层 PCB 中,建议使用专用的电源层和接地层,以实现高效的电源分配并减小阻抗。电源层和接地层应放置在相邻的层上,中间用薄介电材料隔开。这种结构能为噪声电流提供低阻抗、高频的旁路通路,从而提升去耦电容的性能。

电容类型与材质

去耦电容的类型和材质也会影响其性能,以及在特定应用场景中的适用性。

陶瓷电容

陶瓷电容(尤其是多层陶瓷电容,MLCC)因其优异的高频性能、低等效串联电阻(ESR)和小巧的封装尺寸,被广泛用于去耦场景。它们拥有丰富的容量和电压额定值选择,适用于大多数去耦应用。

但需注意,陶瓷电容可能会出现 “直流偏置效应”—— 即随着施加的直流电压升高,电容容量会下降。在选择陶瓷电容(尤其是用于高压应用场景时),必须考虑这一效应。

钽电容与电解电容

与陶瓷电容相比,钽电容和电解电容能以更紧凑的封装提供更大的容量,常用于大容量能量存储和低频去耦场景。然而,它们的等效串联电阻(ESR)更高,高频性能也逊色于陶瓷电容。

钽电容以稳定性和可靠性著称,适合对长期性能有要求的应用。另一方面,电解电容虽能提供最大的容量,但高频性能有限,且等效串联电阻(ESR)较高。

(说明:1. 专业术语如 “DC bias effect(直流偏置效应)”“multilayer ceramic capacitors (MLCCs)(多层陶瓷电容)” 等均采用电子工程领域通用译法;2. 单位符号 “V(伏)” 保留原文,符合技术文档表述规范;3. “tantalum capacitors(钽电容)”“electrolytic capacitors(电解电容)” 为电容类型标准译名,确保行业术语一致性。)

去耦电容最优容量确定流程

既然我们已探讨了影响去耦电容选型的各类因素,接下来将介绍如何为电路确定最优电容容量。

所需电容容量的计算

要确定所需的去耦电容容量,需考虑以下参数:

电源电压(V,单位:伏)

预期最大负载电流(I,单位:安)

允许的电压纹波(ΔV,单位:伏)

开关频率(f,单位:赫兹)

所需的去耦电容容量可通过以下公式计算:C = I / (2πfΔV)

其中:

C 为所需电容容量,单位为法拉(F)

I 为预期最大负载电流,单位为安培(A)

f 为开关频率,单位为赫兹(Hz)

ΔV 为允许的电压纹波,单位为伏特(V)

示例计算

假设某电路的电源电压为 5 伏(V),最大负载电流为 1 安培(A),允许电压纹波为 100 毫伏(即 0.1 伏,V),开关频率为 100 兆赫兹(MHz)。将这些数值代入公式可得:

C = 1 A / (2π × 100 MHz × 0.1 V) ≈ 159 纳法(nF)

在此情况下,应选择容量接近 159 纳法(nF)的去耦电容,例如 150 纳法(nF)或 180 纳法(nF),具体可根据市面上可获取的标准电容容量选择。

选择合适的电容封装

确定所需电容容量后,下一步是选择合适的电容封装。封装尺寸与类型取决于以下因素:印制电路板(PCB)的可用空间、所需的电压与电流额定值,以及期望的高频性能。

常见的去耦电容封装

0201、0402、0603、0805:这类表面贴装(SMD)封装体积小巧,适用于高密度 PCB 布局与高频去耦场景。

1206、1210:这类表面贴装封装体积更大,可提供更高的电容容量与更强的电流承载能力。

径向与轴向通孔封装:这类通孔封装常用于需要大电容容量与高压应用的场景。

选择电容封装时,需考虑 PCB 的空间限制,在满足电气规格要求的前提下,选择能适配可用空间的封装类型。

电容的并联组合

在某些情况下,单一容量的电容可能无法在整个关注的频率范围内提供最优去耦性能。此时,可将不同容量的电容并联组合,以实现更宽的频率覆盖范围。

例如,可将一个大容量储能电容(如 10 微法,μF)与一个小容量陶瓷电容(如 0.1 微法,μF)并联,结合两者在低频与高频去耦中的优势:大容量电容负责提供储能并抑制低频噪声,小容量电容则针对高频噪声,并改善瞬态响应。

采用电容并联组合时,需确保这些电容在 PCB 上紧密排布,以最大限度减小电容之间的阻抗。

(说明:1. 公式中 “2π” 为数学常数,保留符号表述;2. 封装型号 “0201、0402” 等为行业通用规格代码,保留原文;3. 单位符号 “F(法拉)、A(安培)、Hz(赫兹)、V(伏)、nF(纳法)、μF(微法)” 均为国际标准符号,符合技术文档表述习惯。)

第二篇 印制电路板(PCB)设计中去耦电容的选型问题

FROM ALITUM DESIGNER

在各类 PCB 设计规范(包括高速数字设计 “权威指南”)中反复出现的一个要点,是如何选择合适的去耦电容容量。有时人们在讨论这一问题时,并未完全理解这些电容在电源分配网络(PDN)中应发挥的作用,以及它们在保障电源完整性(Power Integrity)方面的职责。我还见过许多应用笔记默认沿用数十年前的旧规 —— 在数字集成电路的电源引脚与接地引脚之间放置三个去耦电容(通常是 1nF、10nF 和 100nF,或类似组合)。在过去,这种做法或许可行:早期高速数字器件产生的电源完整性问题尚不严重,不足以干扰核心电压,因此三个电容的组合基本能满足需求。

然而如今,具有多输出、低核心电压(最低可达 1.0V)的高速集成电路,其噪声约束比以往低速器件严格得多。更严格的噪声约束意味着需要更精确的去耦设计。鉴于此,任何设计人员在使用当今性能适中的微控制器(MCU)及其他各类数字器件时,都必须掌握去耦电容的正确选型方法。那么,最佳选型方式是什么?总体而言,主要有两种方法。下文将详细介绍这两种方法,说明如何计算去耦电容的容量,并解释为何 “三个去耦电容” 的旧说法在现代高速数字设计中已不再适用。

关键术语补充说明

PDN(Power Distribution Network):电源分配网络,指 PCB 上从电源模块到各器件电源引脚的完整供电路径,包括导线、过孔、焊盘、电容等,其设计直接影响电源完整性。

Power Integrity(电源完整性):确保电源网络向器件提供稳定、低噪声电压的能力,是高速数字设计中的核心指标之一,噪声过大会导致器件逻辑错误或性能下降。

Decoupling Capacitor(去耦电容):并联在器件电源与地之间的电容,主要作用是 “就近储能”,抑制电源线上的瞬时电压波动(如器件开关时的电流突变),为器件提供快速电流补充。

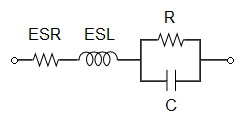

理解等效电容模型

在确定数字设计所需的去耦电容容量之前,你需要先理解电容的基本电路模型。尽管我们倾向于认为电容的工作状态完全符合理论描述,但实际情况并非如此。所有电容的引脚都存在一定的电感,这些电感决定了电容的阻抗特性。在实际建模中,电容通常被表示为一个串联 RLC(电阻 - 电感 - 电容)网络:

在该模型中,ESR(等效串联电阻)和 ESL(等效串联电感)分别代表等效串联电阻与等效串联电感。电容值 C 可采用元件数据手册中标注的电容参数。最后,电阻值 R 用于表征构成电容器的电介质的电导率,它对应着电容器充电后从电路中移除时产生的瞬态漏电流。通常情况下,该电阻值足够大,因此可忽略不计。

在该模型(忽略电阻 R)中,若假设电路两端连接的负载为 0 欧姆,则(ESR/(2×ESL))的值即为该等效电路的阻尼系数。这一数值代表电路在完全充放电状态下,对输入电压变化做出响应所需的最短时间。电容器的数据手册不会列出阻尼系数,而是会像下图所示的那样,仅提供阻抗谱图。若有需要,你可利用数据手册中的 ESL(等效串联电感)和 ESR(等效串联电阻)数值来计算阻尼系数。

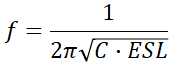

最后,所有实际电容器均具有自谐振频率,该频率与任意串联 RLC 电路的谐振频率计算公式相同,在本模型中具体表示为:

自谐振频率可在阻抗谱图中查看。下方展示的是一个实际 AVX 电容器的示例:

去耦电容的实际作用是什么?

这是一个非常好的问题,它能帮助我们理解为何需要去耦电容来确保数字集成电路(IC)的电源完整性。当所有电容连接到直流电压源时,都会在平衡状态下储存电荷:电容的极板会充电,并保持总量为 Q = CV(Q 为电荷量,C 为电容值,V 为电压)的电荷。若电压 V 出现波动或小幅下降,一部分电荷 Q 会释放出来并输送到负载,其作用类似于一个小型电池。

在数字电路中连接实际电容时,会出现一个问题:电压下降并非发生在单一频率下。电源电压随时间的波动,或是电路中突然出现的电流脉冲,在示波器上通常表现为具有陡峭边沿速率的尖峰信号。这意味着该信号相关的功率谱会分布在一定频率范围内,且会与电容的自谐振频率重叠。其结果是,电容会随之放电,并在电源总线上激发瞬态振荡。如果电源分配网络(PDN)通过总线上的数字电容 IC 获取这部分电能,电源总线上的瞬态信号就会以电源引脚处的振铃形式显现。不过,若能选择合适规格和数量的去耦电容,这种波动就能降至最低。这也是 “三个电容” 这一常规设计准则存在的原因:这种电容组合与规格选择虽非完美,却是保障电源稳定的可行方案。

去耦电容的规格确定方法

了解了实际电容的电气特性后,我们可从三个方向确定去耦电容的规格:

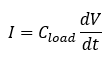

基于时域的负载充电分析:印制电路板(PCB)上的走线本质上具有电容特性,去耦电容的作用是为电容性 IC 提供给负载充电所需的电流。可通过负载电容值以及所需的转换时间 / 峰值电压,估算为走线 / 传输线充电所需的总电荷量与电容值。

基于目标纹波、电流脉冲与阻抗谱的分析:此方法需先设定电源总线振铃的限制条件,再据此确定所需的电容值,使电源分配网络(PDN)的阻抗谱低于目标阻抗。

基于时域的冲激响应分析:该方法需在电源分配网络(PDN)的模型中分析电容的瞬态响应。可利用电路原理图建立 PDN 的唯象模型(phenomenological model),并通过 SPICE 仿真进行瞬态分析;也可通过冲激响应计算得出 PDN 的传递函数与 Z 参数。通过迭代尝试不同的电容值,最终可使 PDN 的阻抗降至目标值以下。

在上述三种方法中,仅有第一种方法较为 “简便”,它能根据电容释放电荷所需的最短时间,为电容组所需储存的总电荷量提供基准估算值。若要为开关速度较快的数字电路设计去耦方案,应选择等效阻尼系数能使电路达到临界阻尼或轻微过阻尼状态的电容,以抑制放电过程中的振铃现象。只要电容的放电速率短于电路的开关时间,去耦电容就能快速补偿电压波动。

基于走线充电的去耦电容总容量估算

估算去耦电容总容量的最简单方法,需考虑三个因素:需输送给电容性 IC 的最大电荷量、电荷输送至 IC 的速度要求,以及需补偿的电压波动幅度。由于大多数负载呈电容性,可将到达负载的电流与信号电压从 “关” 到 “开”(或反之)的变化速率关联起来:

需注意,类似方法也可应用于纯电阻性或纯电感性负载。下面我们以该公式作为去耦电容计算工具,来分析一款具有多个开关输出端的数字集成电路(IC)所带的容性负载。

简单示例:一款含 12 个输出端的数字集成电路

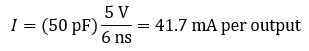

要说明如何将该公式应用于容性负载,最佳方式是结合实例。假设你有一款含 12 个输出端的数字电容集成电路,其每个输出信号的电压为 5 伏(V),上升时间为 6 纳秒(ns)。每个输出端驱动一个负载电容为 50 皮法(pF)的负载。若将信号的上升时间近似为线性变化,则上述公式中的导数可表示为电压变化量 dV = 5 伏(V),时间变化量 dt = 6 纳秒(ns)。因此,每个输出端所需的电流为:

(说明:文中涉及的电子工程术语如 “capacitive load(容性负载)”“rise time(上升时间)”“load capacitance(负载电容)” 等,均采用行业通用中文译法;单位符号 “V(伏)”“ns(纳秒)”“pF(皮法)” 为国际标准符号,保留原文以符合技术文档表达习惯。)

若 12 个输出端全部同时从高电平切换至低电平,那么从电源分配网络(PDN)涌入的总电流将达到 500 毫安(mA)。这种涌入电流会导致接地平面电位发生变化,进而使信号电位产生偏移,而电容需对这种信号电位偏移进行补偿。假设高电平(ON 状态)的阈值为 4.5 伏(V),那么为避免出现位错误,需要补偿的电压跌落幅度为 0.5 伏(V)。此外,这种补偿必须在 6 纳秒(ns)内完成。因此,最小去耦电容值为:

(说明:1. 技术术语 “inrush current” 译为 “涌入电流”,“ground plane potential” 译为 “接地平面电位”,“voltage dip” 译为 “电压跌落”,“bit errors” 译为 “位错误”,均符合电子工程领域通用表述;2. 单位符号 “mA(毫安)”“V(伏)”“ns(纳秒)” 为国际标准符号,保留原文以确保技术文档的准确性和规范性;3. “PDN” 为 “Power Distribution Network(电源分配网络)” 的缩写,首次出现时已完整译出,此处保留缩写以简化表述,符合技术文本习惯。)

去耦电容规格计算与电源分配网络(PDN)阻抗分析

在此情况下,你应使用至少 6 纳法(nF) 的电容,以在 6 纳秒(ns)内补偿最大 0.5 伏(V)的电压波动。需注意,部分设计指南会建议在此示例中采用两个 3 纳法(nF)的电容并联 —— 这种方式可使等效串联电阻(ESR)降低一半,但同时也会使等效串联电感(ESL)同样降低一半,因此对阻尼的整体影响为零。若电容的响应处于欠阻尼状态,你可选择容量更大的电容,这能使响应更接近临界阻尼或过阻尼状态。不过,采用两个电容并联的方式,有助于拉平电源分配网络(PDN)在电容谐振频率附近的阻抗谱。

基于冲激响应 / PDN 阻抗的去耦电容规格确定

上述模型存在哪些问题?核心在于它未考虑实际去耦电容或电路板中真实电源分配网络(PDN)的所有特性,包括:

如前文等效电容阻抗模型中所示的等效串联电感(ESL);

电源分配网络(PDN)中的寄生电容与寄生电感。

其中第二点尤为重要,且需要进行布局后仿真。电源分配网络(PDN)的阻抗谱不仅取决于通过去耦电容计算工具得出的数值,还取决于 PDN 的几何结构(即层叠排布、材料、总线尺寸等)。正因阻抗谱与几何结构密切相关,你需要将印制电路板(PCB)的布局文件导入到诸如 Ansys 这类场求解器工具中进行分析。

结合设计探索的 PDN 阻抗分析

这种分析方法难度更高,有时会通过电路模型来开展。但遗憾的是,电路模型无法准确反映 PDN 阻抗的实际特性,因此通常需要借助场求解器来确定设计中的 Z 参数、S 参数或其他网络参数。场求解器还可用于计算 PDN 的阻抗谱,随后通过傅里叶逆变换得到冲激响应函数。这是一个相当复杂的设计探索主题,值得单独撰写指南进行详细说明;但当你开始处理开关速度极快、同时核心电压低且噪声容限严格的元件时,这种分析方法就变得至关重要。

额外去耦电容的选择

一旦通过场求解器提取出 PDN 模型,你就能识别出 PDN 阻抗谱中哪些频段的阻抗较高,进而选择额外的去耦电容,针对性地抑制 PDN 阻抗谱中的这些峰值。添加自谐振频率与 PDN 阻抗峰值频段重叠的电容(见下文),并持续并联添加电容,直至 PDN 阻抗降至目标阻抗以下。若你不确定 PDN 所需的目标阻抗,可阅读 Kella Knack 撰写的这篇文章,以明确所需的目标阻抗值。此外,我也将准备一篇新文章,介绍如何直接计算该目标阻抗。

(说明:1. 文中 “field solver” 译为 “场求解器”,“post-layout simulations” 译为 “布局后仿真”,“noise margins” 译为 “噪声容限” 等,均为电子工程领域标准术语;2. 单位符号 “nF(纳法)”“ns(纳秒)”“V(伏)” 保留原文,符合技术文档表述规范;3. “Z-parameters”“S-parameters” 为网络参数标准符号,采用行业通用译法 “Z 参数”“S 参数”,同时保留原文符号以确保准确性。)

示例阻抗谱

只要去耦电容的自谐振频率与电源分配网络(PDN)的两个高阻抗(high-Z)峰值频率相匹配,就可将其添加到 PDN 中,以针对性抑制这两个高阻抗峰值。将多个电容并联,可平缓这些峰值的边缘,还有助于降低 PDN 的整体阻抗。

如今的电路板需满足更低功耗、更高数据速率与更严格噪声要求,因此每位设计师都应配备必要的工具,用于印制电路板(PCB)的旁路电容与去耦电容的计算、选型及布局。而仅 Altium Designer(奥腾设计软件) 能为你提供所需的原理图设计与布局工具,助力你完成各类应用场景的全新设计。此外,Altium Designer 的仿真工具套件还可帮助你识别电源完整性问题,并分析电源网络的瞬态特性。

关于 Altium Designer 在 Altium 365 平台上的更多功能,我们目前仅介绍了冰山一角。若你想深入了解去耦电容值的计算方法,可联系我们的专业技术人员,或立即开启 Altium Designer + Altium 365 的免费试用。

(说明:1. 专业术语 “high-Z” 译为 “高阻抗”,“power integrity” 译为 “电源完整性”,符合电子设计领域通用表述;2. 软件名称 “Altium Designer”“Altium 365” 为专有名称,保留原文并补充 “奥腾设计软件” 作为中文常用译法,便于理解;3. “bypassing capacitor” 译为 “旁路电容”,与 “decoupling capacitor(去耦电容)” 明确区分,避免混淆。)

案例

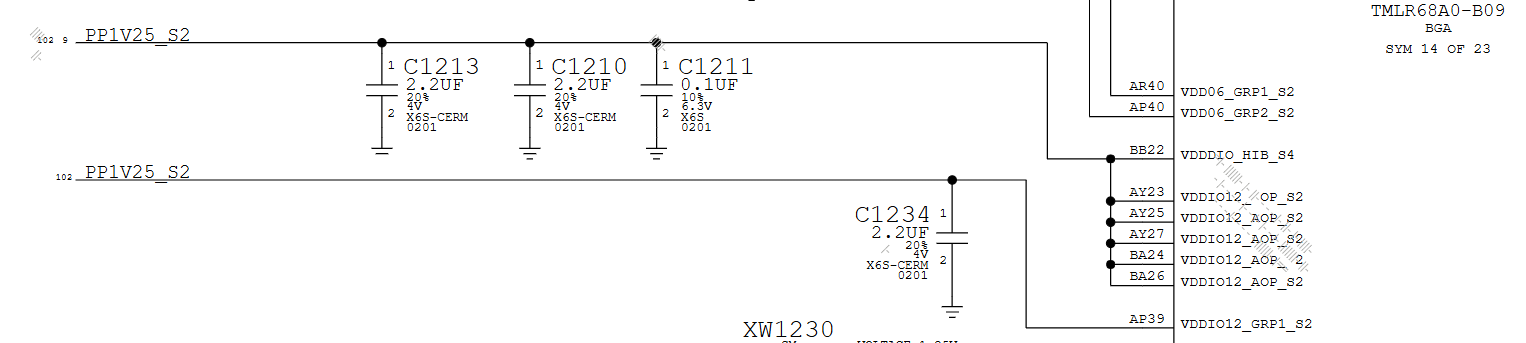

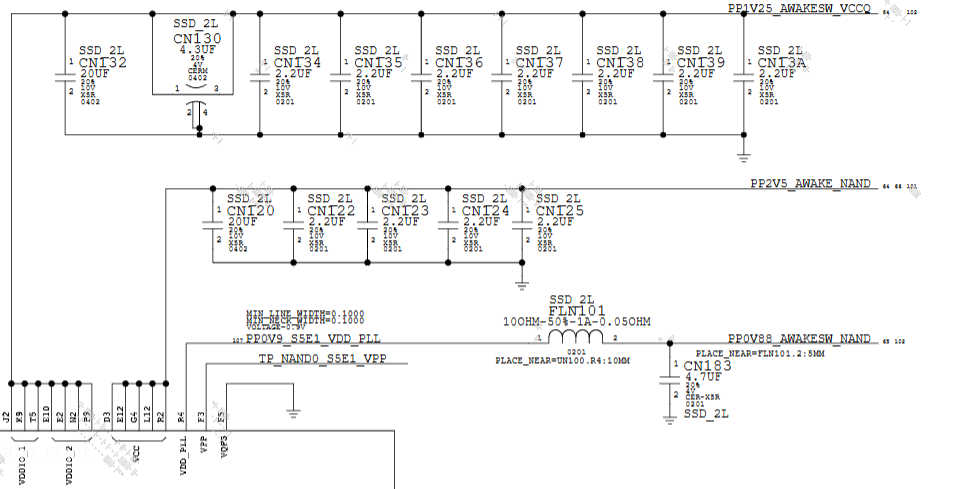

Apple macbook

参考:

https://flexpcb.org/decoupling-capacitor-value-determining-the-circuit-capacitance-for-signal-stabilization/

https://resources.altium.com/p/what-size-decoupling-capacitor-should-i-use-my-digital-ics#understanding-the-equivalent-capacitor-model

3648

3648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?