摘 要:针对激光扫描共聚焦显微镜的大视场、高分辨率需求,为在振镜扫描的时间内获取更多数据量,设计一种基

于 FPGA 的高速数据采集系统。该系统采用 Xilinx 的 A7 系列 FPGA 作为主控芯片,同时选用 TI 公司提供的

LMK0482X系列时钟发生器和一款支持JESD204B协议的单通道14位高速ADC14X250芯片共同组成信号采集系统。

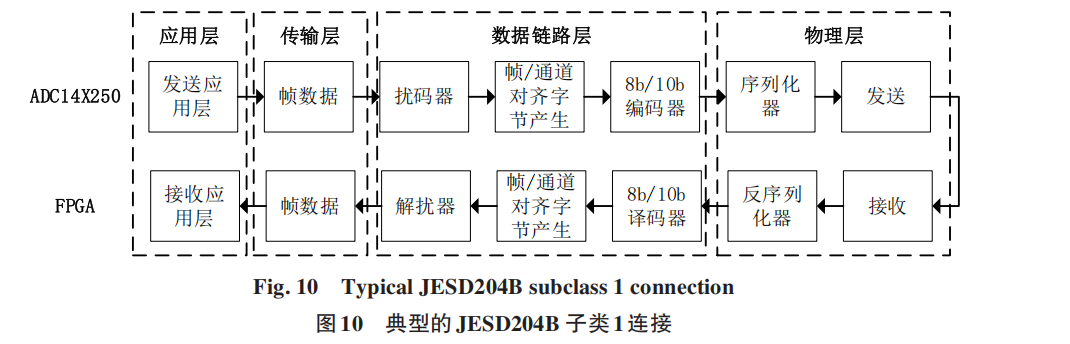

系统使用Verilog硬件描述语言在Vivado平台下实现各模块功能,通过SPI协议完成LMK0482X和ADC14X250芯片的

寄存器配置,利用Xilinx提供的JESD204B IP核构建基于AXI协议的高速串行数据链路,实现ADC与FPGA之间高效

的数据采集传输。实验结果表明,在 5 Gbps的传输速率下,接口可以正确接收与解析数据,系统的采样速率可达到

250 Mbps,数据采样精度为14 bit,符合激光扫描共聚焦成像仪器的数据采集要求。

0 引言

近年来随着共聚焦显微成像技术的迅速发展,其在生

物医学、材料科学等领域的应用越来越广泛[1-3]。由 Ra‐

jadhyaksha等[4]实现了100~1 000 um×100~1 000 um视场的

共聚焦扫描系统,图像帧率可达到每秒 30 帧,但是由于数

据采集速率的限制,每帧的采样点数较少,导致图像分辨

率不高。国内对于激光扫描共聚焦显微成像技术的研究

起步较晚,但也有一些高校、研究所参与研究并取得了一

定成果。如胡茂海等[5]将检流式与共振式光学扫描镜相

结合,采用凌华公司生产的9812采集卡,实现了4 M/s的采

样率,理论最高采集速度可达到 20 M/s。然而,传统的数

据采集方法往往受限于硬件性能和数据采集速率,无法满

足当下对于实时、高分辨率、多维度数据获取的迫切需求。

在本文所述的共聚焦扫描成像系统中,采样率是由二

维振镜的 X 轴速度和过采样率决定的。对于重构一帧

850 pixel×850 pixel 的图像,同时在配合扫描的二维振镜 X

轴频率为 29.3 KHz 的条件下,每个像素点进行 5 倍过采

样。经计算,数据采集系统的采样速率应达到 250 MHz。

因此,本文设计了一种可以配合激光扫描共聚焦成像数据

的高速采集与处理系统,采用支持 JESD204B 串行协议的

模数转换芯片替代传统的并行 LVDS 接口,以实现数据的

采集转换功能。该接口具有更快的转换速率,且引脚数量

少,可实现更小的封装、更短的布线以及更低的成本[6-7]。

系统采用 Xilinx 的 A7 系列 FPGA(Field Programmable Gate

Array)为主控芯片,通过一片采样率为 250 Mbps、数据精

度为 14 bit 的 ADC 芯片实现信号采集。该 ADC 芯片内部

采用基于serdes的JESD204B接口进行数据传输,其数据瞬

时传输速率高达5 Gbps。同时,系统时钟通过LMK系列的

时钟管理芯片进行分配,以确保时钟信号同源以及各芯片

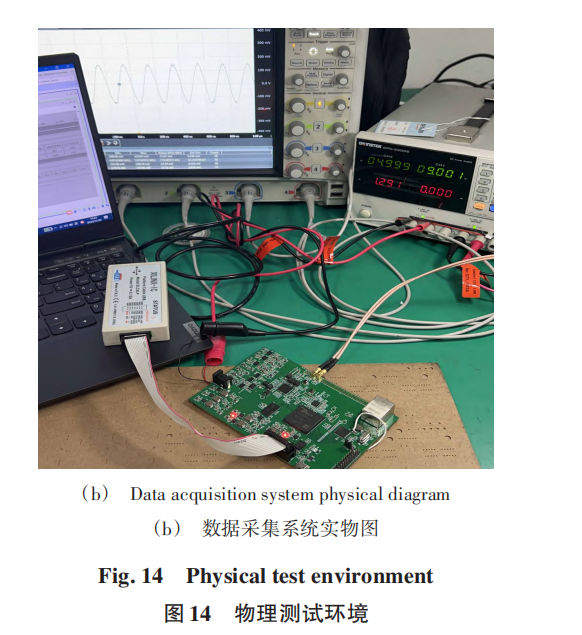

间的时钟同步,从而保证数据采集传输质量。测试实验结

果表明,系统功能的实现准确无误,较传统的数据采集系

统采样率大幅提升,对于实现激光扫描共聚焦大视场、高

分辨率成像可起到关键作用。

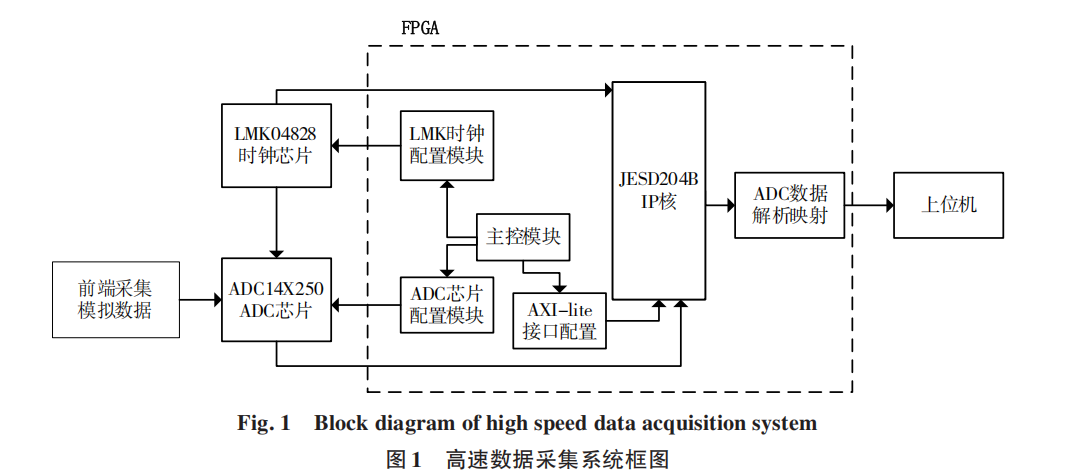

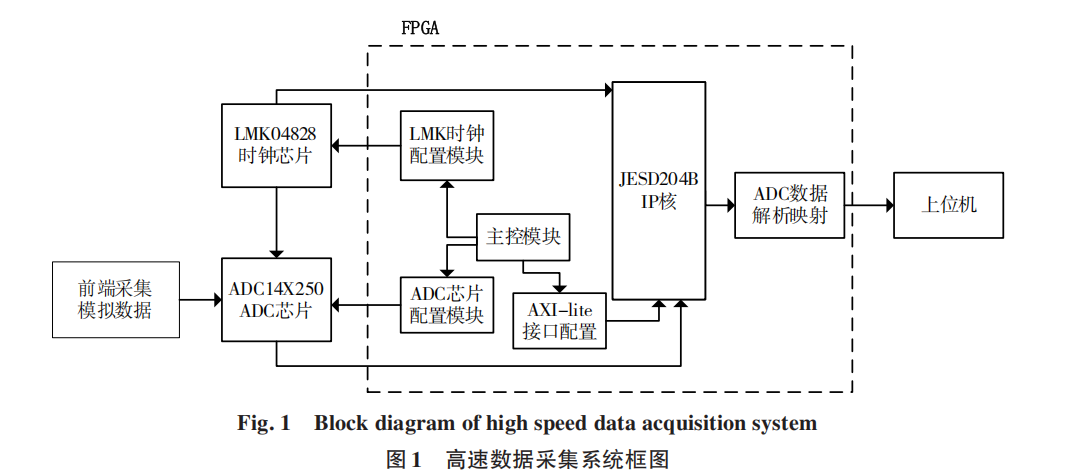

1 系统方案设计

本系统设计以 Xilinx Vivado 软件为开发平台,其中主

控芯片采用 Xilinx Artix-7 系列的现场可编程门阵列(FP‐

GA)。该芯片提供了高性能的功耗比架构和 GTP 高速收

发器,能够支持 JESD204B 协议接口完成高速模数转换器

(Analog to Digital Converter,ADC)的驱动采集。硬件电路

包括 ADC 转换电路、时钟产生电路、电源电路以及外围电

路等。软件部分通过 FPGA 硬件描述语言 Verilog 编程实

现系统功能,包括时钟芯片配置模块、高速ADC控制模块、

数据解析映射模块和系统主控模块。系统总体设计结构

框图如图1所示。

本系统采集的数据由模拟前置电路产生差分信号进

入 ADC 芯片,ADC 将模拟信号转变为数字信号,通过

JESD204B 协议将数据传送到 FPGA 中,其中涉及 ADC 的

配置以及数据的解析映射。时钟产生模块主要负责为

JESD204B 链路传输的 TX 与 RX 端提供相应的高速时钟;

系 统 主 控 模 块 负 责 各 模 块 间 的 标 志 位 传 递 ,通 过

JESD204B 接口逻辑完成数字信号的接收与处理,将数据

传送至上位机完成数据的高速采集。

2 硬件设计

2.1 时钟芯片模块

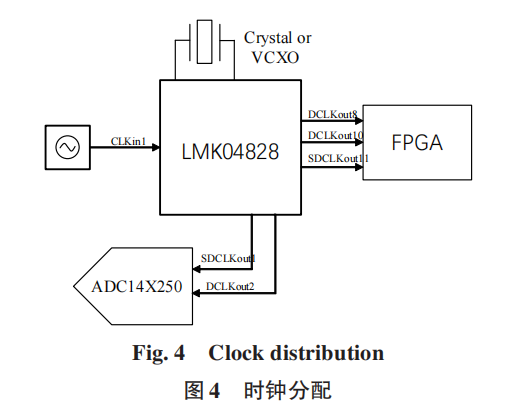

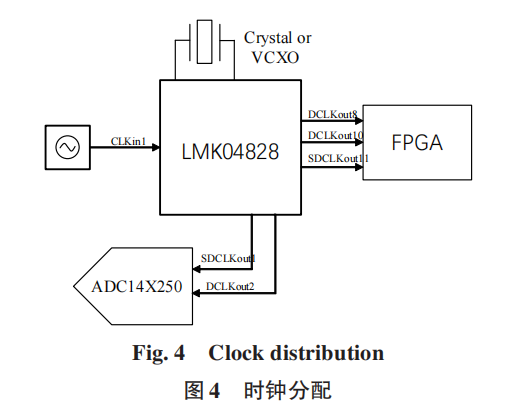

对于 JESD204B 协议下的高速 ADC 数据采集系统,其

对模数转换器件的采样时钟和数据链路的传输时钟要求

较高,通常需要精密的时钟芯片提供时钟源[8]。本系统采

用 TI公司专为 JESD204B接口设计的 LMK0482X系列时钟

芯片作为该模块的核心电路,该芯片内部采用双锁相环结

构,可生成超低抖动、具有射频采样能力的时钟,同时具备

简化系统的功能[9-10]。

时钟芯片产生电路如图 2 所示。该芯片的供电电压

为 3.3 V,PLL 的基准时钟由 SiT910 晶振产生,并输入至

CLKIN0、CLKIN1、OSCin 3 个引脚,通过 SPI 协议对芯片进

行配置,使 DCLKout 引脚产生多路同源时钟,并分别向

ADC 与 FPGA 提供设备时钟(Device Clock)与同步时钟

(SYSREF Clock)。同时,SDCLKout引脚输出 SYSREF 同步

信号,以实现数据链路的时钟对齐。在系统设计中,该时

钟芯片共产生 5 路差分时钟,差分走线通过接入 100 Ω 电

阻进行阻抗匹配。CPout1 引脚在外部时钟源失效时产生

高电平使能备用晶振,以维持芯片继续工作。

信迈提供ARM+FPGA+ADC的精密、高速数据采集系统设计方案。

744

744

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?