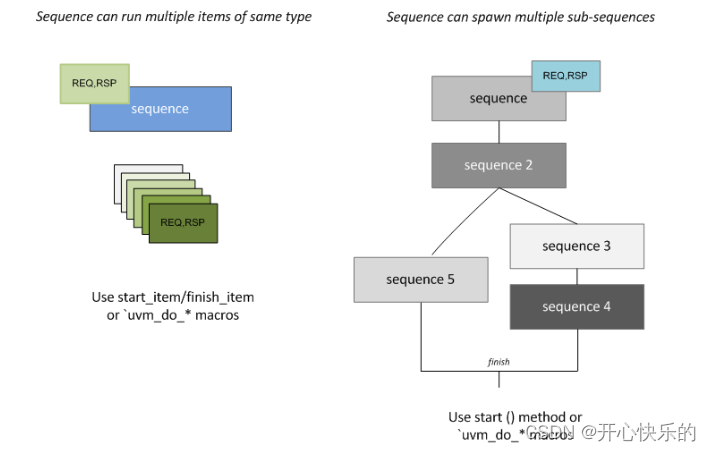

Sequences can do operations on sequence items, or kick-off new sub-subsequences:

1.Execute using the start() method of a sequence or ‘uvm_do macros

2.Execute sequence items via start_item/finish_itemor 'uvm_do macros

'uvm_do macros will identify if the argument is a sequence or sequence_item and will call start() or start_item() accordingly.

ln this page, we'll try to execute a sequence item using the start_item/finish_item task.In order to create a user-definedsequence :

1. Derive from uvm_sequence base class with a specified data object type

2.Register the seque

本文档介绍了System Verilog和UVM中sequence的基础知识,包括使用start()方法和'uvm_do宏执行sequence及sequence item,强调了start_item/finish_item任务的应用。内容涵盖自定义sequence的创建步骤,如继承uvm_sequence基类,注册工厂,指定默认sequencer,并在body()任务中编写主要激励。此外,讨论了在VIP和自定义环境中如何通过多层sequence模拟协议层次,特别是将寄存器操作转换为总线item的重要性。

本文档介绍了System Verilog和UVM中sequence的基础知识,包括使用start()方法和'uvm_do宏执行sequence及sequence item,强调了start_item/finish_item任务的应用。内容涵盖自定义sequence的创建步骤,如继承uvm_sequence基类,注册工厂,指定默认sequencer,并在body()任务中编写主要激励。此外,讨论了在VIP和自定义环境中如何通过多层sequence模拟协议层次,特别是将寄存器操作转换为总线item的重要性。

订阅专栏 解锁全文

订阅专栏 解锁全文

1510

1510

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?