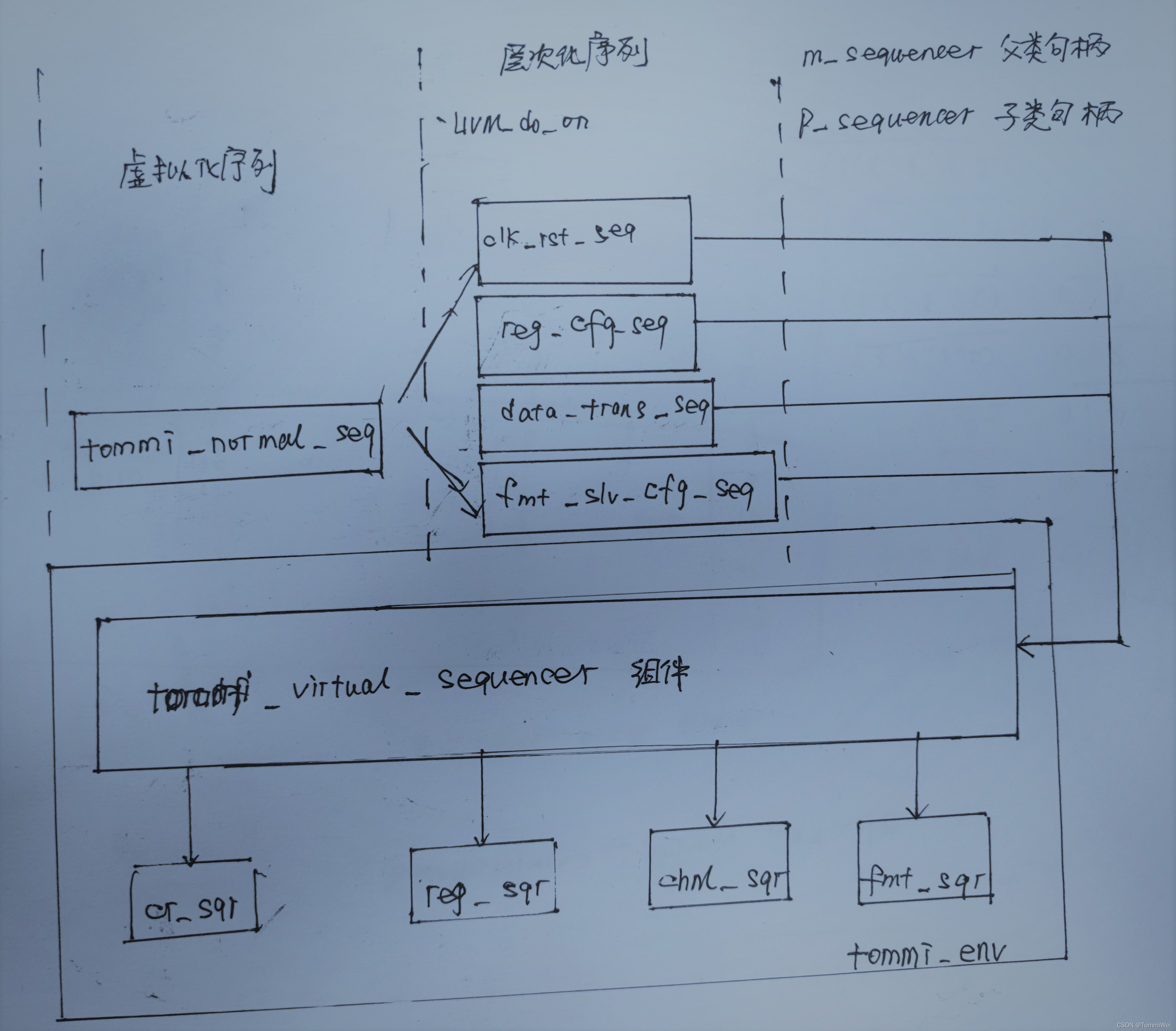

squence的层次化

揭开virtual sequence的神秘面纱

- virtual sequence可以承载不同目标sequencer的sequence群落

- virtual sequence是一个链接所有底层sequencer句柄的地方

- uvm用户需要在顶层的connect阶段,做好virtual sequencer中各个sequencer句柄与底层sequencer实体对象的一一对接,避免句柄悬空。

//*********************************************************************//

// virtual sequence //

//需要区分virtual sequencer 同其它底层负责传送数据对象的sequencer //

//在virtual sequence中记得使用宏

本文介绍了System Verilog中的virtual sequence概念,它用于管理不同目标sequencer的sequence集合。virtual sequence作为链接底层sequencer的纽带,需要在uvm connect阶段正确配置。文章列举了多个在top_env_seq_lib文件中的sequence示例,并强调了如何将它们挂载到virtual sequencer上。通过比喻sequence是货车,sequencer是公路收费站,解释了sequence如何在body()中启动并传递激励。文章还提醒读者注意p_sequencer的使用和connect函数的重要性。最后,作者鼓励读者交流学习并提供联系邮箱。

本文介绍了System Verilog中的virtual sequence概念,它用于管理不同目标sequencer的sequence集合。virtual sequence作为链接底层sequencer的纽带,需要在uvm connect阶段正确配置。文章列举了多个在top_env_seq_lib文件中的sequence示例,并强调了如何将它们挂载到virtual sequencer上。通过比喻sequence是货车,sequencer是公路收费站,解释了sequence如何在body()中启动并传递激励。文章还提醒读者注意p_sequencer的使用和connect函数的重要性。最后,作者鼓励读者交流学习并提供联系邮箱。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?