AXI学习记录(2)------AXI地址传输结构介绍

文章目录

前言

上一篇文章AXI学习记录(1)------AXI握手规则介绍中介绍完了AXI握手规则,接下来看看AXI传输事务相关内容,先介绍地址传输结构。

1 地址传输结构

由于AXI是基于Burst传输,即在一次传输中会传输多个数据。那么问题来了,传输多个数据的话,那肯定得有多个地址,这些地址如何确认呢?

首先,得有一个Start_Address吧,在这基础上,AXI协议中定义了Burst Length、Burst Size和Burst Type来确认Burst Address,下面就来分别介绍这些都是什么玩意。

1.1 Burst Length

按照Spec中所说,一次Burst传输会有一次至多次Transfers(表示一次Burst传输数据的总次数),Burst Length就表示传输Transfers的数量。在地址传输中,使用AW/RLEN[7:0]来分别表示写/读地址通道Burst Length。

根据AXI版本的不同,Burst Length会有一定的区别,如下:

- AXI3中,对于所有的Burst Type都只支持1-16 Transfers,很明显,4bits就够了。

- AXI4中,对于INCR Burst Type,支持1-256 Transfers,这样就要8bits(在这种情况下,要注意与AXI3的兼容性。要么减小Burst Length;要么将一个长的Burst改成一堆短的Burst拼起来,具体怎么操作还不知道,需要继续学习);其余的Burst Type则和AXI3一样。没看到特意说AXI5有什么区别,那就认为和AXI4一样即可。

对于Burst Length还有一些规则需要遵守:

- 对于Burst Type为WRAP 的情况,Burst Length只能是2/4/8/16。

- 每次Burst传输累计地址不能跨越4kb的地址边界。-----这是什么原因?

- Burst一旦发生,不能提前终止,必须保持传输完成。那应该怎么处理呢?------写的话使用write strobes这种机制(个人理解就是对写入地址进行Mask);读的话将不需要的数据丢弃,那我怎么知道丢掉哪些数据,后面会解释。

注意:对于FIFO这种东西,你要是多读了,那你再把这次读不需要数据丢弃,就会丢数据。因此读FIFO就别瞎读,要读多少就读多少,确保需要的Transfers对应Burst Length。

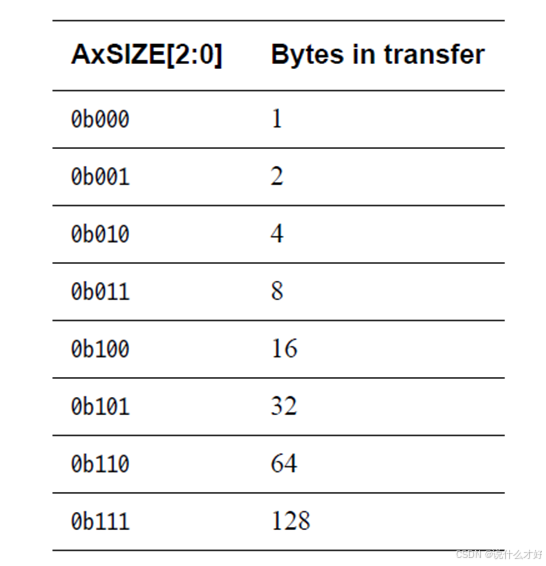

1.2 Burst Size

Burst Size指的就是每个Data Transfer(也叫Beat或者拍)的数据位宽(最大Bytes),在传输过程中,数据位宽不能大于AXI总线位宽(例如AXI是64bits,那你传128bits,这种情况怎么办?------目前暂时不清楚。。。)。

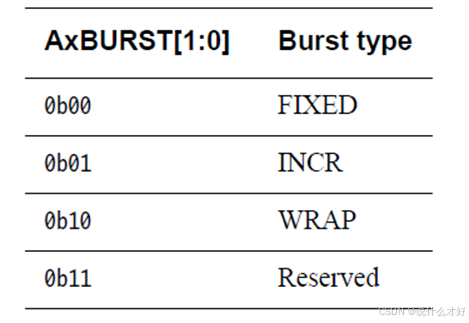

1.3 Burst Type

Burst Type表示AXI Burst传输类型。AXI包含3种Burst Type,下面将对这3种Type分别介绍。

- FIXED

这种类型中所有数据传输都使用同一个Address(即Start Address),适用于读写FIFO。 - INCR

这种类型表示数据传输地址是递增的,即从Start Address开始递增,每次递增的大小是Burst Size,一共递增Burst Length次。常用于RAM读写操作。 - WRAP

这种类型表示数据传递地址是环绕的,即开始是递增,但是到了最大边界时重新回到边界地址。Spec中说该种类型常用于Cache line accesses,暂时还没了解到。。。

这里会有个问题,最小地址和最大地址怎么确认?------下面介绍了怎么计算WRAP上/下界限。

2 Burst Address计算

既然要有计算,那么先定义一些变量,如下表所示:

| Signal Name | Description |

|---|---|

| Start_Address | Burst传输起始地址 |

| Number_Bytes | 每个Data Transfer中数据最大Bytes |

| Data_Bus_Bytes | AXI数据总线位宽,例如64bits数据总线该值为8(64/8=8bytes) |

| Aligned_Address | 起始地址的对齐状态 |

| Burst_Length | 一次Burst传输中数据总传输次数 |

| Address_N | 一次Burst传输中第N个传输的地址 |

| Wrap_Boundary | 一次Wrap Type Burst的最低地址(下界限) |

| Lower_Byte_Lane | 传输最低寻址地址的Byte通道 |

| Upper_Byte_Lane | 传输最高寻址地址的Byte通道 |

| INT | 向下取整 |

如何计算一次Burst传输地址:

- Start_Addess = ADDR,个人理解ADDR作为起始地址输入。

- Number_Bytes = 2 S I Z E 2^{SIZE} 2SIZE,个人理解SIZE就是前面讲的Burst_Size。

- Burst_Length = LEN + 1,LEN就是前面讲的AW/RLEN[7:0]。

- Aligned_Address = (INT(Start_Addess / Number_Bytes) × Number_Bytes,Aligned_Address用来判断传输是否对齐,如果Start_Addess = Aligned_Address则表示对齐传输。

例如:Start_Addess=0x07,Number_Bytes=4,则Aligned_Address=0x04,此时Start_Addess不等于Aligned_Address,表示非对齐传输。如何处理?通过STRB信号处理(数据传输结构相关内容中介绍)。

Burst传输中第一个地址:

- Addess_1 = Start_Addess。

对于INCR和WRAP(没有到WRAP上界限时) Type方式的Burst传输,第N(N不等于1)个地址:

- Addess_N = Aligned_Address + (N - 1) × Number_Bytes。

在WRAP Type Burst中,Wrap_Boundary可以用来表示WRAP下界限:

- Wrap_Boundary = (INT(Start_Addess / (Number_Bytes × Burst_Length))) × (Number_Bytes × Burst_Length)。

- 如果Addess_N = Wrap_Boundary + (Number_Bytes × Burst_Length),此时说明地址已经到了WRAP上界限,则将地址回绕到Wrap_Boundary。地址继续增加则使用Address_N = Start_Address + ((N – 1) × Number_Bytes) – (Number_Bytes × Burst_Length)来计算。

例如:Start_Addess = 0x38,Burst_Length = 4,Number_Bytes = 4(即SIZE=2^4=16),此时:

- Wrap_Boundary = (INT(0x38 / (4 × 4))) × (4 × 4) = INT(56 / 16) × 16 = 3 × 16 = 48 = 0x30

- Wrap上界限 = 0x30 + 0d16 = 0x40

- Addess_1 = 0x38,Addess_2 = 0x3C,Addess_3 = 0x40(到了WRAP上界限,实际地址为0x30),Addess_4 = 0x34(因为Addess_3实际为0x30)。

接着介绍一下Lower_Byte_Lane和Upper_Byte_Lane,Lower_Byte_Lane表示每Beat传输数据最低存放位置,Upper_Byte_Lane表示每Beat传输数据最高存放位置,这两个参数共同决定了每Beat数据在数据总线中的有效范围。

例如:假设数据总线为64bits,其中Lower_Byte_Lane = 2,Upper_Byte_Lane = 5,即表示每Beat数据从XDATA[23:16]开始存放,到XDATA[47:40]结束。

一个Burst传输中第一个传输使用哪个字节通道:

- Lower_Byte_Lane = Start_Address - (INT(Start_Address / Data_Bus_Bytes)) × Data_Bus_Bytes。

- Upper_Byte_Lane = Aligned_Address + (Number_Bytes – 1) – (INT(Start_Address / Data_Bus_Bytes)) × Data_Bus_Bytes

一个Burst传输中第N个传输(N不等于1)使用哪个字节通道:

- Lower_Byte_Lane = Address_N – (INT(Address_N / Data_Bus_Bytes)) × Data_Bus_Bytes

- Upper_Byte_Lane = Lower_Byte_Lane + Number_Bytes – 1

总结

本文简单介绍了AXI地址传输结构,不好的地方就是第2章节介绍的非常乱(目前这部分内容大概率有误),这部分内容和数据传输结构相关,我会尽快学习后续内容并更新。

AXI地址传输结构介绍与计算

AXI地址传输结构介绍与计算

8201

8201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?