最近在做TDC的时候算是把时序稍微了解了一下,也明白了时序报告里建立松弛(WNS)和保持松弛(WHS)的概念和计算过程,这里分享一下,也欢迎大家一起交流。

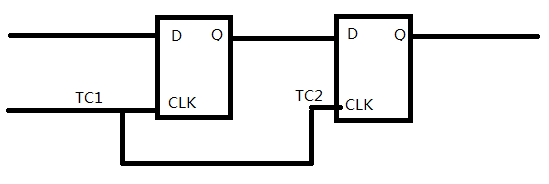

这里的建立松弛和保持松弛都是在FPGA内部的触发器之间的关系,并没有考虑到外部的输入输出延时。一般的模型为如下:

建立松弛指的是,在下一次时钟触发脉冲来时,第一级触发器输出数据到建立时间前之间的时间最大为多少,这个一般用来确定时钟最大的工作频率。

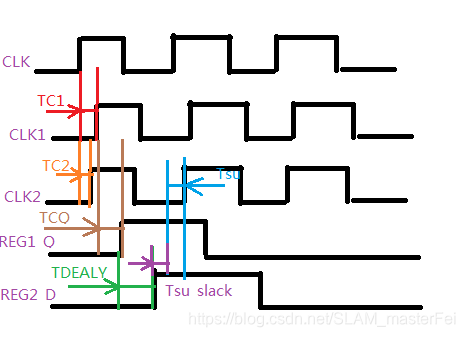

一个典型的二级触发器时序如上图所示,CLK为主时钟,CLK1为考虑走线延时的第一级触发器时钟,CLK2为考虑走线延时的第二级触发器时钟,他们相对于主时钟的延时分别是TC1和TC2,RGG1_Q为触发器的数据输出,经过了传播延时TCO,RGE2_D为第二级触发器的D端,经过了走线延时T_DELAY,Tsu为建立时间,Tsu_slack为建立松弛。所以很容易发现建立松弛直接决定了时钟的最大工作频率。

那么计算过程很简单,有如下关系:Tsu_slack=(TC2+T(一个时钟周期)-Tsu)-(TC1+TCO+T_DELAY)。对应于FPGA的时序报告如下:

本文深入探讨FPGA内部触发器间的时序关系,解析建立松弛(WNS)和保持松弛(WHS)概念及其计算方法,阐述其对时钟频率的影响,适合对FPGA及时序分析感兴趣的读者。

本文深入探讨FPGA内部触发器间的时序关系,解析建立松弛(WNS)和保持松弛(WHS)概念及其计算方法,阐述其对时钟频率的影响,适合对FPGA及时序分析感兴趣的读者。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5336

5336