今天刷题,偶然接触到generate用法,小结如下:

generate可以用来构成循环语句,但是必须要定义genvar作为循环变量

结尾必须接上endgenerate

generate定义for循环时,必须要加类似如下形式

for(i=0;i<n;i=i+1)

begin: label

...

...

end

label是你自己定义的标签,可以理解为c++中的实例化哈哈哈,我瞎说的

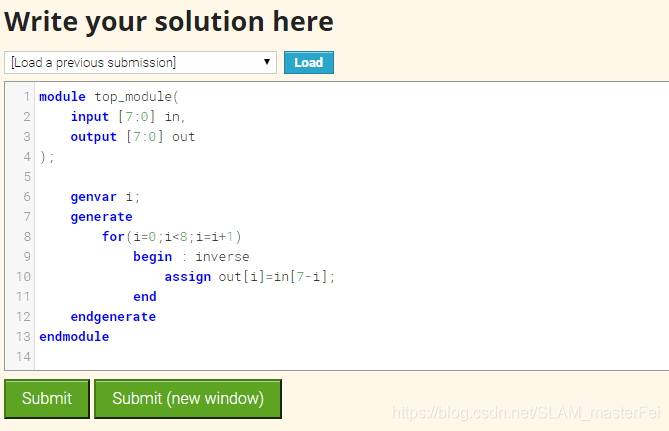

那么这样的语句是可综合的,就拿下面这题来说

verilog代码如下:

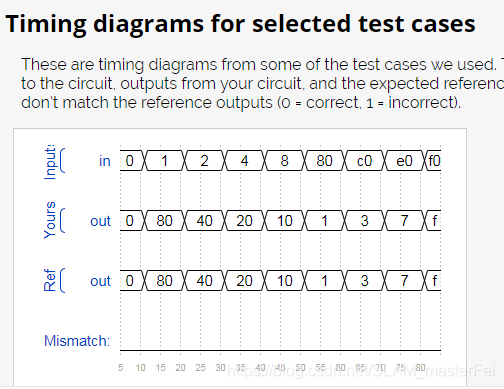

看结果

注意这里是16进制哈是不是很方便完成位交换了呢。。。

本文深入探讨Verilog中generate语句的使用方法,包括如何定义循环语句、必要组件genvar及endgenerate的使用,同时讲解了generate语句在for循环中的应用,并通过实例展示了其在位交换操作中的便利性。

本文深入探讨Verilog中generate语句的使用方法,包括如何定义循环语句、必要组件genvar及endgenerate的使用,同时讲解了generate语句在for循环中的应用,并通过实例展示了其在位交换操作中的便利性。

1503

1503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?