代码

module test (

input wire clk, // 外部时钟输入

input wire rst, // 外部复位输入

output wire [31:0] result, // 计算结果

output wire locked, // 锁定信号

output wire outclk_0, // PLL 输出时钟0

output wire outclk_1 // PLL 输出时钟1

);

// 实例化 PLL 模块

my_pll pll_inst (

.inclk0(clk), // 外部时钟输入

.areset(rst), // 外部复位输入

.c0(outclk_0), // PLL 输出时钟0

.c1(outclk_1), // PLL 输出时钟1

.locked(locked) // PLL 锁定信号

);

// 声明浮点数输入(在 initial 块中赋初值)

reg [31:0] floatA, floatB;

wire [31:0] result_reg; // 结果寄存器

// 实例化处理模块,将 PLL 输出时钟连接到处理模块的 clk 输入

processingElement pe_inst (

.clk(outclk_0), // 连接 PLL 输出时钟0

.reset(rst), // 外部复位信号

.floatA(floatA), // 输入浮点数 A

.floatB(floatB), // 输入浮点数 B

.result(result_reg) // 计算结果

);

// 将 result_reg 的值连接到顶层输出

assign result = result_reg;

// 初始化 floatA 和 floatB

initial begin

floatA = 32'h3F800000; // 浮点数 A 初始化为 1.0 (IEEE 754 格式)

floatB = 32'h3F800000; // 浮点数 B 初始化为 1.0 (IEEE 754 格式)

end

endmodule

约束

方式一:

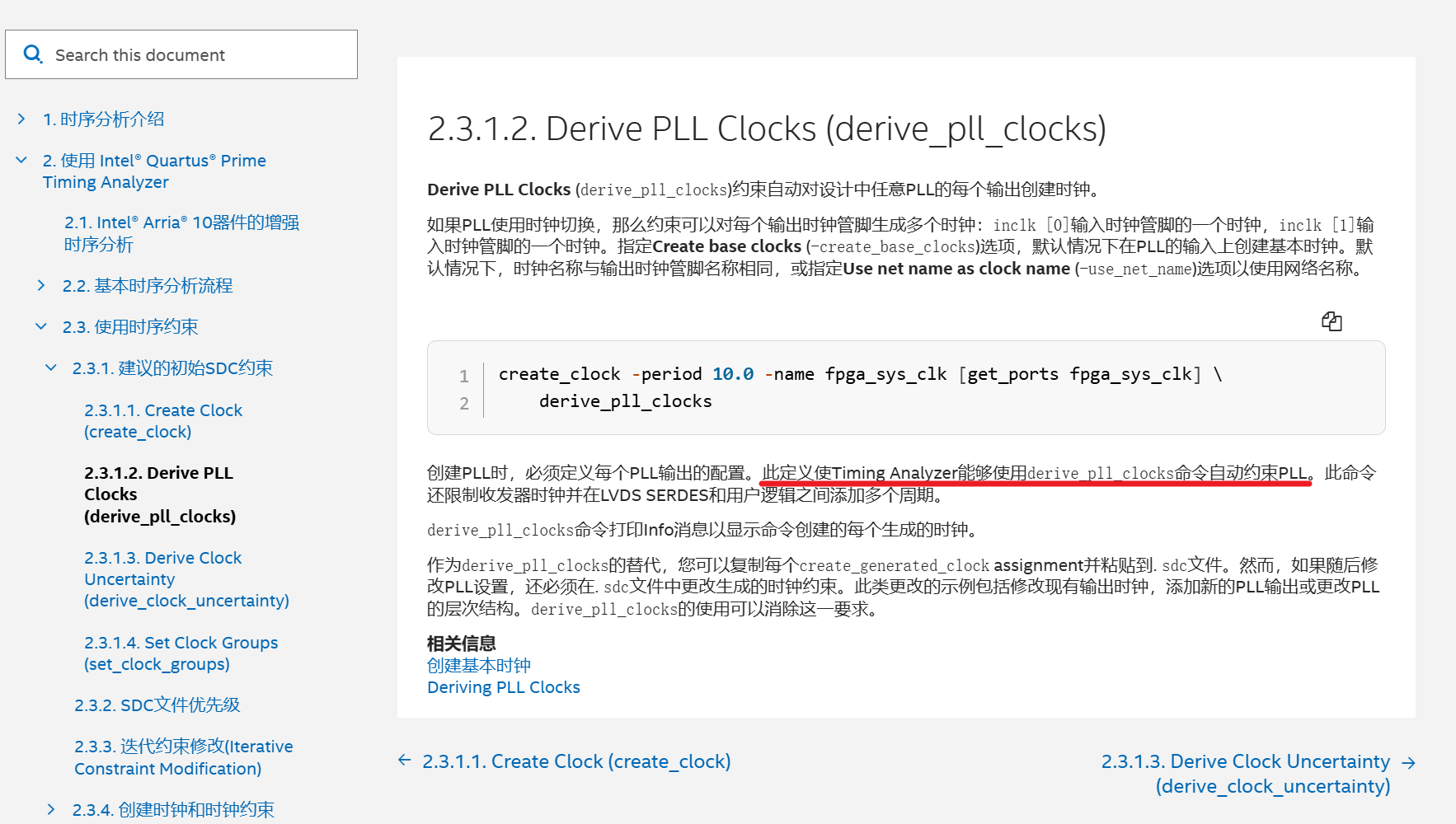

- 带有derive_pll_clocks的约束示例

# https://www.intel.cn/content/www/cn/zh/docs/programmable/683143/19-3/design-constraint-sdc-files.html

## PROGRAM "Quartus Prime"

## VERSION "Version 17.1.0 Internal Build 91 05/07/2017 SJ Pro Edition"

## DATE "Wed May 10 14:22:08 2017"

##

## DEVICE "10AX115R4F40I3SG"

##

#**************************************************************

# Time Information

#**************************************************************

set_time_format -unit ns -decimal_places 3

#**************************************************************

# Create Clock

#**************************************************************

create_clock -name {clk_in} -period 10.000 -waveform { 0.000 5.000 } [get_ports {clk_in}]

#**************************************************************

# Create Generated Clock

#**************************************************************

derive_pll_clocks

#**************************************************************

# Set Clock Uncertainty

#**************************************************************

derive_clock_uncertainty

#**************************************************************

# Set Input Delay

#**************************************************************

set_input_delay -add_delay -clock [get_clocks {clk_in}] 1.500 [get_ports {async_rst}]

set_input_delay -add_delay -clock [get_clocks {clk_in}] 1.200 [get_ports {data_in}]

#**************************************************************

# Set Output Delay

#**************************************************************

set_output_delay -add_delay -clock [get_clocks {clk_in}] 2.000 [get_ports {data_out}]

#**************************************************************

# Set Multicycle Path

#**************************************************************

set_multicycle_path -setup -end -from [get_keepers *] -to [get_keepers {reg2}] 2

- 官方对于

derive_pll_clocks的说明:

方式二:

生成的SDC 文件

#**************************************************************

# Create Clock

#**************************************************************

create_clock -name {clk1} -period 20.000 -waveform { 0.000 10.000 } [get_ports {clk}]

#**************************************************************

# Create Generated Clock 生成的时序约束

#**************************************************************

#create_generated_clock -name {pll1} -source [get_pins {pll_inst|altpll_component|auto_generated|pll1|inclk[0]}] -multiply_by 2 -master_clock {clk1} [get_pins {pll_inst|altpll_component|auto_generated|wire_pll1_clk[1]~clkctrl|outclk}]

create_generated_clock -name {pll_inst|altpll_component|auto_generated|pll1|clk[0]} -source [get_pins {pll_inst|altpll_component|auto_generated|pll1|inclk[0]}] -duty_cycle 50/1 -multiply_by 2 -master_clock {clk1} [get_pins {pll_inst|altpll_component|auto_generated|pll1|clk[0]}]

create_generated_clock -name {pll_inst|altpll_component|auto_generated|pll1|clk[1]} -source [get_pins {pll_inst|altpll_component|auto_generated|pll1|inclk[0]}] -duty_cycle 50/1 -multiply_by 1 -divide_by 2 -master_clock {clk1} [get_pins {pll_inst|altpll_component|auto_generated|pll1|clk[1]}]

- 当代码如下时,无需约束。系统生成的默认derive_pll_clocks约束为空,一些项目(EP2C5T144C8N Fmax60多M,只有主时钟和分组约束)也没有添加手动约束。

- 如不需要再加PLL输出时钟的约束,也不需要输入类似ALTERA的derive_pll_clocks目命令,和FAE确认过,可以直接传递相关约束信息。所述。

module test (

input wire clk, // 外部时钟输入

input wire rst, // 外部复位输入

output wire [31:0] result, // 计算结果

output wire locked, // 锁定信号

);

wire outclk_0, // PLL 输出时钟0

wire outclk_1 // PLL 输出时钟1

// 实例化 PLL 模块

my_pll pll_inst (

.inclk0(clk), // 外部时钟输入

.areset(rst), // 外部复位输入

.c0(outclk_0), // PLL 输出时钟0

.c1(outclk_1), // PLL 输出时钟1

.locked(locked) // PLL 锁定信号

);

// 声明浮点数输入(在 initial 块中赋初值)

reg [31:0] floatA, floatB;

wire [31:0] result_reg; // 结果寄存器

// 实例化处理模块,将 PLL 输出时钟连接到处理模块的 clk 输入

processingElement pe_inst (

.clk(outclk_0), // 连接 PLL 输出时钟0

.reset(rst), // 外部复位信号

.floatA(floatA), // 输入浮点数 A

.floatB(floatB), // 输入浮点数 B

.result(result_reg) // 计算结果

);

// 将 result_reg 的值连接到顶层输出

assign result = result_reg;

// 初始化 floatA 和 floatB

initial begin

floatA = 32'h3F800000; // 浮点数 A 初始化为 1.0 (IEEE 754 格式)

floatB = 32'h3F800000; // 浮点数 B 初始化为 1.0 (IEEE 754 格式)

end

endmodule

CG

- https://www.intel.com/content/www/us/en/docs/programmable/683432/22-1/tcl_pkg_sdc_ver_1-5_cmd_create_generated_clock.html

1万+

1万+